# Real-Time Power Loss Optimized Operation of a Solid State Transformer by Utilizing the Common-Mode Voltage

Tobias Merz, Nikolas Menger, Max-Emanuel Siegemund, Rüdiger Schwendemann, Marc Hiller

## ► To cite this version:

Tobias Merz, Nikolas Menger, Max-Emanuel Siegemund, Rüdiger Schwendemann, Marc Hiller. Real-Time Power Loss Optimized Operation of a Solid State Transformer by Utilizing the Common-Mode Voltage. The 26th European Conference on Power Electronics and Applications, GDR SEEDS France & EPE Association, Mar 2025, Paris, France. 10.34746/epc2025-0027 . hal-05074047

HAL Id: hal-05074047

<https://utc.hal.science/hal-05074047v1>

Submitted on 19 May 2025

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Distributed under a Creative Commons Attribution 4.0 International License

# Real-Time Power Loss Optimized Operation of a Solid State Transformer by Utilizing the Common-Mode Voltage

Tobias Merz, Nikolas Menger, Max-Emanuel Siegemund,

Rüdiger Schwendemann, Marc Hiller

Elektrotechnisches Institut (ETI)

Karlsruhe Institute of Technology (KIT)

Kaiserstr. 12

Karlsruhe, Germany

Tel.: +49 (0)721 608-48264

E-Mail: [tobias.merz@kit.edu](mailto:tobias.merz@kit.edu)

URL: [www.eti.kit.edu](http://www.eti.kit.edu)

**Index Terms**—Analytical loss computation, Cascaded H-Bridge, Dual Active Bridge Converter, Solid-State Transformer

**Abstract**—This article presents a general methodology and a real-time solvable, analytical model for reducing the total losses of the cells of a Solid-State Transformer (SST). The efficiency is increased with the usage of the online optimized common-mode voltage  $u_{CM}$ . Measurements on a 400V<sub>AC</sub> to 750V<sub>DC</sub>, 45kW SST test bench verify the calculation results and the operating principle of the algorithm. A loss reduction of up to 20% is possible without introducing additional restrictions to the SST.

## I. INTRODUCTION

For use as a medium voltage (MV) alternating current (AC) to low voltage (LV) direct current (DC) grid coupling, the Solid-State Transformer (SST) offers significant potential and advantages. These include controlled active and reactive power flow, higher volumetric and gravimetric power density, fewer inverter stages, and active filtering of grid harmonics compared to a conventional low-frequency transformer (LFT) with an additional inverter stage [1]. However, a major drawback of SST is its lower efficiency compared to LFT [2]. To address this limitation, extensive research has focused on reducing the efficiency gap while enhancing existing benefits and overall SST design, including its lifetime [3]. A common topology for connecting a MV AC grid to an LV DC microgrid is the input serial output parallel (ISOP) structure, built with similar power modules. These modules supply energy on either the MV or LV side, depending on the power flow direction. The Dual Active Bridge (DAB) is often used as a galvanically

isolating power transmission stage. First introduced in [4], it has since been extensively studied and improved. Its main advantages are high dynamic performance, zero voltage switching (ZVS) capability, and controllable bidirectional power flow. Improving the efficiency of the DABs, and thus the sub-modules, directly enhances the overall efficiency of the SST [5]–[7]. While traditional methods focus on improving the modulation scheme or upgrading hardware, this publication explores a different approach using a degree of freedom inherent in the three-phase system of an SST. Starting from a basic loss function derived from a single DAB, a mathematical loss model is developed for the phases and the entire SST. By applying various common-mode (CM) voltages  $u_{cm}$  to this model, the system's power losses for the next operation point (OP) can be predicted. This approach enables significant real-time reduction of total system losses.

In Section II of this paper, the topology and the key components of the investigated system are described. In Section III, the analysis is presented in several steps. First, Section III-A discusses the measured power losses of a single DAB module, showing its loss behavior. Next, Section III-B introduces a cost function for the entire SST, combining losses from all modules. Section III-C explains how the CM voltage  $u_{cm}$  can be adjusted to reduce total power losses. In Section III-D, a mathematical optimization method is used to minimize power losses by changing  $u_{cm}$ . Finally, Section IV presents calculated and experimental results, confirming the accuracy and effectiveness of the proposed optimization method.

## II. TOPOLOGY

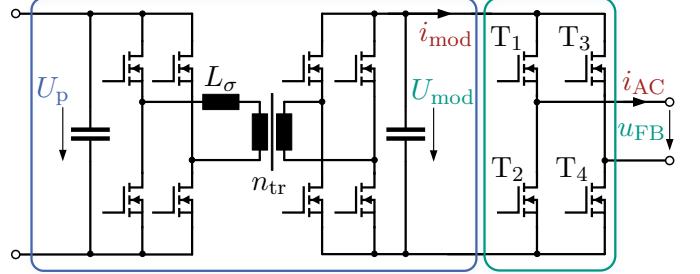

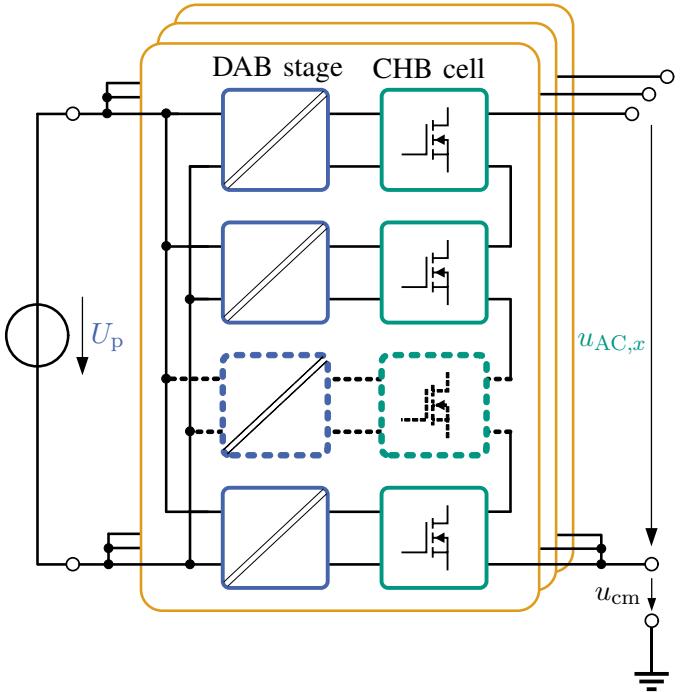

The investigated topology is a three-phase modular Cascaded H-Bridge (CHB)-based SST in a star connection, with each cell individually powered by a galvanically isolated DAB. A single power module, consisting of a CHB cell and a DAB stage, is illustrated in Fig. 1. The DAB, highlighted in blue, enables unrestricted bidirectional power flow and operates at unity gain in this study. The CHB cell, highlighted in green, generates the AC output of each power module. The overall topology of the prototype is depicted in Fig. 2. The DAB stages are connected in parallel and are powered by a bidirectional DC voltage source with an output voltage of  $U_p$ . The converter's AC output voltages  $u_{AC,x}$ , where  $x \in \{U, V, W\}$ , are produced by a series connection of the CHB cells. Depending on the switching state of the four MOSFETs  $T_1$  to  $T_4$ , the CHB cell provides three discrete voltage levels  $u_{FB} \in \{+U_{mod}, -U_{mod}, 0 \text{ V}\}$ . Each SST phase operates using voltage shifted pulse width modulation (VSPWM) with one switching module per phase. In general the current CM voltage  $u_{cm}$  is calculated as shown in (1). The voltage between the phase and the neutral point of the converter is defined as  $u_{AC,x,sp}$ .

$$u_{cm} = \frac{1}{3} \cdot \sum_x u_{AC,x,sp} \quad (1)$$

To enhance voltage utilization of the converter, a triangular-shaped CM voltage  $u_{cm,tri}$  is added to the voltage setpoints of the controller. This triangular CM voltage setpoint is calculated as shown in (2). This degree of freedom is further leveraged by the proposed algorithm described in the following sections. In this publication, the harmonic content of the output voltage is not analyzed in detail. This simplification is justified, as the SST operates as a multilevel converter with many voltage levels per phase and an assumed switching frequency in the kilohertz range. More details on reducing the harmonics is described in [8], [9], for example. In addition, the DAB is set up to transfer enough power to neglect a voltage ripple of the DC link capacitors, and no special voltage suppression method needs to be implemented as in [10].

$$u_{cm,tri} = -\frac{\min(u_{AC,UVW}) + \max(u_{AC,UVW})}{2} \quad (2)$$

The switching states with the resulting output voltages  $u_{FB}$  and the module current  $i_{mod}$  in dependence of the phase current  $i_{AC}$  of the CHB cell is shown in Table I.

Fig. 1: Power module with DAB stage for power supply (blue) and CHB cell output stage (green).

Fig. 2: Three phase modular ISOP SST for AC/DC grid coupling. The dotted module means that there can be several modules.

TABLE I

Switching states of the CHB cell

| State    | Conducting | Output voltage<br>$u_{FB}$ | Module current |           |

|----------|------------|----------------------------|----------------|-----------|

|          |            |                            | $i_{AC}$       | $i_{mod}$ |

| Positive | $T_1, T_4$ | $U_{mod}$                  | $i_{AC}$       |           |

| Negative | $T_2, T_3$ | $-U_{mod}$                 | $-i_{AC}$      |           |

| Bypass 1 | $T_1, T_3$ | 0 V                        | 0 A            |           |

| Bypass 2 | $T_2, T_4$ | 0 V                        | 0 A            |           |

### III. PROPOSED OPTIMIZED OPERATION MODE

The proposed power loss-optimized operation mode of the SST aims to reduce overall power losses by considering the individual losses of each DAB at the current OP. Therefore, a mathematical model is developed to analytically describe the power losses of each DAB (Section III-A). Using this model, the power losses of each phase and the entire SST can be predicted based on the current operating conditions (Section III-B). The total losses are then minimized by adjusting the CM voltage  $u_{cm}$ , which serves as a degree of freedom in the system (Section III-D). A key requirement when applying the proposed method is ensuring that the setpoints of the superimposed current controller remain unaffected. This is achieved by maintaining the relevant line-to-line voltages of the SST unchanged, even when the CM voltage  $u_{CM}$  is modified.

#### A. Power losses of a single DAB

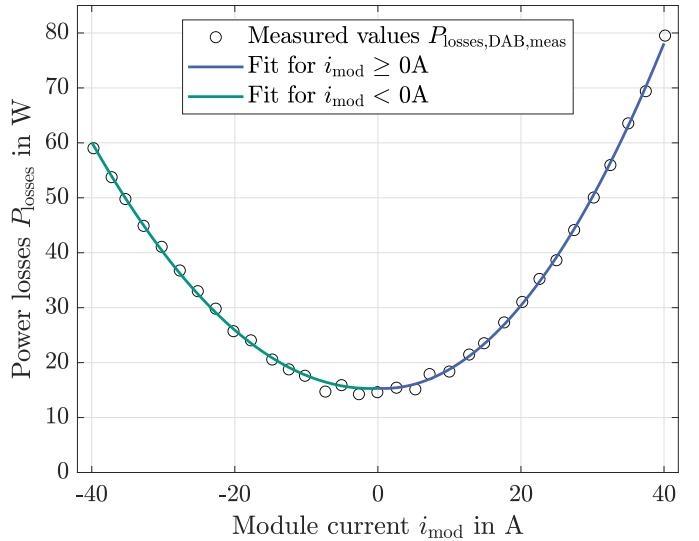

Firstly, the power losses of the DAB stage of a power module operating at unity gain (cf. the blue box in Fig. 1) are measured using a power meter with fixed primary and secondary voltages  $U_p$  and  $U_{mod}$ . The measured losses are fitted to a function based on the module current  $i_{mod}$ . Ohmic losses of the CHB cell are not included, assuming that two of the four semiconductors ( $T_1$  to  $T_4$ ) always conduct the phase current  $i_{AC,x}$ , as shown in Table I. Furthermore, it is assumed that the switching losses of the CHB cells remain within the same range as they would without the proposed method. Figure 3 shows the measured power losses  $P_{losses,meas}$  (black circles). The results reveal an asymmetry between positive and negative module currents. This asymmetry arises from different voltage levels on the primary and secondary sides, leading to varying semiconductor switching behavior. More hardware details are provided in Section IV.

Secondly, to obtain an analytical description of power losses as a function of the module current  $i_{mod}$ , the measurement results are used for curve fitting. Due to the observed asymmetry, two separate functions are employed: one for positive output power ( $i_{mod} \geq 0$  A) and another for negative output power ( $i_{mod} < 0$  A). Since lower-order polynomials are easier to handle and capture the primary loss contributions — quadratic for copper losses, linear for switching losses, and constant for transformer core losses under fixed switching frequency and voltages [11] — a quadratic function is chosen, as shown in (3). If sufficient computational power is available, higher-order

**Fig. 3:** Measured and fitted power losses of a DAB with  $U_p = 750$  V and  $U_{mod} = 53.2$  V.

polynomials or other function types could be used for more precise real-time optimization.

$$P_{losses,DAB}(i_{mod}) = p_{2,k} \cdot i_{mod}^2 + p_{1,k} \cdot i_{mod} + p_{0,k} \quad (3)$$

Thirdly, the variables  $p_{n,k}$  serve as fitting parameters, where  $n \in \{2, 1, 0\}$  represents the coefficients for the quadratic, linear, and constant terms of the loss function. The index  $k \in \{\text{pos, neg}\}$  indicates whether the power flow within a module is positive or negative, respectively. This distinction ensures an accurate representation of the asymmetric power loss behavior observed during the measurements.

Fourthly, due to physical considerations, it is reasonable that the power losses for very small positive and negative currents, close to 0 A, should be similar. This leads to a constant offset and an intersection of the curves, creating a continuous function that may not be continuously differentiable. Consequently,  $p_{0,\text{pos}} = p_{0,\text{neg}} = p_0$ . The results of the fitting parameters for the investigated scaled prototype are shown in Section IV.

#### B. Mathematical model of SST phase losses caused by the DABs

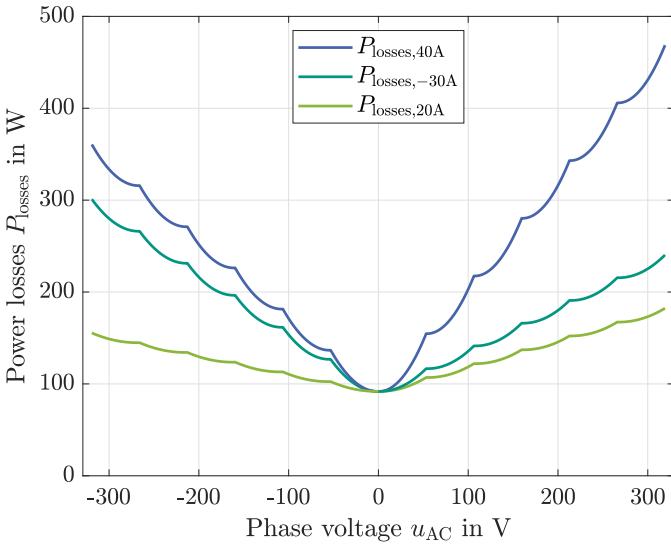

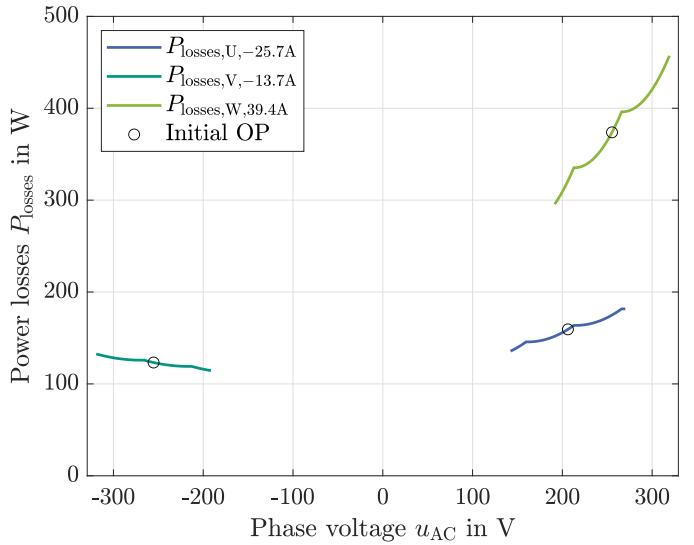

The fitted power loss curves of a single DAB are combined into an analytical power loss model for a single phase of the SST, depending on the number of modules per phase,  $m_{ph}$ . Figure 4 illustrates the phase power losses as a function of different phase currents  $i_{AC}$ . As mentioned earlier, each phase operates with VSPWM. In this mode, only one module is actively

**Fig. 4:** Calculated power losses of a single phase with six modules for different phase currents and voltages.

switching, while the other modules are either in bypass or in an active state (i.e., positive or negative) to achieve the phase voltage setpoints  $u_{AC,x,sp}$  of the overlaid controller as accurately as possible.

The number of modules in a phase in an active state is an integer value and denoted by  $a_{fix,x}$ , where  $a_{fix,x} \in \mathbb{Z}$  and  $-m_{ph} \leq a_{fix,x} \leq m_{ph}$ . Each DAB stage of a module in a positive state must deliver the corresponding phase current ( $i_{mod} = i_{AC}$ ) to maintain a constant module voltage  $U_{mod}$ . Modules in a negative switching state have to supply the negative phase current ( $i_{mod} = -i_{AC}$ ). Modules in bypass state do not transmit any power in this control cycle ( $i_{mod} = 0$  A). The DAB stage of the switching module supplies a portion of the phase current ( $i_{mod} = a_{dc} \cdot i_{AC}$ ), determined by the duty cycle  $a_{dc,x}$  with  $-1 \leq a_{dc,x} \leq +1$ , which is derived from the voltage setpoint of the current controller.

It is evident that smaller phase voltages and currents result in lower phase losses. However, phase currents are not a degree of freedom, as they are defined by the superimposed controller and the grid. The resulting mathematical loss model of a single phase is shown in (4).

$$\begin{aligned}

P_{losses,x}(a_{fix,x}, a_{dc,x}, m_{ph}, i_{AC,x}) = & \\

p_{2,k} \cdot (|a_{fix,x}| + a_{dc,x}^2) \cdot i_{AC,x}^2 + & \\

p_{1,k} \cdot (a_{fix,x} + a_{dc,x}) \cdot i_{AC,x} + & \\

p_0 \cdot m_{ph} & \quad (4)

\end{aligned}$$

Combining (4) for each phase and considering that the change in CM voltage  $u_{cm}$  changes  $a_{fix,x}$  and  $a_{dc,x}$

**Fig. 5:** Calculated power losses of each phase for a specific OP and residual voltage modification range ( $\hat{u}_{AC} = 325$  V,  $\hat{i}_{AC} = 40$  A,  $\varphi = 65^\circ$ ,  $\omega t = 25^\circ$ ).

as shown in (5) and (6) for each phase  $x$  leads to (7). The function 'trunc' is a truncation which means rounding to the next integer in the direction of zero.

$$a_{fix,x}(u_{cm}) = \text{trunc} \left( \frac{u_{AC,x,sp} + u_{cm}}{U_{mod}} \right) \quad (5)$$

$$a_{dc,x}(u_{cm}) = \frac{u_{AC,x,sp} + u_{cm}}{U_{mod}} - a_{fix,x}(u_{cm}) \quad (6)$$

$$P_{losses,\text{total}}(u_{cm}) = \sum_x P_{losses,x}(u_{cm}) \quad (7)$$

### C. Using the common-mode voltage for optimization

Since the investigated SST is a three-phase system in a star connection, it inherently offers the opportunity to use the CM voltage  $u_{cm}$  for various objectives. Primarily, the CM voltage is typically used to increase the maximum output voltage. However, because the SST does not always operate at its voltage limits, the residual voltage range of the combined phases can be utilized to reduce overall losses. This is achieved by operating more DABs at higher efficiency and fewer at less efficient OP.

Figure 5 illustrates an example OP with the setpoint for the triangular CM voltage at  $u_{cm} = 68.7$  V (black circles). When the CM voltage is modified, all three phase voltages shift in the same direction simultaneously to maintain the same line-to-line voltage. However, the losses in each phase change differently depending on the corresponding phase currents.

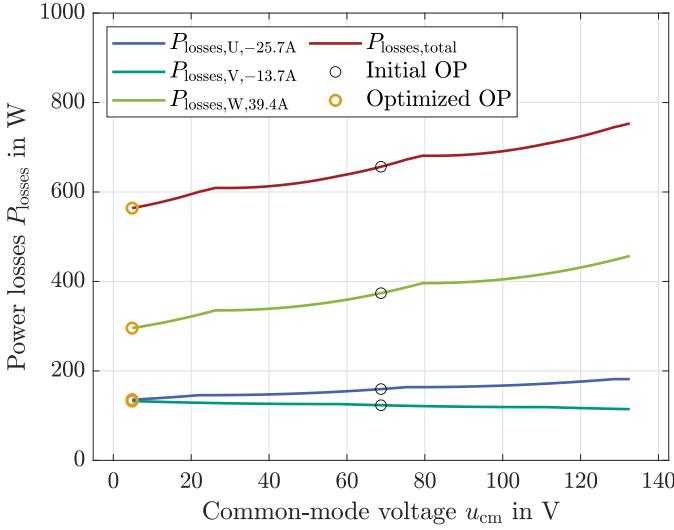

To highlight the potential for power loss modification, Fig. 6 shows the power losses of each phase as

**Fig. 6:** Losses within each phase and total DAB losses in relation to the residual CM voltage  $u_{\text{cm}}$  range.

a function of the permissible CM voltage  $u_{\text{cm}}$  range. Additionally, the sum of the phase losses  $P_{\text{losses},\text{total}}$  and the initial OP are displayed. It is evident that in this case, reducing the CM voltage  $u_{\text{cm}}$  also reduces the total power losses. Hence, the overall efficiency of the SST is increased.

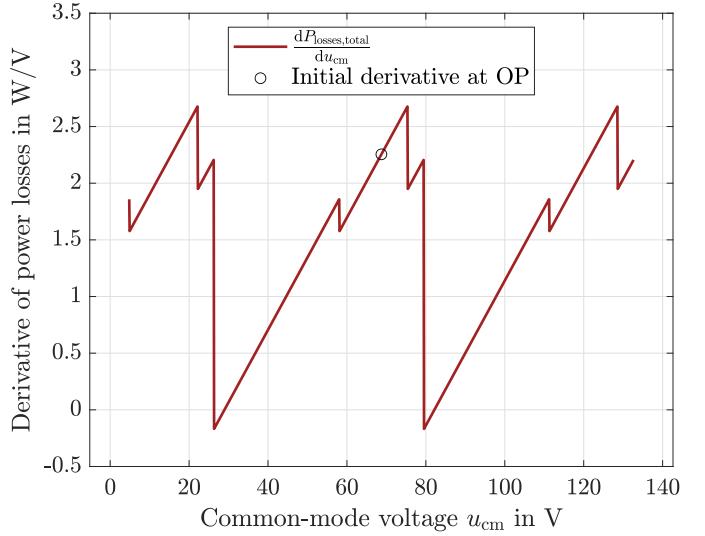

#### D. Minimizing the overall DAB power losses

Due to the mathematical power loss model of each phase, it is possible to solve this constrained, superimposed optimization problem analytically. Since the power losses are represented by polynomial fitting functions, calculating the local derivatives and setting them to zero to find local minima is simple. Solving (8) for  $u_{\text{cm}}$  leads to a local and potential global minimum. Given the constraints, the maximum and minimum common-mode voltages must also be tested to identify the global minimum. By evaluating this limited set of potential local minima with the predicted losses from (7), the global minimum of the power losses is determined and applied to the output of the SST phases.

$$\frac{dP_{\text{losses},\text{total}}}{du_{\text{cm}}} = \sum_x \frac{dP_{\text{losses},x}}{du_{\text{cm}}} = 0 \text{ W V}^{-1} \quad (8)$$

An upper bound of the amount of potential local minima  $B_{\text{opt}}$  can be calculated according to (9). It is proportional to the amount of modules per phase  $m_{\text{ph}}$ . The implementation has to be capable of calculating and comparing all of these  $B_{\text{opt}}$  potential local minima within one control cycle to be deterministic. However, in reality the absolute number of local minima is smaller, since the valid CM voltage range is reduced because of

**Fig. 7:** Derivative of total power losses  $\frac{dP_{\text{losses},\text{total}}}{du_{\text{cm}}}$  with respect to CM voltage  $u_{\text{cm}}$ .

the actual voltage setpoints of the superimposed current controllers.

$$B_{\text{opt}} = 3 \cdot (2m_{\text{ph}} + 1) \quad (9)$$

In Fig. 7 the overall derivative of the mentioned OP is shown, revealing two local minima. However, the global minimum is found at the minimal CM voltage  $u_{\text{cm}} \approx 4.8 \text{ V}$ . As a result, the power losses at this particular OP can be reduced from  $P_{\text{losses},\text{total},\text{old}} \approx 660 \text{ W}$  to  $P_{\text{losses},\text{total},\text{new}} \approx 566 \text{ W}$ . The optimized OP is highlighted with the orange circles in Fig. 6.

## IV. RESULTS

Both the calculated results and the measurements in the following subsections are generated with the system, described in Table II. The algorithm is implemented on an field-programmable gate array (FPGA) which operates with a frequency of  $f_{\text{FPGA}} = 150 \text{ MHz}$ . The algorithm is able to calculate the loss optimized common-mode voltage in real-time.

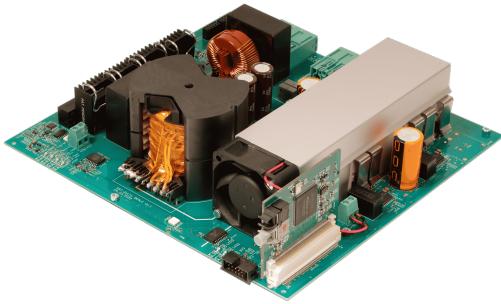

#### A. Hardware setup

Figure 8 shows a picture of a single power module of the SST. It consists of the DAB stage, the CHB cell, a plug-in FPGA controller board, and current, voltage, and temperature measurement systems. The control of the capacitor's voltage in each power module is managed by a simple PI-controller. The SST is controlled by a modular signal processing platform that incorporates two ARM-core processors and a high-performance FPGA [12]. The control structure of the SST as grid coupling between a 400 V AC and a 750 V DC grid is explained detail in [13].

**TABLE II**

System specification

| Parameter                       | Symbol                           | Value   |

|---------------------------------|----------------------------------|---------|

| Modules per phase               | $m_{\text{ph}}$                  | 6       |

| Module voltage                  | $U_{\text{mod}}$                 | 53.2 V  |

| Primary/ DC grid voltage        | $U_p$                            | 750 V   |

| Transformer winding ratio       | $n_{\text{tr}}$                  | 14.11:1 |

| DAB and CHB switching frequency | $f_{\text{DAB}}, f_{\text{CHB}}$ | 50 kHz  |

| Maximum phase current           | $I_{\text{AC},\text{max}}$       | 60 A    |

| Nominal power of DAB            | $P_{\text{DAB}}$                 | 2.5 kW  |

| Nominal power of SST            | $P_{\text{SST}}$                 | 45 kW   |

| System control frequency        | $f_{\text{sys}}$                 | 50 kHz  |

| AC grid voltage                 | $U_{\text{grid}}$                | 400 V   |

| Grid frequency                  | $f_{\text{grid}}$                | 50 Hz   |

| Grid filter                     | $L_{\text{filter}}$              | 1 mH    |

**Fig. 8:** Hardware of the power module with a DAB stage and the CHB cell.

### B. Calculation results

The results of the fitting process for the values shown in Fig. 3 are presented in Table III.

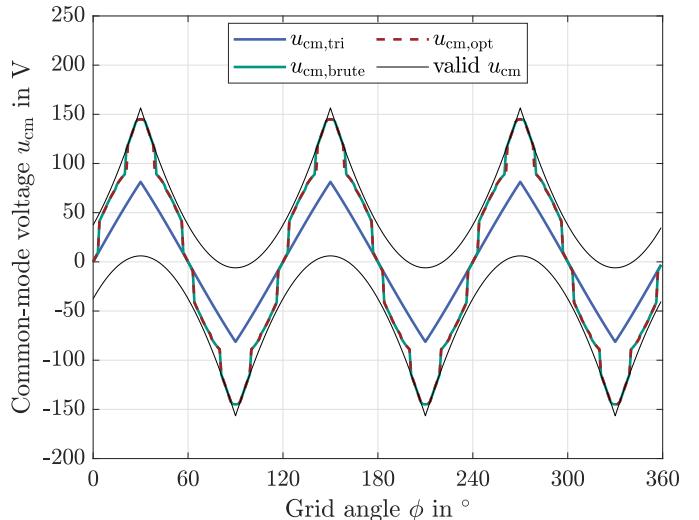

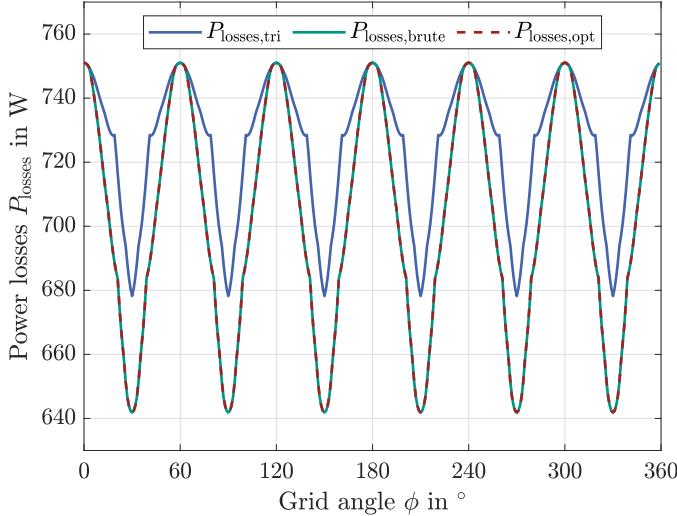

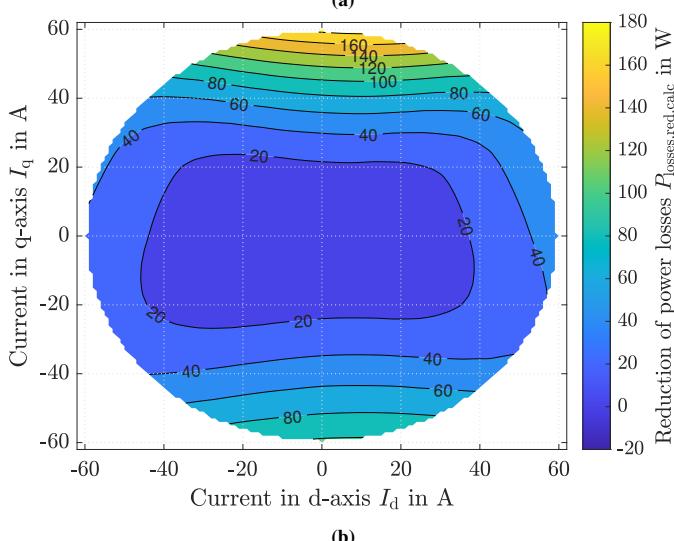

As a reference for the proposed optimization method, indicated with the index opt, the total losses  $P_{\text{losses},\text{total}}$  and the resulting CM voltage  $u_{\text{cm}}$  are compared to the modulation scheme with a maximized output voltage range (triangular shape), indicated by the index tri. It is important to note that the proposed method does not restrict the maximum output voltage. To verify the

**TABLE III**

Fitting parameters specification

| Parameter          | Value                     |

|--------------------|---------------------------|

| $p_{2,\text{pos}}$ | $40.8 \text{ mW A}^{-2}$  |

| $p_{1,\text{pos}}$ | $-61.9 \text{ mW A}^{-1}$ |

| $p_{2,\text{neg}}$ | $29.5 \text{ mW A}^{-2}$  |

| $p_{1,\text{neg}}$ | $60.4 \text{ mW A}^{-1}$  |

| $p_0$              | 15.3 W                    |

**Fig. 9:** Comparison of the valid CM voltage  $u_{\text{cm}}$  for a grid period.

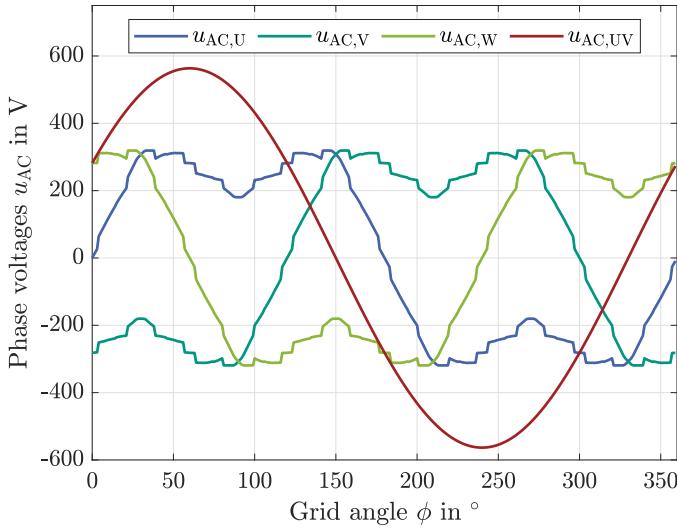

calculation results of the loss-optimized method, a time-consuming, not real-time capable brute-force algorithm is implemented in MATLAB, indicated by the index brute. The OP shown in the following figures (Fig. 9, Fig. 10 and Fig. 11) is  $\hat{U}_{\text{AC}} = 325 \text{ V}$ ,  $\hat{I}_{\text{AC}} = 40 \text{ A}$ ,  $\varphi = 0^\circ$ . Figure 9 shows that the analytical and the brute-force approach yield the same results, which differ from the triangular shape. The black lines indicate the minimum and maximum CM voltage range for this setup and grid voltages. It can be observed that the optimized CM voltage  $u_{\text{cm}}$  only matches the reference values at grid angles close to integer multiples of  $\omega t = 60^\circ$ . The resulting phase voltages of the converter are shown in Fig. 10. Although these phase voltages do not resemble a sinusoidal waveform, the resulting line-to-line voltage between two phases, which is relevant for controlling the sinusoidal currents, is sinusoidal and shown in red.

Fig. 11 shows the calculated power losses  $P_{\text{losses}}$  for the different calculation methods. It is evident that when the CM voltages  $u_{\text{CM}}$  are equal, the power losses are equal, too. Hence, the loss-optimized method achieves operating points that result in power losses equal to or lower than those of the reference method, with a reduction in losses occurring in most cases. Consequently, the overall efficiency of the DAB stages is improved. As a result of the optimization of each OP of the SST, the power losses over a full grid period are also reduced.

### C. Experimental results

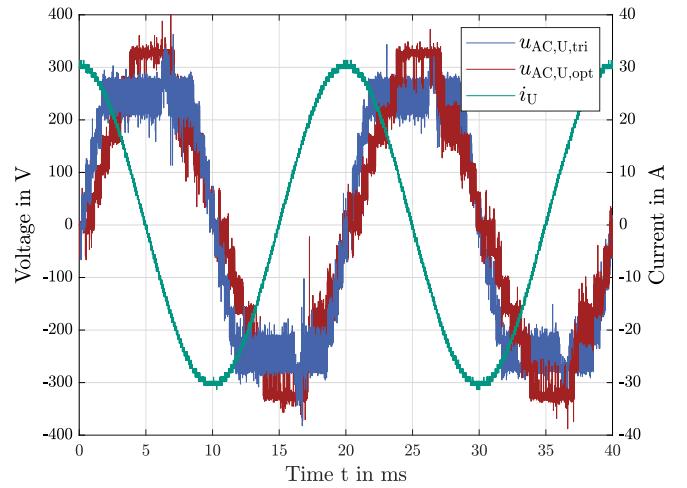

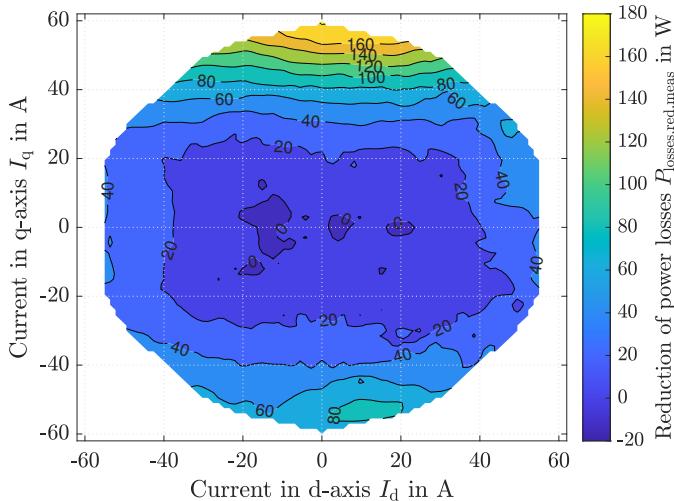

To evaluate the actual power loss reduction, measurements with different setpoint currents for  $I_d$  and  $I_q$  are conducted on the grid. As an example Fig. 12 shows the resulting voltage and current of phase U for

**Fig. 10:** Resulting calculated, switching period average SST output phase voltages with loss optimized CM voltage. Resulting sinusoidal line-to-line voltage  $u_{AC,UV}$  between phases U and V.

**Fig. 12:** Measured reference (blue) and optimized (red) voltage and current (green) of phase U with  $I_d = 0$  A and  $I_q = 30$  A.

**Fig. 11:** Comparison of the resulting losses  $P_{\text{losses}}$  during a grid period.

an OP of  $I_d = 0$  A and  $I_q = 30$  A. As previously mentioned, the phase current is not affected by the proposed scheme. However, due to the different CM voltage, the phase voltage takes on a different form. The loss reduction over the full operation range of the SST is shown in Fig. 13a. Additionally, a calculation with the same setpoints for voltages and currents is performed to compare the results and assess the accuracy of the model. The calculated results are presented in Fig. 13b. Both the measurements and the calculations show high accordance with a reduction in power losses of more than 160 W, even though the calculation does not consider harmonic voltages of the grid. However, there

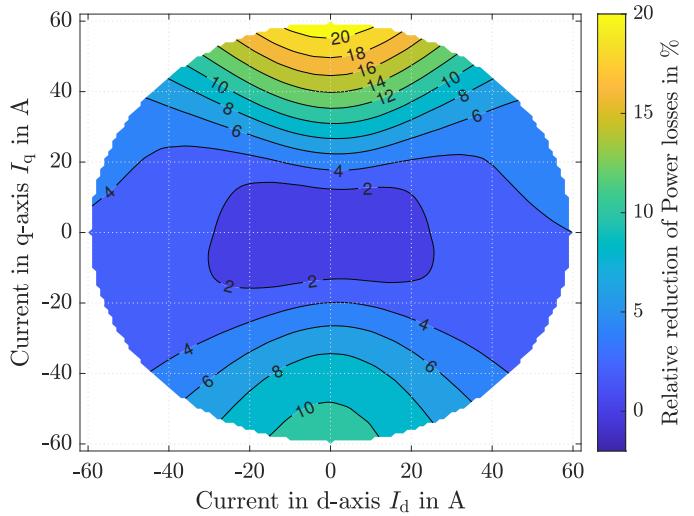

are some deviations at low current setpoints which can be caused by the accuracy of the measurement system. The reason for the asymmetric behavior with high positive and high negative currents in the q-direction is due to the effect of the voltage drop across the filter inductance  $L_{\text{filter}}$ . A positive q-current leads to a decrease in the required voltage in the d-direction, while a negative q-current increases the d-voltage setpoint. Due to this fact, less voltage is necessary to control the current, resulting in a wider range of valid values of the CM voltage  $u_{\text{CM}}$ . Figure 13 shows that the power losses of the DAB stages can be significantly reduced in nearly every OP. Figure 14 shows the relative reduction of the power losses for the calculation with a maximum relative reduction of 20 %.

## V. CONCLUSION

This paper presents a detailed approach to minimize the sum of power losses across all DAB modules of an SST, while being real-time capable. The approach is based on a mathematical model of the power losses for a single DAB module. After combining these into a model for a phase and then for the entire SST, it is used to estimate and minimize the total power losses of all 18 DAB modules by leveraging the residual degree of freedom in the CM voltage  $u_{\text{CM}}$  of the three-phase system. Calculations demonstrate the resulting CM voltage and the reduced losses of the entire converter by up to 20 %. Experiments validate these calculated results with high accuracy. Further research could explore alternative modulation schemes for the SST, generalize the approach for unscaled high-power DABs, optimize

(a)

(b)

**Fig. 13:** Reduction of (a) measured power losses  $P_{\text{losses,red,meas}} = P_{\text{losses,tri,meas}} - P_{\text{losses,opt,meas}}$  and (b) calculated power losses  $P_{\text{losses,red,calc}} = P_{\text{losses,tri,calc}} - P_{\text{losses,opt,calc}}$  at different OP for the loss optimized method in contrast to the reference.

the distribution of power transferred by the DABs, and incorporate the required redundancy of the SST.

**Fig. 14:** Calculated relative reduction of the losses of the DAB stages.

## REFERENCES

- [1] L. Ferreira Costa, G. De Carne, G. Buticchi, and M. Liserre, “The Smart Transformer: A solid-state transformer tailored to provide ancillary services to the distribution grid,” *IEEE Power Electronics Magazine*, vol. 4, no. 2, pp. 56–67, 2017.

- [2] J. E. Huber and J. W. Kolar, “Applicability of Solid-State Transformers in Today’s and Future Distribution Grids,” *IEEE Transactions on Smart Grid*, vol. 10, no. 1, pp. 317–326, 2019.

- [3] Y. Ko, V. Raveendran, M. Andresen, and M. Liserre, “Discontinuous Modulation based Power Routing for Modular Smart Transformers,” *2018 IEEE Energy Conversion Congress and Exposition, ECCE 2018*, pp. 1084–1090, 2018.

- [4] R. W. A. A. D. Doncker, D. M. Divan, and M. H. Kheraluwala, “A Three-Phase Soft-Switched High-Power-Density dc/dc Converter for High-Power Applications,” *IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS*, VOL. 27, NO. 1, JANUARY/FEBRUARY 1991 A, vol. 27, no. 1, p. 11, 1991.

- [5] M. A. Bahmani, T. Thiringer, A. Rabiei, and T. Abdulahovic, “Comparative Study of a Multi-MW High-Power Density DC Transformer with an Optimized High-Frequency Magnetics in All-DC Offshore Wind Farm,” *IEEE Transactions on Power Delivery*, vol. 31, no. 2, pp. 857–866, 2016.

- [6] T. Liu, Y. Xuan, X. Yang, P. Xu, Y. Li, L. Huang, and X. Hao, “Adaptive voltage control scheme for DAB based modular cascaded SST in PV application,” *2018 International Power Electronics Conference, IPEC-Niigata - ECCE Asia 2018*, pp. 1478–1483, 2018.

- [7] T. Liu, X. Yang, W. Chen, Y. Xuan, Y. Li, L. Huang, and X. Hao, “High-Efficiency Control Strategy for 10-kV/1-MW Solid-State Transformer in PV Application,” *IEEE Transactions on Power Electronics*, vol. 35, no. 11, pp. 11 770–11 782, 2020.

- [8] M. H. Mandol, S. P. Biswas, T. K. Roy, M. K. Hosain, and M. F. Kibria, “A Novel Modulation Scheme to Improve the Injected Power Quality for Modular Multilevel Medium Voltage Grid-Tied Power Converters,” *2nd International Conference on Electrical, Computer and Communication Engineering, ECCE 2019*, pp. 7–9, 2019.

- [9] I. N. W. Satiawan, "Carrier Based PWM Methods of Dual Cascaded Inverter for Solar Power Plant Solid State Transformer," *2021 International Conference on Smart-Green Technology in Electrical and Information Systems (ICSGTEIS)*, no. October, pp. 80–85, 2021.

- [10] Z. Li, Y. Zhang, Z. Wang, J. Liu, Z. Ji, and F. Chang, "Bilateral Common-mode Voltage Injection Method with Minimized Low-frequency Ripple Buffering of AC / AC Solid-State Transformer," *2024 IEEE 10th International Power Electronics and Motion Control Conference (IPEMC2024-ECCE Asia)*, vol. 2, no. 1, pp. 70–77, 2024.

- [11] N. Menger, T. Merz, J. Gehringer, F. Sommer, and M. Hiller, "Loss Estimation of a Dual Active Bridge as part of a Solid State Transformer using Frequency Domain Modelling," *IEEE Energy Conversion Congress and Exposition (ECCE)*, 2022.

- [12] B. Schmitz-Rode, L. Stefanski, R. Schwendemann, S. Decker, S. Mersche, P. Kiehnle, P. Himmelmann, A. Liske, and M. Hiller, "A modular signal processing platform for grid and motor control, HIL and PHIL applications," *2022 International Power Electronics Conference, IPEC-Himeji 2022-ECCE Asia*, pp. 1817–1824, 2022.

- [13] N. Menger, T. Merz, G. Ziegelmair, R. Schwendemann, and M. Hiller, "Decoupled Control Structure of a Modular Solid State Transformer," *2023 25th European Conference on Power Electronics and Applications, EPE 2023 ECCE Europe*, 2023.