# **Design and Investigation of Efficient Millimeter-wave Silicon-based Power Amplifiers**

Zur Erlangung des akademischen Grades eines

**DOKTORS DER INGENIEURWISSENSCHAFTEN

(Dr.-Ing.)**

von der KIT-Fakultät für

Elektrotechnik und Informationstechnik

des Karlsruher Instituts für Technologie (KIT)

angenommene

## **DISSERTATION**

von

**M.Sc. Alexander Haag**

geboren in: Germersheim

Tag der mündlichen Prüfung:

05.09.2025

Hauptreferent:

Korreferent:

Prof. Dr.-Ing. Ahmet Çağrı Ulusoy

Prof. Dr. Jens Anders

# Zusammenfassung

Mit dem Bestreben höhere Datenraten für die nächsten Generationen der mobilen Kommunikationsinfrastruktur, zum Beispiel für Mobilfunk der fünften und sechsten Generation, sowie für zukünftige Satellitenkommunikation zu erreichen, sind Frequenzbänder zwischen 10 GHz und 60 GHz ein Feld intensiver akademischer wie industrieller Forschung geworden. Für beide Anwendungen ist die Nutzung von Antennengruppen vorgesehen, wodurch die benötigte Signalleistung pro Antennenkanal in siliziumbasierten Technologien erreichbar wird. Trotzdem ist das Erreichen der benötigten Ausgangsleistungen mit Leistungsverstärkern in Silizium oder Siliziumgermanium herausfordernd und typischerweise werden diese in III/V Technologien wie Galliumarsenid oder Galliumnitrid realisiert. Um die limitierte Performanz von siliziumbasierten Leistungsverstärkern zu überwinden, werden in dieser Arbeit verschiedene Aspekte der Leistungsverstärkerentwicklung im Millimeterwellenfrequenzbereich untersucht.

Zuerst werden Leistungsverstärker mit einem einzelnen Verstärkerkern, welcher über diskrete LC-Netzwerke angepasst wird, betrachtet. Die Anpassnetzwerke werden auf optimale Topologie und erreichbare Netzwerkeffizienz erforscht. Das Ziel ist die Netzwerkverluste bereits vor der Implementierung genau vorhersagen zu können. In dieser Untersuchung wird der Qualitätsfaktor jeder Netzwerkkomponente in Abhängigkeit ihrer Größe und der gewählten Frequenz modelliert. Das so entwickelte Verfahren findet die maximal zu erwartende Netzwerkeffizienz für jeden Punkt im Smith Diagramm, einschließlich der optimalen Netzwerktopologie an den jeweiligen Punkten. Zwei Leistungsverstärker werden mit der gefundenen optimalen Netzwerktopologie entwickelt. Ein Leistungsverstärker, integriert in einer 130 nm SiGe Technologie, erreicht bei einer Arbeitsfrequenz von 28 GHz eine gesättigte Ausgangsleistung von 23.7 dBm und eine maximale leistungsbezogene Effizienz (PAE) von 40 %. Ein zweiter Leistungsverstärker, integriert in einer 22 nm FD-SOI CMOS Technologie, erreicht bei 18 GHz eine maximale Ausgangsleistung von 17 dBm bei einer PAE

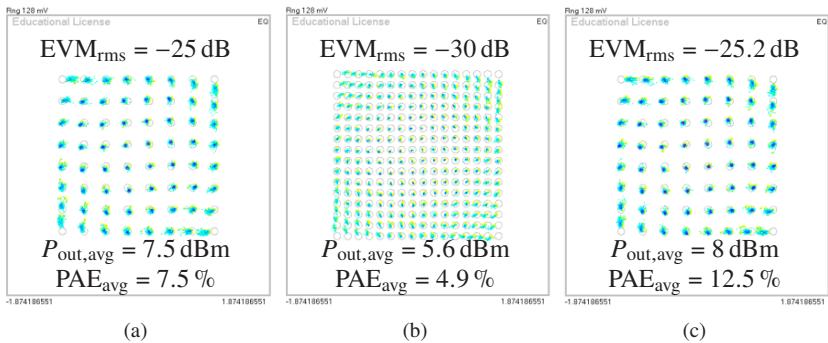

von 45 %. Bei Betrieb mit einem 64-QAM moduliertem Signal erreicht der Leistungsverstärker eine durchschnittliche PAE von 12.5 %. Beide Verstärker sind für ihre jeweiligen Technologien sehr kompakt und benötigen nur eine geringe Chipfläche.

Darauffolgend wird Leistungskombination zur Erhöhung der limitierten Ausgangsleistung von Silizium untersucht. Die am häufigsten eingesetzten Methoden, Transformatoren und Wilkinson-Kombinatoren, werden verglichen. Während Transformatoren für ihre hohe Effizienz und geringen Platzbedarf bekannt sind, ist ihre Nutzbarkeit zur Erzeugung hoher Leistungen bei Millimeterwellen durch geometrische Anforderungen begrenzt. Ein pseudo-differenzieller Leistungsverstärker, bestehend aus einem Transistor mit einem Windungsverhältnis von 2 zu 1 und zwei Verstärkerkernen wird in 130 nm SiGe BiCMOS entwickelt, um explorativ die Leistungserzeugung mit Transformatoren zu untersuchen. Durch Komplikationen während der Vermessung erreicht der Leistungsverstärker nur eine Ausgangsleistung von 23.7 dBm bei einer PAE von 26 %. Im Anschluss wird gezeigt, dass Wilkinson-Kombinatoren ohne Isolationswiderstand 16-zu-1 Kombinierung mit Quellimpedanzen im Bereich von  $10\Omega$  ermöglichen. Bei optimalem Design zeigen diese Kombinatoren eine hohe Effizienz. Im Vergleich zu Transformatoren steigt jedoch der Bedarf an Fläche.

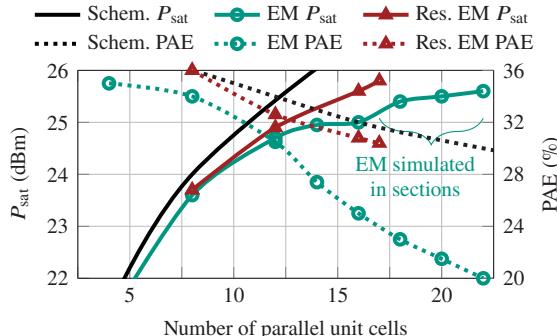

Der Hauptteil dieser Arbeit untersucht den Entwurf der Verstärkerkerne und der dazugehörigen Grenzen bei großer Parallelisierung von Transistoren. Im Rahmen dieser Arbeit wird die Größe der Verstärkerkerne durch die Parallelisierung mehrerer Einheitszellen variiert. Durch die Modellierung der bei dieser Parallelisierung entstehenden parasitären Elemente wird gezeigt, dass für niedrige Impedanzen, zum Beispiel am Eingang oder bei der optimalen Lastimpedanz am Ausgang, die internen parasitären Elemente zu einer Verschlechterung der Performanz führen. Hauptsächlich tragen die notwendigen Leitungsstücke zwischen den Einheitszellen zu dieser Verschlechterung bei. Sowohl ohmsche Verluste in den Leitungssegmenten als auch Variationen in der Belastung der individuellen Einheitszellen verursachen die Reduktion in der Performanz. Eine neue Entwurfsmethode, resonante Verstärkerkerne, wird vorgestellt, um den Einfluss der parasitären Elemente zu reduzieren. Am Ein- und Ausgang werden parallel geschaltete Induktivitäten so entworfen, dass sie sich mit den parasitären Kapazitäten der aktiven Komponenten in Resonanz befinden und so die lokalen Impedanzen innerhalb des Verstärkerkerns erhöhen. Der Einfluss der Leitungsstücke wird hierdurch minimiert. Unter Nutzung dieser Methode wer-

---

den Leistungsverstärkerprototypen mit hoher Ausgangsleistung entworfen und demonstrieren neue Rekorde in der Ausgangsleistung. Die finalen Prototypen erreichen bei 28 GHz jeweils eine gesättigte Ausgangsleistung von 31.7 dBm und 36.7 dBm. Dies entspricht einer Verbesserung gegenüber vorherigen Veröffentlichungen um 6 bis 10 dB. Die zugehörige PAE beträgt jeweils 36.8 % und 28 %.

Zum Abschluss wird eine allgemeine Entwurfsmethode für hohe Effizienzen unter modulierter Anregung betrachtet. Um die Verstärkerlinearität ab Anfang des Entwurfsprozess zu berücksichtigen wird Zweittonanregung zur Bestimmung des Arbeitspunktes, Biasnetzwerks und der optimalen Lastimpedanz verwendet. Die PAE bei einem IMD3 von  $-25$  dBc wird als Optimierungsmetrik verwendet. Durch Anpassung der Anforderung an IMD3 kann die gewünschte Linearität verändert werden und es wird gezeigt, dass dies die optimale Lastimpedanz verschiebt. Unter Einsatz der eingeführten Methodik wird ein *Q*-Band Leistungsverstärker in 130 nm SiGe BiCMOS entwickelt. Bei 40 GHz wird eine durchschnittliche PAE von 13.2 % für ein 64-QAM moduliertes Signal demonstriert. Die durchschnittliche Ausgangsleistung beträgt 19 dBm.

# Abstract

In pursuit of high data rates for next generation mobile communication infrastructure, e.g. fifth generation mobile communication (5G) and sixth generation mobile communication (6G), and next generation satellite communication, the frequency bands between 10 GHz and 60 GHz have become an intensive field of research for both academia and industry. For both applications antenna array configurations are envisioned and thus the required signal power per antenna channel becomes attainable in silicon-based technologies. Still, the required output power levels may be challenging to achieve with complementary metal-oxide-semiconductor (CMOS) or silicon germanium (SiGe) bipolar complementary metal-oxide-semiconductor (BiCMOS) power amplifiers (PAs). Thus integration is typically carried out in compound semiconductor technologies (III-V), such as gallium arsenide (GaAs) and gallium nitride (GaN). To overcome the limited performance of silicon PAs, this work investigates various aspects of PA design at millimeter-wave (mmWave) frequencies.

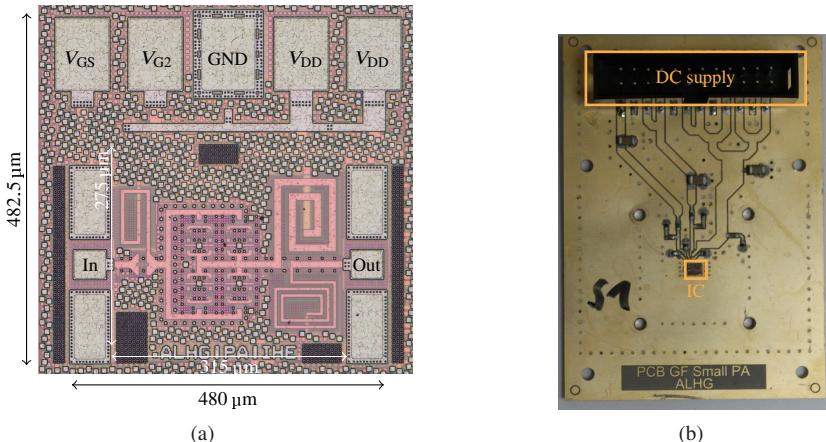

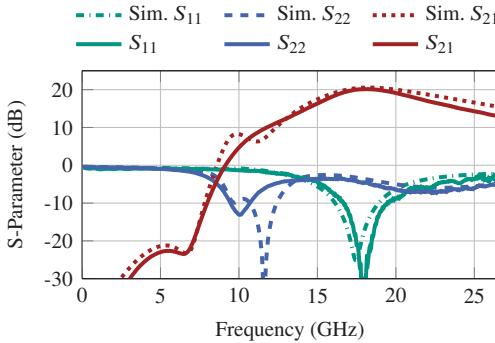

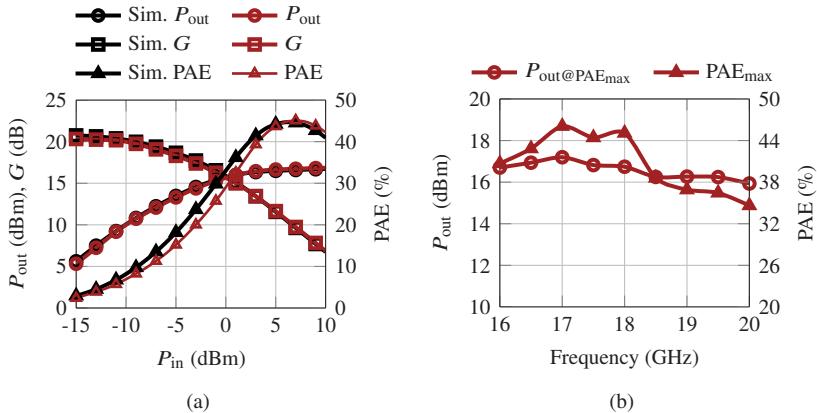

Initially, single core PAs matched by lumped LC-networks are explored. The matching networks are studied for optimal network topologies and for achievable network efficiency. The goal is to enable accurate prediction of network efficiency before implementation. In this study, each network component's quality factor is modelled depending on component value and frequency of operation. The study yields the maximum expected network efficiency for  $|\Gamma| < 0.9$  in a Smith chart normalized to  $50 \Omega$  accurately, including the best network topology for each point. Two PAs are then designed according to the best network topology. A first PA, integrated in 130 nm SiGe BiCMOS, achieves a medium saturated output power of 23.7 dBm and a peak power-added efficiency (PAE) of 40 % at 28 GHz. A second PA integrated in 22 nm FD-SOI CMOS achieves a saturated output power of 17 dBm with a PAE of 45 % and an average modulated PAE of 12.5 % for a 64-quadrature amplitude modulation (QAM) signal at 18 GHz. Both PAs are among the most area efficient designs in their respective technologies, thus being especially interesting for large antenna arrays.

In the following the focus is shifted towards increasing the limited output power of silicon using power combiners. The most used methods, transformers and Wilkinson combiners, are compared. While transformers are very efficient and compact power combiners, at mmWave frequencies their use to deliver high output power in silicon is limited by geometric constraints. A pseudo-differential PA using a transformer with a turn ratio of 2-to-1 is presented in 130 nm SiGe BiCMOS to explore power combining with transformers, but due to complications during the measurement the PA only achieves 23.7 dBm of output power at a PAE of 26 %. Next, Wilkinson combining, without isolation resistor, is shown to enable 16-to-1 combination without significantly limiting the source impedance range. When optimally designed, the combiners show high efficiency, however the area consumption is increased compared to transformers.

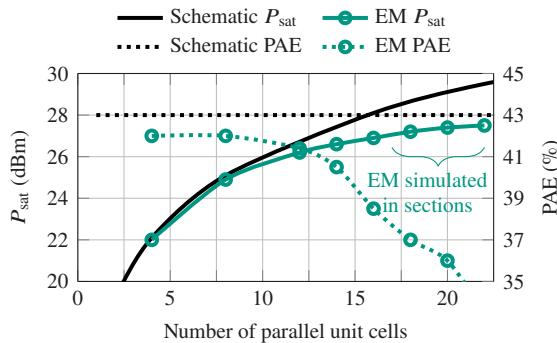

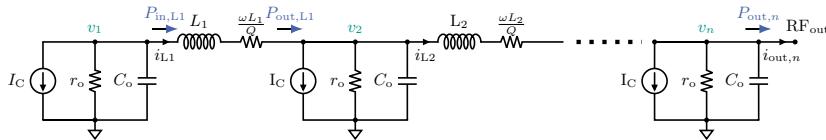

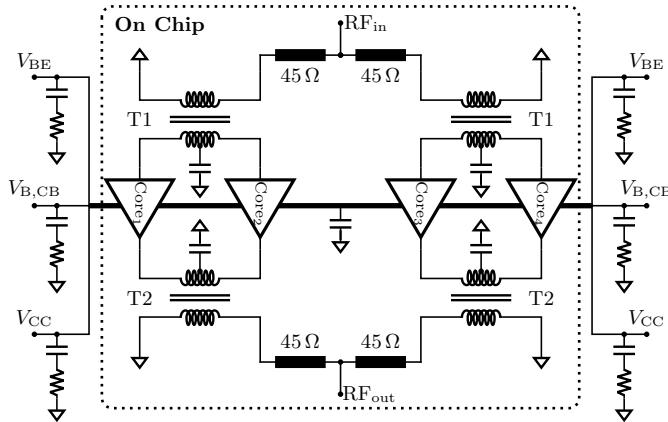

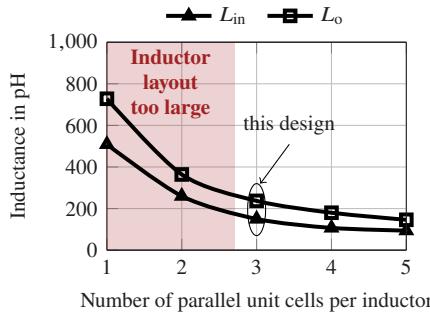

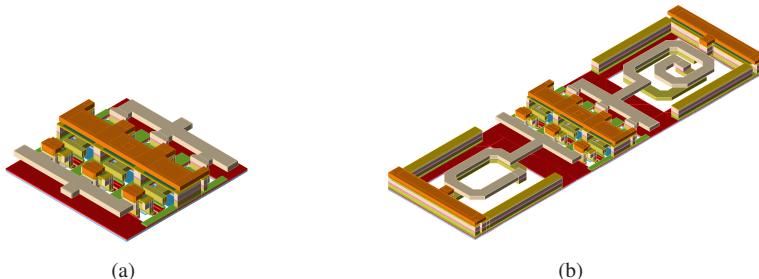

The main part of this work investigates power amplifier core design and the limits of large device parallelization. Throughout this work the size of a device inside a PA core is varied by parallelizing multiple unit cells. By modelling the parasitics created by this parallelization, it is shown that for low impedances inside the core, for example input and load-pull impedance, the internal parasitics inside the core reduce the PA core performance. This reduction is mainly caused by the necessary line segments between the unit cells. Both ohmic loss of the line segments and variation in the loading of individual unit cells cause performance degradation. A novel design method, the resonated amplifier core, is introduced to reduce the impact of parasitics. Shunt inductors at input and output of the core, designed to be in resonance with the parasitic capacitors, are used to increase the local impedances and thus reduce the effect of the line segments. Multiple optimization steps are presented to refine the design method to improve performance. Using these methods high power SiGe BiCMOS PA prototypes are developed and demonstrate record breaking output power. The final designs achieve saturated output power levels of 31.7 dBm and 36.7 dBm at 28 GHz, improving upon state of the art by 6 to 10 dB. The corresponding PAE is 36.8 % and 28 %, respectively.

Lastly, a general design method aiming for high modulated efficiency is explored. To consider a PA's linearity from the start of the design, two-tone excitation is used to find the operating point, bias network and load-pull impedance. PAE for a third order intermodulation distortion (IMD3) of  $-25$  dBc is used as the metric for optimization. By shifting the requirement for IMD3 the desired linearity can be adjusted, and the optimal load-pull impedance is shown to vary

---

depending on the desired value of IMD3. Using the introduced method a  $Q$ -band PA prototype in 130 nm SiGe BiCMOS is developed. It achieves 13.2 % average PAE for a 64-QAM signal. The average output power is 19 dBm.

# Acknowledgement

To begin, I would like to express my sincere gratitude towards Prof. Dr.-Ing. Ahmet Çağrı Ulusoy for supervision and mentoring throughout this work. He was very supportive of my work and enabled me to freely pursue new ideas, of which some may have use. I deeply appreciate his continued support, mentoring and contribution for our start-up. To Prof. Dr. Jens Anders, I extend my gratitude for the co-lecturing of this thesis. Additionally, I would like to thank Prof. Dr.-Ing. Thomas Zwick, who offered me to stay at IHE after examining my master thesis and for bringing me in touch with Prof. Dr.-Ing. Ahmet Çağrı Ulusoy.

My gratitude is owed to all the staff at IHE. I thank Marion Jentzsch, Simone Gorré and Angela Ziemba for their support and patience in bureaucratic matters. Ronald Vester, Thorsten Fux, Andreas Gallego, Mirko Nonnenmacher, Jasmin Rösner and especially Andreas Lipp for preparing measurement samples.

I want to thank all my colleagues at IHE for their support and company, as well as a good amount of fun, during the last six years. Special thanks to Ibrahim Kağan Aksoyak and Selina Eckel with whom I've shared a room for this time and who successfully dealt with me on a daily basis.

I extend a personal thank you to my friends and all my family. In particular, my little brother Michael, who is in fact not that little anymore, and my mother Ute and father Jörg for enabling me to pursue my studies.

Lastly, I would like to express my special thanks to Johanna Julia Wrabitz, who encouraged and supported me for the better part of this journey.

July 2025,

Karlsruhe, Germany

Alexander Haag

# Contents

|                                                                                                   |    |

|---------------------------------------------------------------------------------------------------|----|

| <b>Zusammenfassung</b> . . . . .                                                                  | i  |

| <b>Abstract</b> . . . . .                                                                         | v  |

| <b>Acknowledgement</b> . . . . .                                                                  | ix |

| <b>Acronyms and symbols</b> . . . . .                                                             | xv |

| <b>1 Introduction</b> . . . . .                                                                   | 1  |

| 1.1 Power Amplifiers for Satellite Communication . . . . .                                        | 5  |

| 1.2 State-of-the-art CMOS and SiGe BiCMOS Power Amplifiers . . . . .                              | 7  |

| 1.3 Power Amplifier Terminology . . . . .                                                         | 9  |

| 1.4 CMOS and SiGe BiCMOS Technologies . . . . .                                                   | 10 |

| 1.5 Thesis Goal and Outline . . . . .                                                             | 11 |

| <b>2 Power Amplifier Basics</b> . . . . .                                                         | 13 |

| 2.1 Transistors, Topologies and Challenges for Millimeter-Wave Silicon Power Amplifiers . . . . . | 18 |

| <b>3 Optimization of LC-based Output Matching Network Design</b> . . . . .                        | 25 |

| 3.1 Efficiency Optimization of LC-Matching Networks . . . . .                                     | 26 |

| 3.1.1 Efficient 23.7 dBm Ka-Band PA in 130nm SiGe . . . . .                                       | 34 |

| 3.1.2 Efficient Ku-Band PA in 22nm FD-SOI . . . . .                                               | 38 |

| 3.2 Conclusion . . . . .                                                                          | 45 |

| <b>4 Efficient On-Chip Power Combining</b> . . . . .                                              | 47 |

| 4.1 Transformer-based combining . . . . .                                                         | 48 |

| 4.1.1 Scalability of Transformer Combining . . . . .                                              | 52 |

|          |                                                                         |            |

|----------|-------------------------------------------------------------------------|------------|

| 4.1.2    | 23.7 dBm Pseudo Differential Ka-Band PA in 130nm SiGe . . . . .         | 54         |

| 4.2      | In-phase Power Combining . . . . .                                      | 62         |

| 4.2.1    | Layer comparison . . . . .                                              | 67         |

| 4.3      | Conclusion . . . . .                                                    | 69         |

| <b>5</b> | <b>Resonated Amplifier Cores . . . . .</b>                              | <b>71</b>  |

| 5.1      | Large Device Parallelization in PA Cores . . . . .                      | 71         |

| 5.1.1    | PA Core Interconnect Analysis . . . . .                                 | 74         |

| 5.2      | Resonated Amplifier Cores . . . . .                                     | 77         |

| 5.2.1    | Resonated Core Interconnect Analysis . . . . .                          | 78         |

| 5.3      | 30.8 dBm $K_a$ -Band Power Amplifier in 130nm SiGe . . . . .            | 80         |

| 5.3.1    | Resonated Amplifier Core Design . . . . .                               | 80         |

| 5.3.2    | Power Combiner Design . . . . .                                         | 85         |

| 5.3.3    | On-chip Thermal Analysis . . . . .                                      | 87         |

| 5.3.4    | Characterization . . . . .                                              | 89         |

| 5.4      | 24 dBm $Q$ -Band Power Amplifier in 22nm FDSOI . . . . .                | 92         |

| 5.4.1    | Resonated Amplifier Core Design . . . . .                               | 92         |

| 5.4.2    | Characterization . . . . .                                              | 97         |

| 5.5      | 32 dBm $K_a$ -Band Power Amplifier in 130nm SiGe . . . . .              | 101        |

| 5.5.1    | Resonated Amplifier Core Design . . . . .                               | 102        |

| 5.5.2    | 4:1 Power Splitter and Combiner Design . . . . .                        | 105        |

| 5.5.3    | Characterization . . . . .                                              | 107        |

| 5.6      | 36.7 dBm $K_a$ -Band Power Amplifier in 130nm SiGe . . . . .            | 111        |

| 5.6.1    | 16:1 Power Splitter and Combiner Design . . . . .                       | 111        |

| 5.6.2    | Characterization . . . . .                                              | 118        |

| 5.7      | Conclusion . . . . .                                                    | 122        |

| <b>6</b> | <b>Linear Power Amplifier Design Using Two-Tone Load-pull . . . . .</b> | <b>125</b> |

| 6.1      | Two-Tone Load-pull . . . . .                                            | 127        |

| 6.2      | Linear Q-Band Power Amplifier in 130nm SiGe . . . . .                   | 131        |

| 6.2.1    | Analysis and Design . . . . .                                           | 132        |

| 6.2.2    | Characterization . . . . .                                              | 139        |

| 6.3      | Conclusion . . . . .                                                    | 145        |

| <b>7</b> | <b>Conclusion and Outlook . . . . .</b>                                 | <b>147</b> |

|                                                          |            |

|----------------------------------------------------------|------------|

| <b>A Appendix</b> . . . . .                              | <b>153</b> |

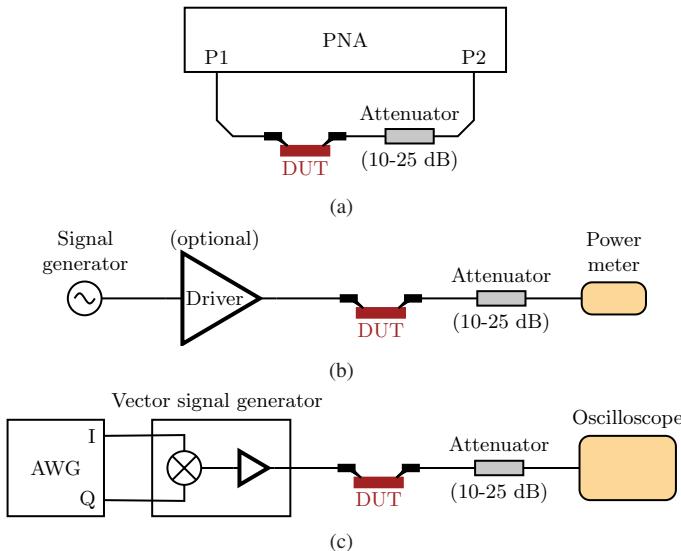

| A.1 Measurement Setups . . . . .                         | 153        |

| A.2 In-phase Power Combiner Comparison . . . . .         | 154        |

| A.3 Printed Circuit Boards for Measurements . . . . .    | 156        |

| A.4 Additional Material on Core Design . . . . .         | 157        |

| A.5 References for State of the Art Comparison . . . . . | 158        |

| A.6 Temperature Sensor . . . . .                         | 158        |

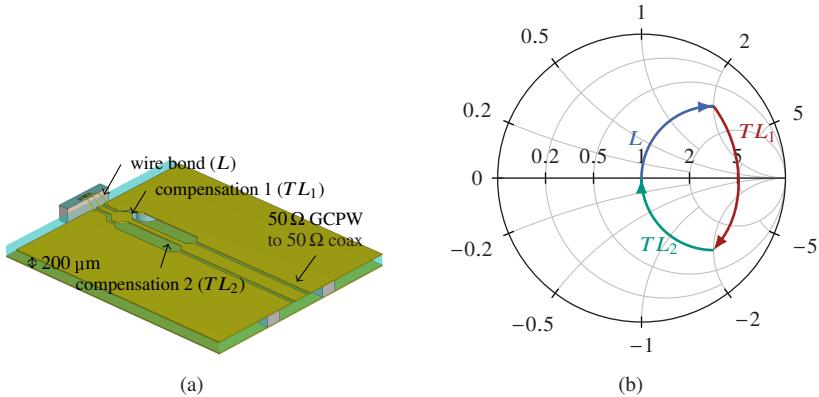

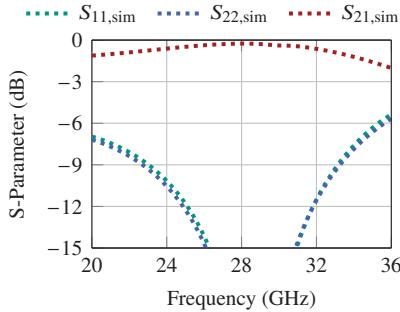

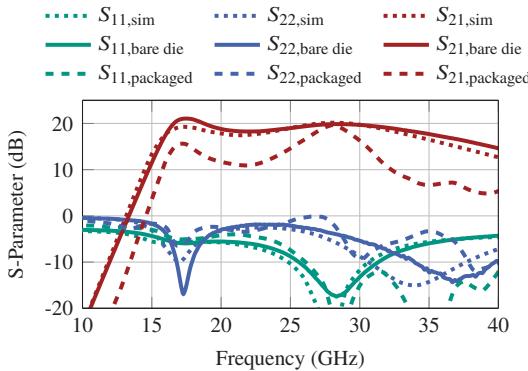

| A.7 28 GHz Chip to Coaxial Transition . . . . .          | 160        |

| <b>Bibliography</b> . . . . .                            | <b>163</b> |

| <b>Own Publications</b> . . . . .                        | <b>179</b> |

| Patents . . . . .                                        | 179        |

| Journal Papers . . . . .                                 | 179        |

| Conference Papers . . . . .                              | 180        |

# Acronyms and symbols

## Acronyms

|               |                                                 |

|---------------|-------------------------------------------------|

| <b>5G</b>     | fifth generation mobile communication           |

| <b>6G</b>     | sixth generation mobile communication           |

| <b>AC</b>     | alternate current                               |

| <b>ACPR</b>   | adjacent channel power ratio                    |

| <b>ADS</b>    | Advanced Design System                          |

| <b>Al</b>     | aluminum                                        |

| <b>APSK</b>   | amplitude and phase-shift keying                |

| <b>AWG</b>    | arbitrary waveform generator                    |

| <b>BEOL</b>   | back end of line                                |

| <b>BER</b>    | bit error rate                                  |

| <b>BiCMOS</b> | bipolar complementary metal-oxide-semiconductor |

| <b>CB</b>     | common-base                                     |

| <b>CE</b>     | common-emitter                                  |

| <b>CG</b>     | common-gate                                     |

| <b>CS</b>     | common-source                                   |

| <b>Cu</b>     | copper                                          |

|               |                                         |

|---------------|-----------------------------------------|

| <b>CMOS</b>   | complementary metal-oxide-semiconductor |

| <b>DAT</b>    | distributed active transformer          |

| <b>DC</b>     | direct current                          |

| <b>DPA</b>    | Doherty power amplifier                 |

| <b>DUT</b>    | device under test                       |

| <b>EC</b>     | equivalent circuit                      |

| <b>EIRP</b>   | effective isotropic radiated power      |

| <b>EM</b>     | electromagnetic                         |

| <b>ESD</b>    | electrostatic discharge                 |

| <b>EVM</b>    | error vector magnitude                  |

| <b>FD-SOI</b> | fully depleted silicon on insulator     |

| <b>FEOL</b>   | front end of line                       |

| <b>FET</b>    | field effect transistor                 |

| <b>FSPL</b>   | free-space path loss                    |

| <b>GaAs</b>   | gallium arsenide                        |

| <b>GaN</b>    | gallium nitride                         |

| <b>GF</b>     | GlobalFoundries                         |

| <b>GND</b>    | ground                                  |

| <b>HB</b>     | harmonic balance                        |

| <b>HBT</b>    | heterojunction bipolar transistor       |

| <b>HEMT</b>   | high-electron-mobility-transistor       |

| <b>HPA</b>    | high power amplifier                    |

|               |                                                          |

|---------------|----------------------------------------------------------|

| <b>IC</b>     | integrated circuit                                       |

| <b>IHE</b>    | Institute of Radio Frequency Engineering and Electronics |

| <b>IHP</b>    | Leibniz Institute for High Performance Microelectronics  |

| <b>IL</b>     | insertion loss                                           |

| <b>IM3</b>    | third order intermodulation product                      |

| <b>IMD3</b>   | third order intermodulation distortion                   |

| <b>IMN</b>    | input matching network                                   |

| <b>KIT</b>    | Karlsruhe Institute of Technology                        |

| <b>LEO</b>    | low earth orbit                                          |

| <b>LMBA</b>   | Load Modulated Balanced Amplifier                        |

| <b>MIM</b>    | metal-insulator-metal                                    |

| <b>mmWave</b> | millimeter-wave                                          |

| <b>MoM</b>    | metal-oxide-metal                                        |

| <b>MPA</b>    | medium power amplifier                                   |

| <b>NF</b>     | noise figure                                             |

| <b>OFDM</b>   | orthogonal frequency-division multiplexing               |

| <b>OMN</b>    | output matching network                                  |

| <b>PA</b>     | power amplifier                                          |

| <b>PAE</b>    | power-added efficiency                                   |

| <b>PAPR</b>   | peak-to-average power ratio                              |

| <b>PCB</b>    | printed circuit board                                    |

| <b>PD</b>     | power density                                            |

|               |                                    |

|---------------|------------------------------------|

| <b>Q</b>      | quality factor                     |

| <b>QAM</b>    | quadrature amplitude modulation    |

| <b>RADAR</b>  | radio detection and ranging        |

| <b>RF</b>     | radio frequency                    |

| <b>RFIC</b>   | radio frequency integrated circuit |

| <b>RMS</b>    | root mean square                   |

| <b>SatCom</b> | satellite communication            |

| <b>SEE</b>    | single event effects               |

| <b>SRF</b>    | self-resonant frequency            |

| <b>Si</b>     | silicon                            |

| <b>SiGe</b>   | silicon germanium                  |

| <b>SNR</b>    | signal-to-noise ratio              |

| <b>TID</b>    | total ionizing dose                |

| <b>TL</b>     | transmission line                  |

| <b>TX</b>     | transmitter                        |

| <b>UC</b>     | unit cell                          |

| <b>UCS</b>    | unit cell segment                  |

## Frequently used symbols

|            |                                |

|------------|--------------------------------|

| $BW$       | Bandwidth                      |

| $BV_{CEO}$ | open-base breakdown voltage    |

| $BV_{CBO}$ | open-emitter breakdown voltage |

|                   |                          |

|-------------------|--------------------------|

| $f$               | Frequency                |

| $\omega$          | Angular frequency        |

| $L_E$             | Emitter length           |

| $P$               | Power                    |

| $P_{\text{out}}$  | Output power             |

| $P_{\text{sat}}$  | Saturated output power   |

| $\lambda$         | Wavelength               |

| $\varphi$         | Phase shift              |

| $T$               | Temperature              |

| $V_{\text{knee}}$ | Knee voltage             |

| $Z_{\text{in}}$   | Input impedance          |

| $Z_L$             | Load impedance           |

| $Z_{\text{LP}}$   | Load-pull impedance      |

| $Z_{\text{out}}$  | Output impedance         |

| $Z_S$             | Source impedance         |

| $Z_0$             | Characteristic impedance |

## Constants

$\pi = 3.141\,59$

PI

$k_B = 1.38 \times 10^{-23} \text{ J/K}$

Boltzmann's constant

$c = 299\,792\,458 \text{ m/s}$

speed of light in vacuum

# 1 Introduction

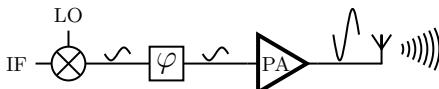

In recent years, a strong push towards higher frequencies for communication and radio detection and ranging (RADAR) applications could be seen in academia, as well as industry. The introduction of 5G at frequencies up to 6 GHz and on-going research endeavors for the 5G FR2 bands around 28 GHz [3GP24], automotive radar at 76 to 81 GHz [HTS<sup>+</sup>12] as well as on-going research towards 6G [IYK<sup>+</sup>21] and low earth orbit (LEO) satellite constellations [ACC<sup>23</sup>] highlight the need for continued innovation in radio frequency integrated circuit (RFIC) design. Significant advances in silicon-based technologies now enable the integration of entire high frequency systems on a single silicon (Si) chip, including digital and mixed-signal components. This is especially interesting due to a reduction in cost and packaging complexity. However, the technological advances improving the achievable transistor speeds usually come at the cost of reduced nominal supply voltages for the active devices. One important high frequency component, which is especially affected by a reduction in supply voltage, is the power amplifier (PA). PAs are a necessity in any radio frequency (RF) and mmWave system, as they provide the required signal power in either RADAR detection or communication applications. Additionally, PAs typically dissipate the most power in a transmitter, or possibly the entire transceiver, and thus their efficiency dominates the overall efficiency of the system. Fig. 1.1 illustrates a basic block diagram of an integrated transmitter chain, including a mixer, phase shifter and the PA, as well as a qualitative representation of signal strength.

Figure 1.1: Basic transmitter chain including a mixer, phase shifter (PS), PA and antenna.

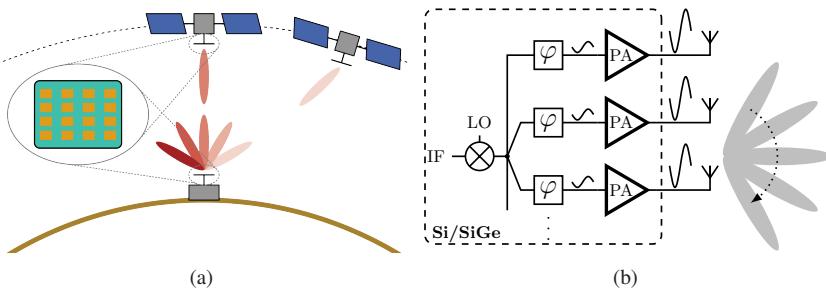

Two application scenarios envisioned at  $K_a$ -band frequencies are mobile communication and LEO satellite communication (SatCom). In Fig. 1.2 a SatCom scenario and a simplified beamforming transmitter block diagram are depicted. In the past, the stringent requirements on the performance of PAs mandated the usage of III/V technologies such as GaN or GaAs when targeting mmWave frequencies. This previously prevented the integration of a full system in a single chip. However, compared to classical transceiver architectures with just a single PA, the introduction of phased array architectures in numerous applications reduces the required output power per PA and enables the integration of entire systems in CMOS or SiGe BiCMOS technologies.

Figure 1.2: Example applications for CMOS and SiGe BiCMOS PAs: a) LEO SatCom and b) beamforming transmitters.

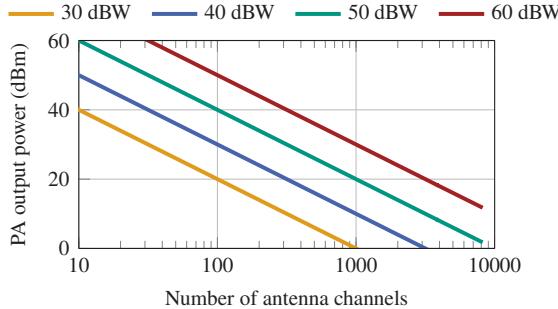

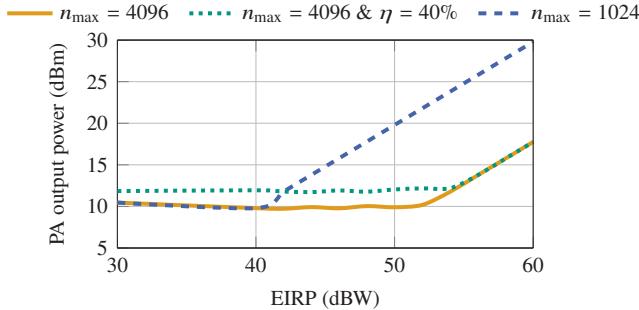

In Fig. 1.3 the required output power per PA versus the number of antenna channels is depicted for different total effective isotropic radiated power (EIRP) values. The transmitter architecture is assumed as previously shown in Fig. 1.2b. For the calculation a unit element antenna gain,  $G_{\text{unit}}$ , of 4 dBi and a power margin,  $M$ , of 4 dB for large scan angles are assumed. The PA output power,  $P_{\text{PA,dBm}}$ , is calculated using

$$P_{\text{PA,dBm}} = \text{EIRP}_{\text{dBW}} + 30 + M_{\text{dB}} - G_{\text{unit,dBi}} - 20 \cdot \log(n) \quad (1.1)$$

with  $n$  being the number of channels in the array.

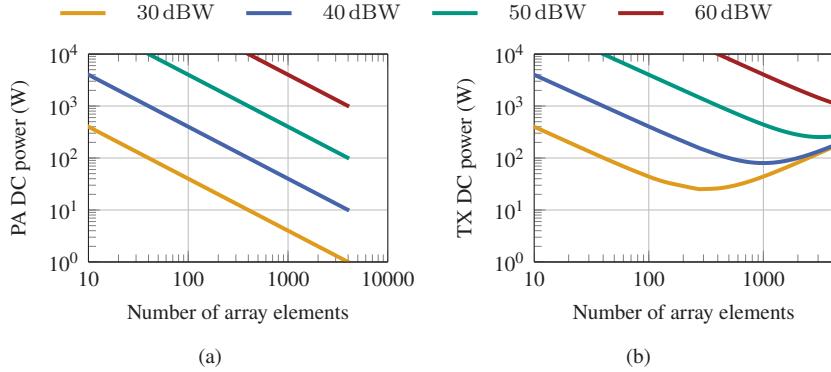

Given enough elements within an array the required output power per PA can be reduced. For example, to achieve 40 dBW in a 1024-element array, an individual PA must output around 10 dBm, which is feasible in silicon. Additionally, an important parameter is direct current (DC) power consumption. In Fig. 1.4a the

Figure 1.3: Required output power per PA versus number of antenna elements to achieve a target EIRP.

cumulative DC power consumption of all PAs within a transmitter is shown over the number of channels in the transmitter. The power consumption is calculated with

$$P_{DC,PA} = \frac{P_{PA,W}}{\eta} \cdot n. \quad (1.2)$$

Independent of the output power per PA a constant efficiency,  $\eta$ , of 25 % is used. By increasing the size of the array and reducing the output power per PA the cumulative DC power consumption of all PAs is reduced. However, this calculation assumes that the PAs dominate the overall power consumption. When the arrays become larger and the output power per PA is reduced this assumption is no longer valid and the power consumption of the other components, e.g., the phase shifters, becomes relevant. Fig. 1.4b shows the transmitter power consumption over the number of channels when a power consumption of 40 mW is added per channel, to model the power consumption of other components. Depending on the target EIRP values different optimum transmitter sizes are obtained for which the DC power consumption is minimized. For the given example values the optimum array size for an EIRP of 40 dBW is around 1024 elements, corresponding to a PA output power of approximately 10 dBm. Similarly, for a target EIRP of 30 dBW the PA output power for the optimum array size of 300 is 10 dBm.

In Fig. 1.5, the optimum output power per PA to minimize power consumption is shown versus EIRP of the transmitter. Using a maximum number of channels,  $n_{max}$ , of 4096 as the base case, the optimum PA output power remains around 10 dBm until an EIRP of 52 dBW. For higher EIRP values, the array would have

Figure 1.4: Transmitter DC power consumption for different EIRP values: a) only PA power consumption and b) system power consumption.

to be larger than 4096 elements and thus the output power per PA increases. Additionally, the same results are plotted when the efficiency of the PAs is increased to 40 %. Except for an increase in the optimum output power per PA at lower EIRP values, the trend remains the same. Lastly, the optimum PA output power for a maximum array size of 1024 is shown. For this case, the rise in output power per PA starts at an EIRP of 40 dBW. Following this analysis a larger number of channels in the array is expected to be more efficient, however, so far other factors such as physical size of the array and feasibility have been neglected. In contrast, typical phased arrays reported in [ACC<sup>+</sup>23] only feature element numbers up to 1024 and thus PA output power may range between 10 to 30 dBm for the analysed EIRP range of 30 to 60 dBW.

Figure 1.5: Optimum PA output power versus transmitter EIRP to minimize DC power consumption.

An example application at  $K_a$ -band are LEO satellites, which in comparison to geostationary communication satellites, are only visible for several minutes per flyover. Both the satellite and user terminal have to align their antenna beams for successful communication. This can either be done mechanically or electronically using the previously discussed phased arrays, with the latter being the preferred option [ACC<sup>+</sup>23]. Similarly, for future mobile communication multiple simultaneous beams and beam steering are envisioned. With the prospect of using antenna arrays in future communication and radar systems, PA design in CMOS or SiGe BiCMOS technologies remains a key challenge of integrated circuit (IC) design.

However, even with reduced requirements, the development of PAs at these frequencies is challenging in silicon-based technologies. Power requirements may range between 10 dBm to 30 dBm per channel, and especially the upper end is beyond what state of the art can produce with a peak efficiency above 20 % [WNP16, ELM14]. This work investigates fundamental design methods to increase the delivered power of CMOS or SiGe BiCMOS PAs at mmWave frequencies in pursuit of eliminating the expensive GaN or GaAs devices.

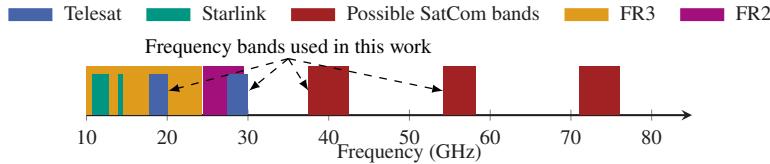

## 1.1 Power Amplifiers for Satellite Communication

As an example, potential requirements imposed on PAs for LEO SatCom at  $K_a$ -band frequencies are analyzed in the following. Fig. 1.6 visualizes the targeted frequency bands for two known LEO SatCom satellite constellations, Starlink and Telesat [ACC<sup>+</sup>23, VD19], and potential future space applications [VD19, LHHJ24]. Additionally, the frequency bands for 5G FR2 from 24.5 to 29.5 GHz [3GP24] and 6G FR3 are indicated. The frequency band around 28 GHz is actively pursued for both SatCom and mobile communication and is thus selected as one of the primary bands of interest for this work.

As previously indicated, antenna arrays are envisioned for these operations. By introducing antenna arrays, especially for LEO SatCom, the ability to electronically steer the beam during satellite flyover is a significant advantage. A first estimate of the required output power per PA can be calculated from the maximum EIRP, which is specified to be 39 dBW for Telesat with a maximum

Figure 1.6: Frequency bands for LEO SatCom, 5G FR2 and 6G FR3.

antenna gain of 38 dB. This results in a total transmitted power of 31 dBm for the satellite. Similar numbers are expected for ground stations. When this transmitted power is divided into, for example, 256 antenna elements, each antenna channel has to be provided with around 7 dBm. However, this assumes only a single antenna beam and no attenuation due to a high beam angle. Assuming that multiple simultaneous beams and high beam angles should be serviced with this EIRP per beam, the transmit power per antenna grows by several decibels to around 15-20 dBm. For communication purposes this is not the saturated output power, but rather the required power at back-off. Thus, the saturated power requirement per PA under these conditions may be in the range of 25-30 dBm. As an example, throughout this work different QAM constellations, such as 64- and 256-QAM, are used to verify average PA performance for a communication scenario. For SatCom amplitude and phase-shift keying (APSK) constellations are also used [ETS24, ACC<sup>+</sup>23]. While QAM exhibits a higher peak-to-average power ratio (PAPR) compared to APSK for similar constellations, QAM is more frequently used in mobile communication, literature and thus more suitable when comparing performance.

Depending on the specific application, the EIRP requirements might be as high as 78 dBW [VD19]. Even for a 4096 (64x64) element antenna array, with an assumed antenna element gain of 9 dBi a total transmitted power of 63 dBm is required. Not accounting for additional losses, this results in a linear power requirement of 26.9 dBm per antenna channel.

While on the satellite payloads GaN-based high power amplifiers (HPAs) are preferable due to their higher efficiency [GPCC23] and power capability, CMOS and SiGe BiCMOS are a promising option for ground stations, user terminals and as driver amplifiers, if the required power levels can be met with a suitable efficiency.

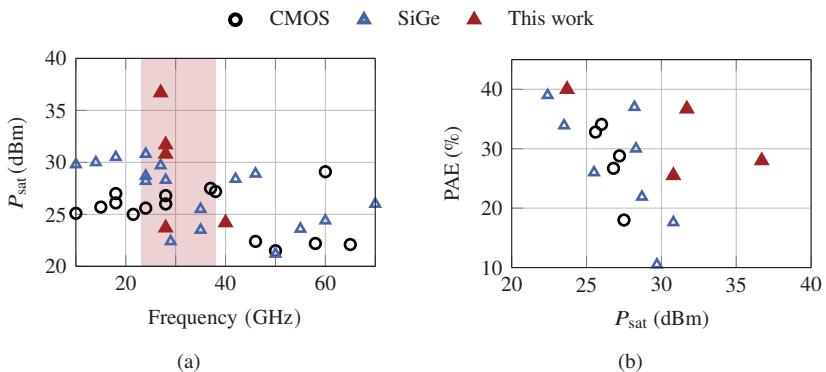

## 1.2 State-of-the-art CMOS and SiGe BiCMOS Power Amplifiers

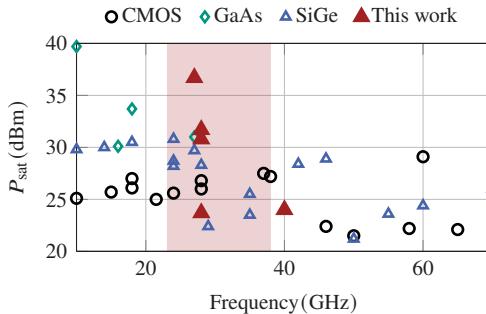

In Fig. 1.7a the saturated output power versus frequency of a collection of state-of-the-art CMOS and SiGe BiCMOS PAs [WEA<sup>+</sup>] is presented. The figure only includes integrated PAs without off-chip combiners. For a frequency range around 28 GHz, indicated in the figure, only one publication reaches a power level beyond 30 dBm. Most of the PAs achieve a saturated output power in the range of 20 to 28 dBm. However, when the associated PAE is presented versus the saturated output power for the PAs within the indicated frequency range, the PAE significantly declines for the larger PAs. Around 30 dBm the peak PAE is at or below 17 %.

Figure 1.7: State-of-the-art silicon PAs [WEA<sup>+</sup>]: a) saturated output power w.r.t. frequency from 10-70 GHz and b) PAE w.r.t. saturated output power for the indicated frequency range.

Furthermore, both SiGe BiCMOS PAs achieving 29 and 30.8 dBm utilize impractically high supply voltages beyond 5 V to achieve this performance. For faster heterojunction bipolar transistor (HBT) technologies, this is impossible. The high voltages in [ELM14, WNP16] are possible due to the slower HBTs (integrated in 0.25 and 0.35  $\mu\text{m}$  CMOS nodes) used in these publications.

In [ELM14] a cascode configuration consisting of a faster low voltage HBT as the common-emitter (CE) device and a slower high voltage HBT as the common-base (CB) device is used to increase gain, breakdown voltage and the

optimum load impedance. A total of 8 PA cores are then combined through a power combiner consisting of a combination of transmission lines (TLs) and lumped components. For a  $50\Omega$  load a combiner insertion loss of 2.4 dB is reported. During characterization, a saturated output power of 29.7 dBm for a supply voltage of 6.55 V is presented. By load-pulling the reported PA and presenting a load impedance of  $(21.2 - 18j)\Omega$  to the PA instead of  $50\Omega$ , the saturated output power is improved to 31 dBm for a supply voltage of 6.9 V. The PAE ranges from 10.2-13 % in these cases.

In [WNP16] a high power signal source is presented, consisting of a voltage-controlled oscillator and a two-stage PA. The last stage consists of four differential PA cores. Each core is comprised of a differential cascode and a matching network, which presents the optimal impedance to the core given a  $50\Omega$  load. The pre-matched cores are then combined through lumped  $50\Omega$  Wilkinson combiners and interfaced differentially at the output. At 24 GHz, the PA delivers a saturated output power of 30.8 dBm with a corresponding peak PAE of 17.6 % for a supply voltage of 5.8 V.

While these example PAs in SiGe BiCMOS use Wilkinson power combining, CMOS PAs typically utilize transformer-based combining. As an example, in [HLLW18] a PA in 90 nm CMOS with a saturated output power of 26 dBm is presented. This is among the highest power levels reported in CMOS at 28 GHz. The PAE is 34 % for a supply voltage of 2.4 V. The PA consists of two differential PA cores, which are comprised of a cascode architecture and neutralization capacitors at the common-source (CS) device, as well as an additional neutralization network across the drain and source of the common-gate (CG) device. The cores are then combined through a transformer-based network.

The presented state of the art highlights the necessity of improvements to the design methods of silicon-based PAs at higher power levels. While PAE in the CMOS example is higher compared to the SiGe examples, the saturated output power falls short of 30 dBm. The SiGe examples achieve up to 30 dBm, but at lower efficiency. All presented examples utilize a cascode structure to improve output voltage swing, but the choice of the combining network architecture and details of the PA core design differ, and no efficient solution is available.

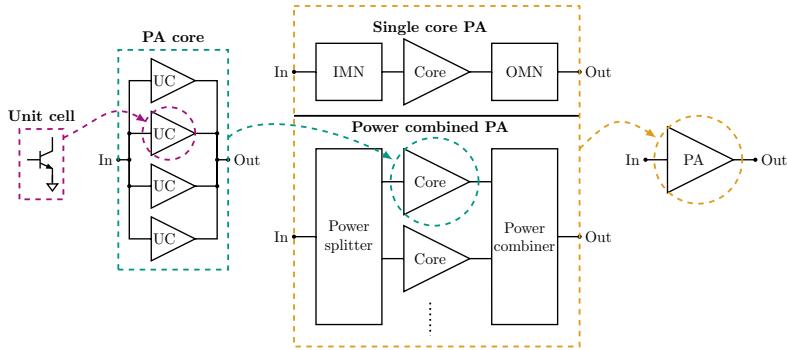

## 1.3 Power Amplifier Terminology

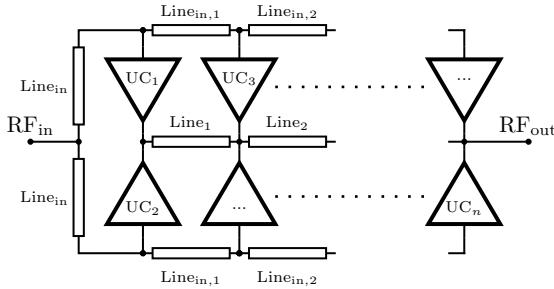

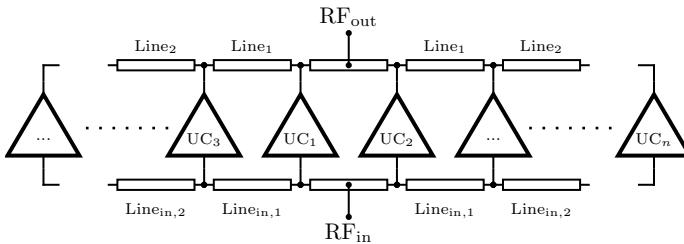

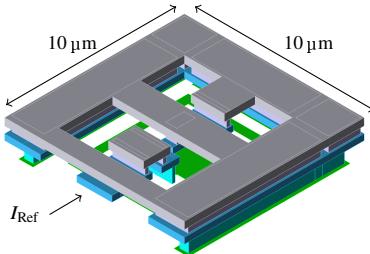

Within the context of this thesis, the structure of a PA is described as shown in Fig. 1.8. Starting at the left of Fig. 1.8, the smallest building block termed a unit cell (UC) is shown. It consists of active devices, e.g., in common-emitter or cascode configuration, with a fixed device size. Additionally, components such as resistors and capacitors could be integrated with the active devices. A PA core contains several unit cells directly connected in parallel. UCs are repeated to scale the total device size within the PA core and the core is then used as a single functional block within the design. The unit cell approach is chosen to enable convenient scaling of the PA core size. Depending on the architecture of the PA, it may consist of a single PA core directly matched to the desired system impedance through an output matching network (OMN) and input matching network (IMN) or multiple PA cores, which are interfaced through a power splitting and power combining structure. The power splitter and combiner differ from direct parallelization by including impedance transformation, e.g., transformers or transmission lines.

Figure 1.8: Power amplifier structure.

## 1.4 CMOS and SiGe BiCMOS Technologies

In this work four different technologies are used for PA design. Three of those technologies are 130 nm SiGe BiCMOS technologies from the Leibniz Institute for High Performance Microelectronics (IHP), namely SG13G2, SG13G2Cu and SG13G3Cu. Both G2 technologies share the same front end of line (FEOL), including the HBT devices. The HBTs offer  $f_T$  and  $f_{max}$  in the range of 350 GHz and 450 GHz, respectively. The G3 technology provides improved HBT performance in its FEOL with  $f_T$  and  $f_{max}$  in the range of 470 GHz and 650 GHz. The used back end of line (BEOL) is the same in the G2Cu and G3Cu technologies but differs from the SG13G2 technology. The fourth technology is GlobalFoundries (GF)' 22 nm CMOS fully depleted silicon on insulator (FD-SOI) technology, providing field effect transistors (FETs) with  $f_T$  and  $f_{max}$  in the range of 350 GHz and 370 GHz. All technologies provide sufficient transistor speed for the frequency bands between 20 GHz to 80 GHz targeted within this work. A summary is provided in table 1.1.

Table 1.1: Summary and comparison of CMOS and SiGe BiCMOS technologies used in this work.

| Tech.                     | SG13G2<br>SiGe BiCMOS | SG13G2Cu<br>SiGe BiCMOS | SG13G3Cu<br>SiGe BiCMOS | 22 nm FD-SOI<br>CMOS |

|---------------------------|-----------------------|-------------------------|-------------------------|----------------------|

| $f_{max}$ (GHz)           | 450                   | 450                     | 650                     | 370                  |

| $f_T$ (GHz)               | 350                   | 350                     | 470                     | 350                  |

| $BV_{CEO}/V_{GS,max}$ (V) | 1.6                   | 1.6                     | $\approx$ 1.5           | 0.8                  |

| Num. of metal layers      | 7                     | 8                       | 8                       | 11                   |

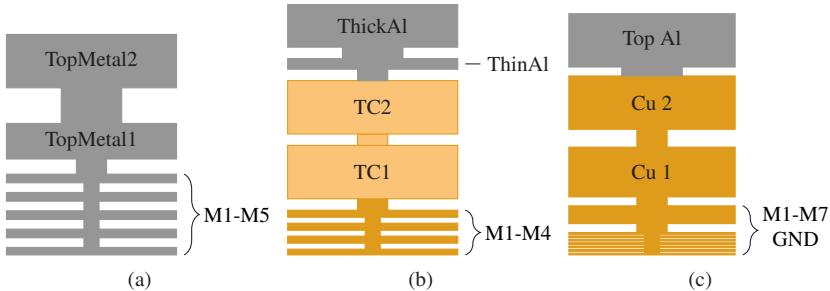

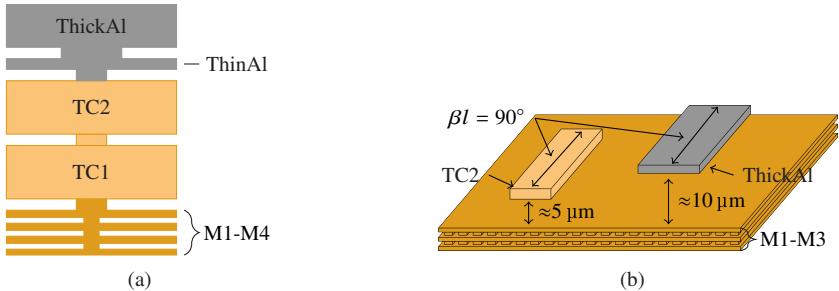

For the integration of passive structures and to contact the active devices the available metal layers in the BEOL are used. The composition of the layers influences the achievable performance. Fig. 1.9 illustrates the usable metal layers in the BEOL of the respective technologies. The illustrations are intentionally not to scale for propriety reasons, however the relative scale between the stacks is preserved. SG13G2 offers a total of 7 aluminum (Al) layers, of which the top two layers are thicker. To provide a ground connection the lower metal layers, M1 to M3, are stacked together, shielding the lossy Si substrate. Top-Metal1 and Top-Metal2 are then used for signal routing. SG13G2Cu provides 6 copper (Cu) layers and two Al layers. The lower Cu layers, M1-M3, are again

used as ground. Signal routing is possible in the thick Cu layers and in the top metal layer, ThickAl. This BEOL provides two advantages in comparison to the Al BEOL of the SG13G2 process. First, by providing three thick layers handling of large currents is simplified and secondly, the overall stack height is larger reducing losses and coupling to the lossy Si substrate. Lastly, the BEOL used in the 22 nm FD-SOI process is presented in Fig. 1.9c. It provides 6 thin metal layers, M1-M6, which are used to contact the transistors, but are too lossy for RF routing. Instead, M1-M7 are used as ground. By utilizing the first thicker metal the ground provides sufficient conductivity. Again, three thicker metal layers are available, of which two are Cu layers. Similar to SG13G2Cu, this BEOL enables better current handling capabilities and a larger total stack height.

Figure 1.9: BEOL illustrations for: a) IHP's SG13G2; b) IHP's SG13G2Cu/SG13G3Cu and c) GF's 22 nm FD-SOI. Illustrations are not to scale.

## 1.5 Thesis Goal and Outline

The goal of this thesis is to investigate fundamental PA design challenges at mmWave frequencies. A core part is developing and refining design techniques for optimization of CMOS and SiGe BiCMOS PAs at mmWave frequencies.

The first focus topic are efficient matching and power combining networks for highly parallelized transistor configurations. The target impedances to be matched are as low as  $10\Omega$ . Both LC-based matching for PAs with a single core and large TL-based power combining networks with up to 16 inputs are explored.

The main focus area is then set on device parallelization within the PA cores. The cause of PA core performance degradation during large device parallelization is analyzed and a method to improve performance in largely parallelized cores is introduced. This is pursued to enable efficient PAs beyond a saturated output power of 30 dBm.

Finally, an optimization method targeted at linear PAs is presented to bridge the gap from peak performance optimization to back-off optimization in communication scenarios.

## 2 Power Amplifier Basics

*Parts of the following chapter are based on and similar to content presented in [Cri06].*

A power amplifier's main objective is to deliver a specific output power into a load. The level of output power is determined by the respective application. The signal power,  $P$ , into a load depends on the amplitude of incident current,  $I_{\text{out}}$ , and amplitude of the voltage,  $V_{\text{out}}$ , across the load, as

$$P = \frac{1}{2} \Re \{ V_{\text{out}} \cdot I_{\text{out}}^* \}. \quad (2.1)$$

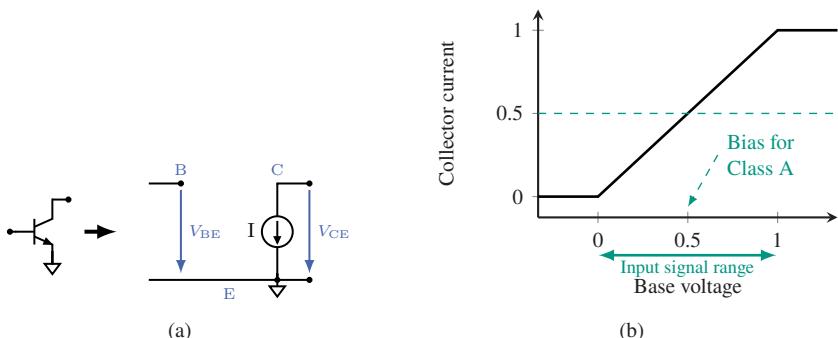

The voltage and current swing have to be provided by transistors operating as amplifiers. Important concepts of power amplification can be illustrated by observing the characteristics of a simplified and idealized representation of a transistor, as is shown in Fig. 2.1a. For simplicity only a bipolar device is

Figure 2.1: Idealized device characteristics for a transistor: a) ideal device model and b) idealized DC characteristic.

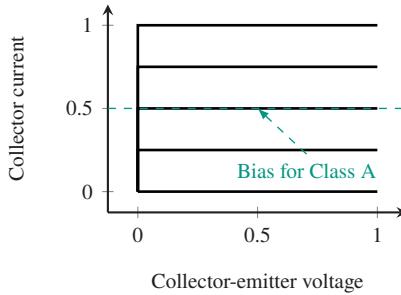

depicted, but for this analysis FET and bipolar transistors are identical. The transistor is modelled by a voltage controlled current source with a perfectly linear direct current (DC) characteristic within its operating limits, shown in Fig. 2.1b with normalized parameters. It is assumed that the transistor operation is permissible up to a maximum voltage,  $V_{\max}$ , across collector and emitter and a maximum collector current,  $I_{\max}$ . Both parameters are technology dependent. For simplification, no minimum voltage at the output, such as the knee voltage,  $V_{\text{knee}}$ , is required and ideal loading conditions are assumed. The resulting idealized output DC IV curve is depicted in Fig. 2.2.

Figure 2.2: Idealized output DC IV curve.

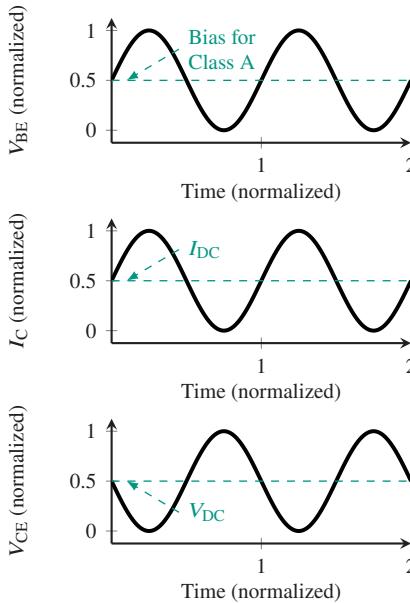

Under these conditions the theoretical concept of class A operation can be achieved by biasing the transistor at the operating point of  $V_{\text{CE},\max}/2$  and  $I_{\text{C},\max}/2$ . If the input signal drives the transistor to the limits, but not beyond a normalized base voltage of 0 or 1, the input signal is linearly amplified, illustrated in Fig. 2.3 for a sinusoidal excitation.

In this case, the output voltage and current swing have an amplitude of  $V_{\text{DC}}$  and  $I_{\text{DC}}$ , respectively. Thus, the output power,  $P_{\text{out}}$  is calculated to be

$$P_{\text{out}} = \frac{1}{2} V_{\text{DC}} \cdot I_{\text{DC}} \quad (2.2)$$

and the dissipated DC power,  $P_{\text{DC}}$  is

$$P_{\text{DC}} = V_{\text{DC}} \cdot I_{\text{DC}}. \quad (2.3)$$

Figure 2.3: Idealized class A operation.

By dividing the RF output power by the dissipated DC power, the PA's efficiency is calculated, and for the idealized case of the class A amplifier a theoretical efficiency,  $\eta = P_{\text{out}}/P_{\text{DC}}$  of 50 % is possible. This aspect of PA design is important. In a real amplifier, it is typically referred to as drain or collector efficiency,  $\eta_{\text{D,C}}$  and defined as

$$\eta_{\text{C}} = \frac{P_{\text{RF,out}}}{P_{\text{DC}}}. \quad (2.4)$$

A more meaningful approach to define efficiency for realistic circuits with limited gain is to subtract the required RF input power,  $P_{\text{RF,in}}$ , from the delivered output power yielding the power-added efficiency (PAE)

$$\text{PAE} = \frac{P_{\text{RF,out}} - P_{\text{RF,in}}}{P_{\text{DC}}}. \quad (2.5)$$

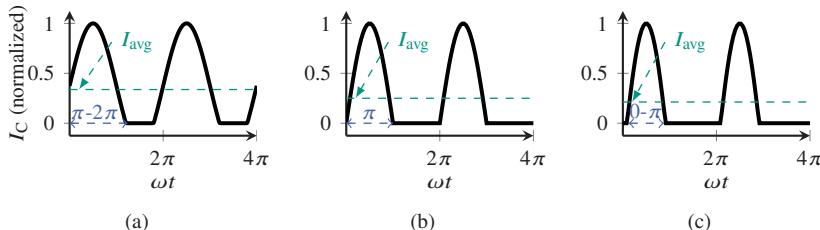

A theoretical efficiency higher than 50 % can be achieved by reducing the base bias voltage, which reduces the DC current consumption. As a consequence, parts of the output waveform are truncated. The three conventional modes beyond class A are class AB, B, and C. A typical way to differentiate between these classes is to use the conduction angle,  $\alpha$ , for which the transistor is conducting current. Conduction angle and theoretical efficiency limits are summarized in table 2.1 and idealized current waveforms are shown in Fig. 2.4. While in theory a higher efficiency is achieved, a lower bias point generates significant harmonic content due to the truncation of the output sine wave, and for the theoretical analysis an ideal short is assumed as the harmonic termination. Additionally, the theoretical signal power beyond class B deteriorates, resulting in higher efficiency at the cost of lower output signal strength and the required driving power is significantly increased (up to 6 dB for class B). When this is taken into account PAE may not improve accordingly in practical cases.

Table 2.1: Summary of theoretical performance for basic classes of operation.

| Class                             | A      | AB           | B     | C          |

|-----------------------------------|--------|--------------|-------|------------|

| Conduction angle $\alpha$         | $2\pi$ | $\pi - 2\pi$ | $\pi$ | $0 - \pi$  |

| Theoretical efficiency $\eta$ (%) | 50     | 50 - 78.5    | 78.5  | 78.5 - 100 |

Figure 2.4: Ideal current waveforms for theoretical classes of operation: a) class AB; b) class B and c) class C.

At mmWave frequencies, generating sufficiently large output power remains one of the major challenges for PA design in CMOS and SiGe BiCMOS technologies. This is mainly attributed to the low open-base breakdown voltage,  $BV_{CEO}$ , limiting the possible voltage swing across a basic transistor setup,

---

as presented before. The maximum output power that can be delivered by the idealized transistor is

$$P_{\max} = \frac{1}{2} \frac{V_{\text{CE},\max}}{2} \cdot \frac{I_{\text{C},\max}}{2}. \quad (2.6)$$

The corresponding load resistor,  $R_{\text{opt}}$ , is calculated using the load-line method [Cri06]. The load impedance is selected such that the maximum voltage swing is reached at maximum current swing. In the case of the previously presented ideal transistor, this is

$$R_{\text{opt}} = \frac{V_{\text{CE},\max}}{I_{\text{C},\max}}. \quad (2.7)$$

Since the theoretical limit for the amplitude of the output voltage swing,  $V_{\text{peak}}$ , is equivalent to the supply voltage or half the maximum collector emitter voltage, this limits what a transistor can deliver into a load resistor, as

$$P = \frac{1}{2} \frac{V_{\text{peak}}^2}{R}. \quad (2.8)$$

For a conventional load resistance of  $50 \Omega$  and a supply voltage of  $1.5 \text{ V}$  this amounts to approximately  $13 \text{ dBm}$ . To further extend the output power the optimal load resistance must be lowered. At the same time, the active device size needs to be increased to provide sufficient current swing. When a saturated output power of  $30 \text{ dBm}$  is targeted the optimal load resistance is calculated to be  $1.1 \Omega$ , by rearranging equation 2.8 to

$$R = \frac{1}{2} \frac{V_{\text{peak}}^2}{P}. \quad (2.9)$$

At mmWave, a load resistance this low is susceptible to parasitics and incurs high losses inside the matching network. This will reduce the amplifier's efficiency.

## 2.1 Transistors, Topologies and Challenges for Millimeter-Wave Silicon Power Amplifiers

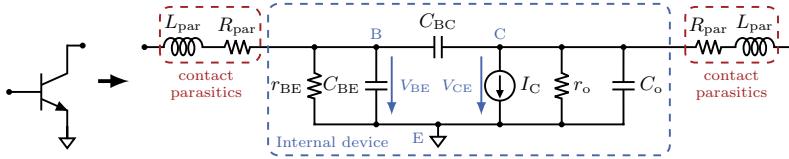

A more realistic model of an HBT operating at mmWave frequencies is presented in Fig. 2.5. Parasitic capacitors at input and output reduce the impedances of the transistors, even for relatively small transistor sizes. Low impedances increase the influence of parasitics and result in higher matching network loss. A feedback path is introduced into the circuit by the collector-base capacitor,  $C_{BC}$ . During operation with high voltage gain, which is desirable for PAs, this capacitor's effect on the input is enhanced by the Miller effect. Parasitic resistors, introduced by the device contacts, directly affect transistor performance and prevent perfect compensation of the internal device capacitors by resonating inductors. Transistor performance is thus reduced with increasing frequency. Lastly, the transistor's output current as a function of  $V_{BE}$  is generally not linear, but either exponential for HBTs or quadratic for FETs [Sze81].

Figure 2.5: Simplified high-frequency transistor model.

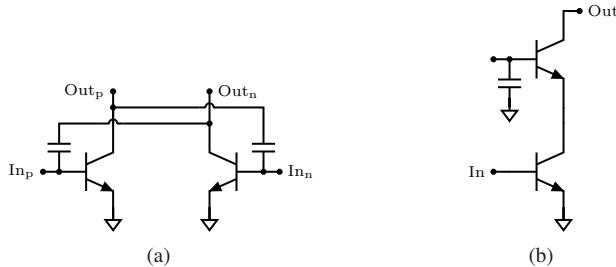

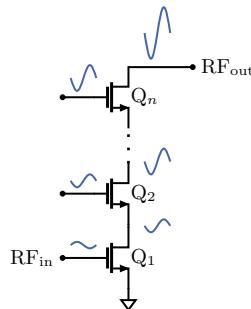

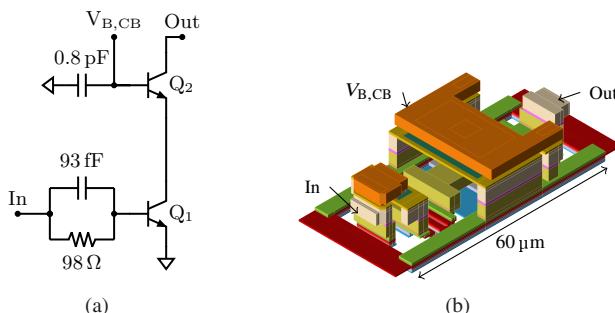

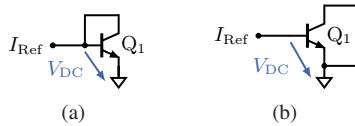

The enhanced Miller effect of transistors in a basic CE configuration is one of the reasons, which makes more advanced amplifier topologies preferable. The two most prevalent topologies are neutralized differential pairs and the cascode, or a combination of both, e.g., in [LW23, WW20b, WWW20]. Additionally, transistor stacking, often used [DHG<sup>+</sup>13] with FETs, allows for higher voltage swing. The first two options are displayed in Fig. 2.6.

The neutralized differential pair contains neutralization capacitances to compensate the feedback from the output back to the input. However, it is not pursued further throughout this work, as the implementation of the neutralization capacitors for large device peripheries is challenging and restricts the layout geometry. The cascode adds a second device in CB configuration, which provides a low load impedance to the CE stage. The CE's voltage gain is thus decreased, ideally to 1, and the feedback due to the collector-base ca-

Figure 2.6: Advanced transistor arrangements for power amplification: a) neutralized differential pair and b) cascode.

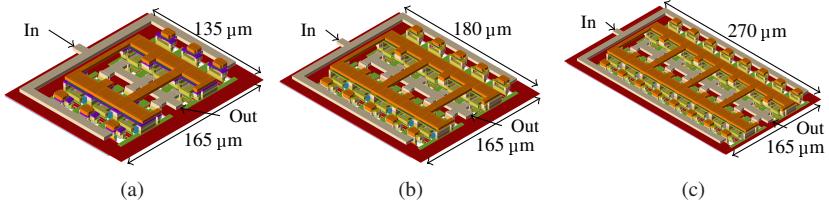

pacitance reduced. The cascode provides additional advantages over a simple CE configuration, such as higher input impedance, higher output impedance combined with higher gain, increased optimal load impedance and increased voltage swing. While a CE is limited by  $BV_{CEO}$ , the CB device is limited by the open-emitter breakdown voltage,  $BV_{CBO}$  [ORW<sup>+</sup>15, CSC<sup>+</sup>11]. A 130 nm SiGe technology used throughout this work features a  $BV_{CEO}$  of 1.6 V and a  $BV_{CBO}$  of 4.8 V. Following [ORW<sup>+</sup>15], the CB device can be operated with a collector-base voltage,  $V_{CB}$ , of 2.4 V ( $BV_{CBO}/2$ ) and during compressed operation RF swing across collector and emitter is allowed slightly beyond  $BV_{CBO}$ . To allow for operation close to the optimal value of  $BV_{CBO}$  the upper base must have a low ohmic termination. When the transistor is biased beyond  $BV_{CEO}$  current reversal into the base would otherwise increase the voltage inside the device's base. This could lead to localized current increase inside the device, leading to a further increase of base voltage. This could lead to the destruction of the device. The analysis in [ORW<sup>+</sup>15] did not account for mutual heating of the CE and CB device. Hence, appropriate measures, such as resistive emitter degeneration, ballasting or bias circuits, are required to stabilize the current set by the CE device. Using an idealized cascode arrangement with an assumed voltage swing amplitude of 3.5 V and an optimal load resistor of  $50\Omega$  an output power of 20.8 dBm is possible. Still, to achieve 30 dBm of output power, a low load resistance of  $6.1\Omega$  is required.

In a realistic high-frequency scenario, transistors are not purely resistive, and a reactive component has to be compensated. Additionally, the voltage swing amplitude is going to be smaller than the supply voltage. Finally, large device parallelization comes at the cost of increased parasitics. Ultimately, the PA's performance is further reduced.

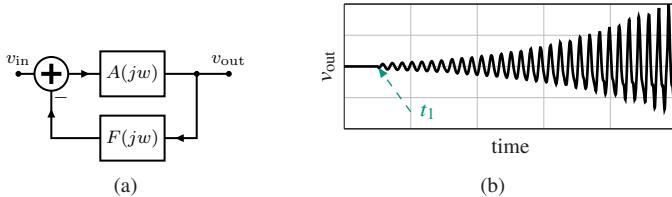

## Stability

Besides delivering power, stability and the associated analysis is one of the major challenges of PA design. Due to the aforementioned parasitics, inherent to the transistor itself, but also due to the added geometries during layout, feedback paths inside an amplifier design can lead to instability. To briefly summarize amplifier instability, Fig. 2.7 illustrates a simplified diagram of an amplifier split into a forward gain block ( $A(j\omega)$ ) and a feedback gain block ( $F(j\omega)$ ). Following the Barkhausen stability criterion, the amplifier can oscillate for  $|A(j\omega)F(j\omega)| \geq 1$  and  $\angle A(j\omega) + \angle F(j\omega) = 2n\pi$  [Beh11].

Figure 2.7: RF amplifier stability: a) generalized block diagram and b) unstable transient response to a short broadband pulse at  $t_1$ .

At low frequencies, the transistors' gain is high and attenuation from a real circuit's output to its input may be smaller. Additionally, it is challenging to avoid the phase condition for oscillation for every frequency between DC to  $f_{\max}$ . Without preventive measures, an oscillation can occur. This may compress the amplifier and cause unwanted output signals, performance degradation and could lead to failure of the devices. Fig. 2.7b shows the output voltage of an unstable amplifier versus time, after a short pulse was excited at the input at  $t_1$ . Due to the unstable behavior the amplifier is unusable. To predict unstable operation, amplifiers require careful stability analysis both in small- and large-signal operation [TVU24b]. Suitable methods to prevent the unstable behavior, for example adding resistors, can then be evaluated

Since determining the complete transfer function of a real RF amplifier is impractical, the Barkhausen criterion is not used. Throughout this work, the following methods are used to analyze stability. First, small-signal stability analysis using Rollett's  $K$ -factor [Rol62] is performed during the whole design phase. It is used as a first evaluation of the PA core and sub-block stability. However, in more complicated designs  $K$ -factor analysis delivers limited insight, as

it is only limited to small-signal operation and treats the PA as a single two-port block. To extend  $K$ -factor analysis a bias sweep is performed for the PAs presented in this thesis. By analyzing the PA's  $K$ -factor for different operating conditions, as they would occur during a large-signal period, a first estimate on large-signal stability can be established. Still, by treating the PA as a two-port blackbox unstable behavior can be missed. Thus, transient simulations are used to verify stability for the finished designs. To do so, a broadband pulse is excited at each terminal, RF and DC, and the response is observed.

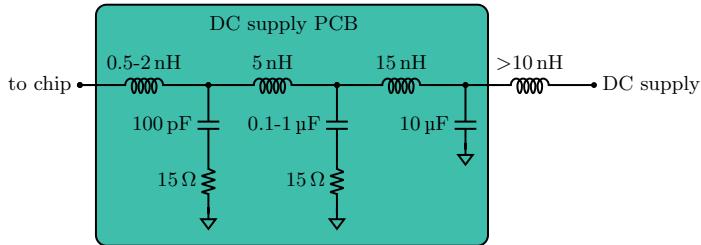

To ensure stability, most PAs in this work are assembled on printed circuit boards (PCBs) for DC supply, including additional soldered capacitors at the DC terminals, which is a general method for stabilization [Cri06]. To suppress low-frequency oscillations, all designs utilize a parallel  $RC$ -element at the RF input of their cores to ballast the transistors and attenuate low-frequency signals.

## Linearity versus Efficiency

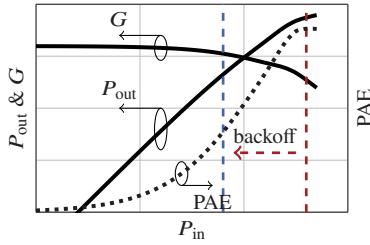

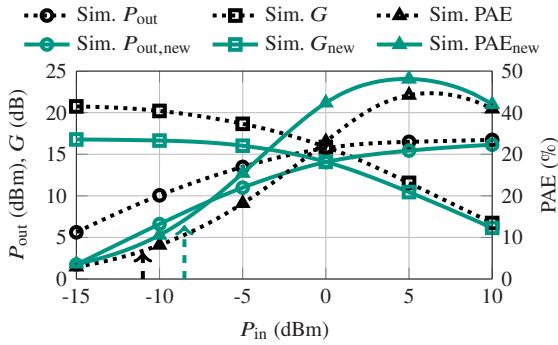

In modern communication, complex single carrier modulation schemes such as 64- and 256-QAM are used in conjunction with multi carrier methods such as orthogonal frequency-division multiplexing (OFDM) [WAF21]. While using these modulation schemes guarantees efficient usage of the available spectrum, their high PAPR puts extensive linearity requirements on the PAs. Due to the non-linear behavior of PAs in compression a power back-off of several decibels, depending on the respective PAPR, is required and results in a lower average performance. Fig. 2.8 illustrates a PA's typical large-signal performance over input power, as well as the effect of power back-off on the performance. In this example, the PA's PAE at back-off is less than half its peak value.

Table 2.2 presents a summary of key parameters for different modulation schemes for a root-raised-cosine-filter with a roll-off factor,  $\alpha$ , of 0.35. QAM requirements are according to 5G NR [VMR17, WAF21], APSK based on SatCom DVB-S2 [TVU24b].

To analyze the signal quality after amplification by a PA, root mean square (RMS) error vector magnitude (EVM) is used. It is defined as the RMS value

Figure 2.8: PA large-signal performance with power back-off illustration.

Table 2.2: Summary of modulation scheme parameters [VMR17, WAF21, TVU24b].

| Const.  | PAPR (dB) | EVM <sub>RMS</sub> (%) | EVM <sub>RMS</sub> (dB) |

|---------|-----------|------------------------|-------------------------|

| 16-QAM  | 6.6       | 12.5                   | -18                     |

| 64-QAM  | 7.7       | 8                      | -22                     |

| 256-QAM | 8.2       | 3.5                    | -29                     |

| 16-APSK | ≈7        | ≈15                    | -16.5                   |

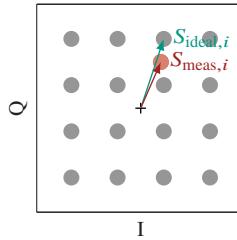

of the error vector,  $A_{\text{error,RMS}}$ , over the RMS value of the constellation point magnitudes,  $A_{\text{ideal,RMS}}$ , [VMR17]

$$\text{EVM}_{\text{RMS}} = \frac{\sqrt{\frac{1}{N} \sum_{i=1}^N |S_{\text{ideal},i} - S_{\text{meas},i}|^2}}{\sqrt{\frac{1}{M} \sum_{i=1}^M |S_{\text{ideal},i}|^2}} = \frac{A_{\text{error,RMS}}}{A_{\text{ideal,RMS}}}. \quad (2.10)$$

Fig. 2.9 shows an example constellation diagram for 16-QAM, indicating the ideal ( $S_{\text{ideal},i}$ ) and measured ( $S_{\text{meas},i}$ ) vectors. The errors are for example caused by AM-AM, e.g., gain compression, and AM-PM characteristics of the PAs, especially affecting symbols with large amplitude.

Figure 2.9: Normalized constellation diagram for a 16-QAM signal (similar to [VMR17]).

## Thermal Management

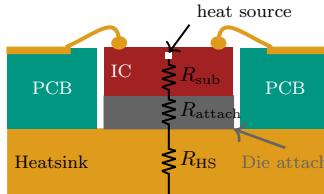

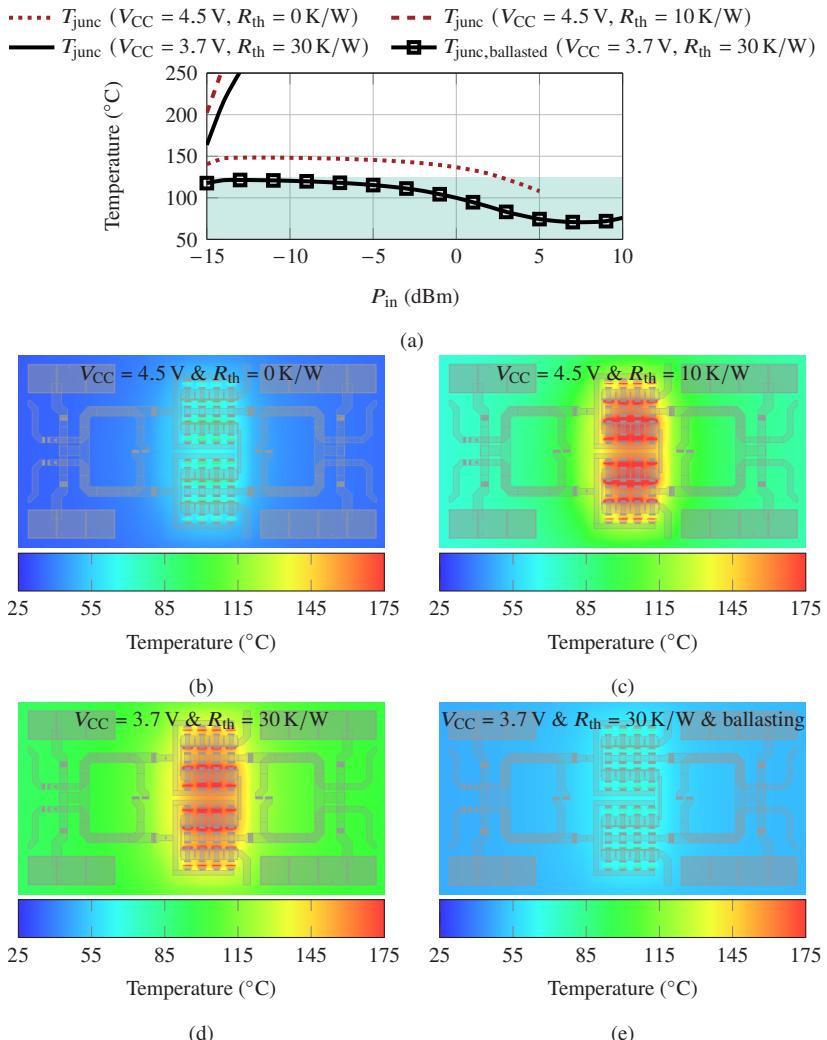

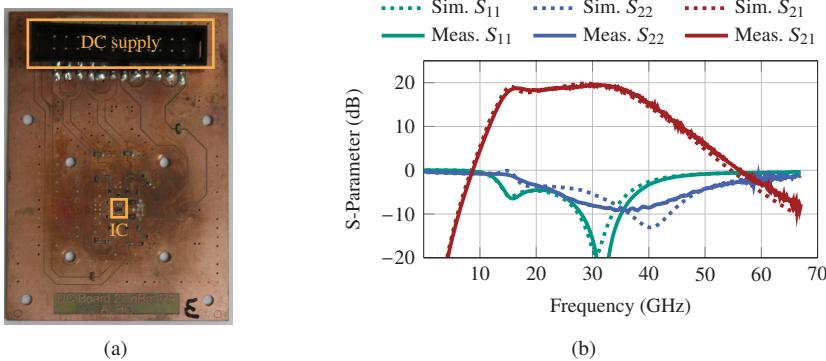

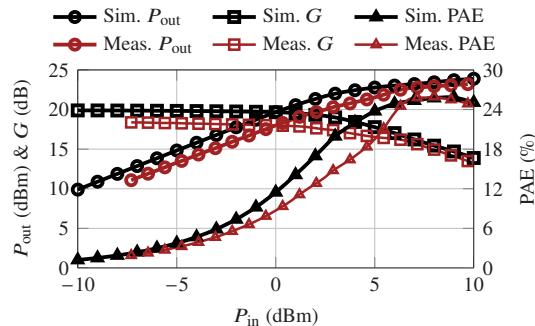

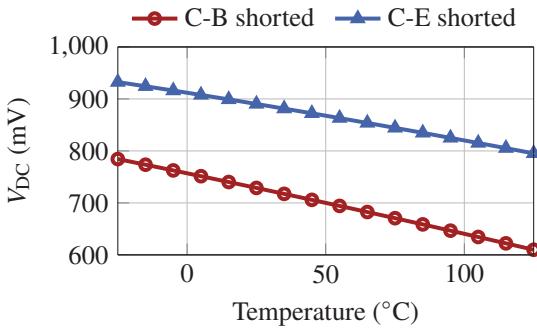

Thermal management of PAs, especially for higher power levels, is critical to ensure high RF performance. First, the chip area in which DC power is dissipated is small and secondly at higher frequencies the efficiency of PAs is generally lower and in relative terms more power is dissipated. This can cause high temperatures in the chip and might lead to thermal runaway and failure of the chip. Furthermore, in some applications, such as SatCom, the amount of heat transfer is limited, as no heat transfer by convection or conduction to the environment of the satellite is possible. One aspect to simplify thermal management is to achieve high efficiency during large-signal operation. This reduces the amount of dissipated power per delivered RF power. Still, to prevent performance deterioration heat must be transferred from the active devices to a heatsink. [Bah09] shows a 12 W HPA losing 0.4 dB output power for a 1 ms pulse compared to a 10  $\mu$ s pulse, highlighting the severity of the problem. In this work Si-based technologies are used. The silicon substrate has a relatively high thermal conductivity,  $k_{\text{Si}}$ , of  $145 \text{ W m}^{-1} \text{ K}^{-1}$  [Bah09], enabling good heat conduction away from the active devices. However, this mandates a die attachment with sufficient heat conduction to ambient temperature at the chip bottom. Otherwise, the overall chip temperature may rise significantly. A thermal resistance,  $R_{\text{th}}$  is used to model the transition from chip to heatsink. In this work, for any off-chip interface (e.g., heatsink or die attach) equal heat transfer distribution and even surfaces, without any voids, are assumed. The thermal resistance of a structure can then be simplified to

$$R_{\text{th}} = \frac{h}{A \cdot k}, \quad (2.11)$$

where  $h$  is the height,  $A$  the interface area (e.g. the chip area) and  $k$  the thermal conductivity of the respective material. Fig. 2.10 illustrates a basic thermal package model used throughout this work. The on-chip thermal resistance can be extracted using electrothermal co-simulation, for example using Keysight's Advanced Design System (ADS). This also includes thermal coupling between individual devices. In later chapters, two example SiGe BiCMOS PAs are presented highlighting the importance of thermal simulation, management and its influence on PA performance.

Figure 2.10: Basic thermal model used throughout this work.

### 3 Optimization of LC-based Output Matching Network Design

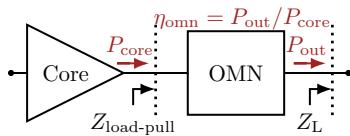

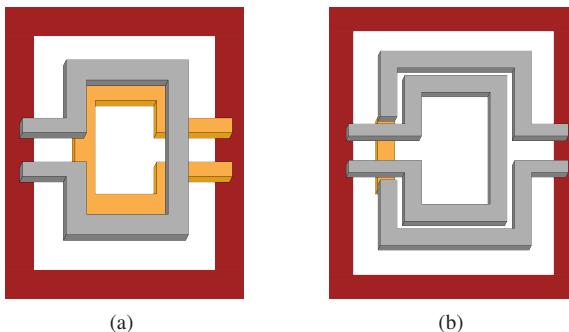

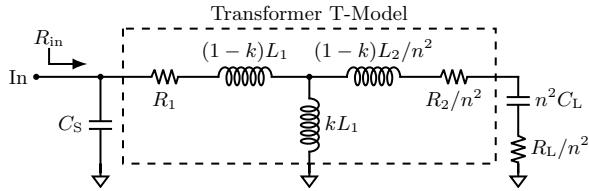

A critical aspect of PA design is the output matching network (OMN). The OMN has to transform the load impedance, commonly referred to as  $Z_L$  or  $Z_{load}$ , to the load-pull impedance,  $Z_{LP}$  or  $Z_{load-pull}$ , of the PA core. This is illustrated in Fig. 3.1. The OMN's efficiency,  $\eta_{omn}$ , relating the power delivered by the PA core to the OMN,  $P_{core}$ , to the power delivered to the load,  $P_{out}$ , directly influences the achievable performance of the PA in terms of output power and PAE. The bandwidth associated with the PA is also limited in part by the bandwidth of the OMN. Additionally, DC feeding and blocking have to be facilitated inside the network. Different approaches for matching networks exist, for example resistive matching, reactive LC-based matching and TL-based matching networks. While resistive matching offers a simple and generally broadband solution, it is impractical in PA design, when a high efficiency and output power are desired. For TL-based matching, the physical length of the TLs scales inversely with frequency, thus a TL-based matching network consumes a significant amount of chip area below a frequency of about 50 to 80 GHz. A combination of both resistive and TL-based matching is used in distributed amplifiers to achieve broadband amplification. However, even when no extra DC power is dissipated on the resistors, literature examples achieve peak PAE values of only 20 % for an output power of 20 dBm at  $K_a$ -band [LFCE18]. Lastly, transformers are a popular solution achieving high network efficiency,

Figure 3.1: PA output matching overview. ©IEEE

especially in differential-to-differential cases. Still, transformers require specific physical geometries and in case of a high transformation ratio between  $Z_L$  and  $Z_{LP}$  a higher turn ratio than 1:1, which may reduce efficiency.

In contrast, LC-based matching networks feature very high integration density even at lower frequencies between  $K_u$ - and  $W$ -band as well as high efficiency. In this chapter, the efficiency driven design of LC-matching networks is investigated for implementation in SiGe BiCMOS BEOLs at mmWave frequencies. Two prototype PAs using optimized network topologies are then presented.

### 3.1 Efficiency Optimization of LC-Matching Networks

*Parts of the following content are published in [8].*

LC-based matching networks utilize lumped components, capacitors and inductors, to facilitate the transformation between two impedances. During the design phase of LC-based matching networks the imperfections of network components are usually neglected. At lower frequencies, this assumption may result in good performance, however the chosen network topology may not be the most efficient solution. This becomes more important as frequency increases and the impedances to be matched decrease. A plethora of analytical and numerical LC matching network optimization techniques including network losses have been previously published, for example in [CS18, HXW21, HP06, AKRH02]. These methods typically treat the optimization from a general point of view by simplifying the component imperfections to constant quality factors and by allowing for an unlimited number of components and component values. Thus, the practical insight for the designer is limited.

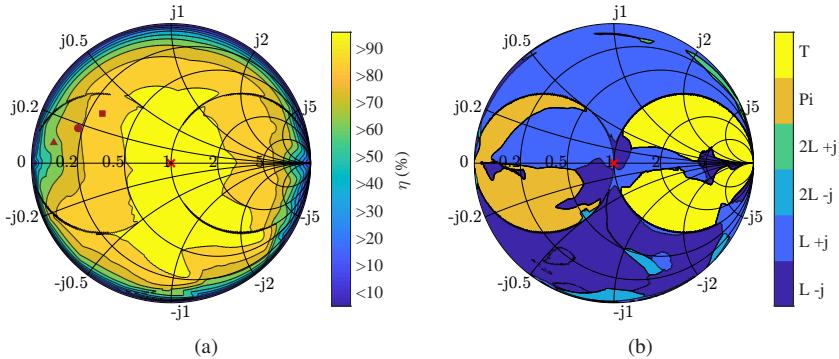

The goal of the following analysis is to accurately predict matching network loss before design implementation and to find network topologies optimizing the network's efficiency. An analytical solution to this problem appears impractical, as the number of possible network topologies is too large. Instead, an exhaustive search is pursued. Additionally, for this study the number of possible network components is limited. While an arbitrary number of components is possible and state of the art suggests performance improvements, implementation of a network with many components consumes significant chip area and unavo-

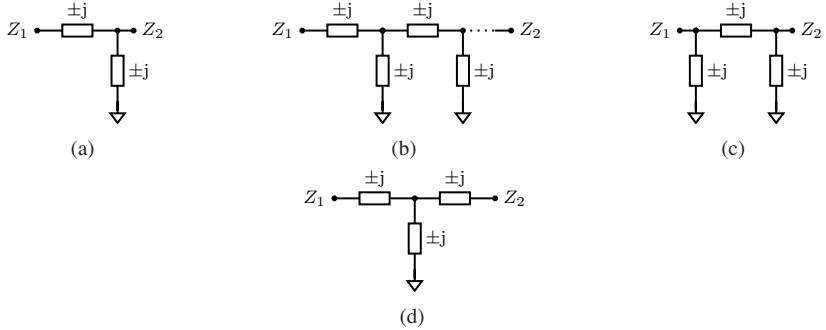

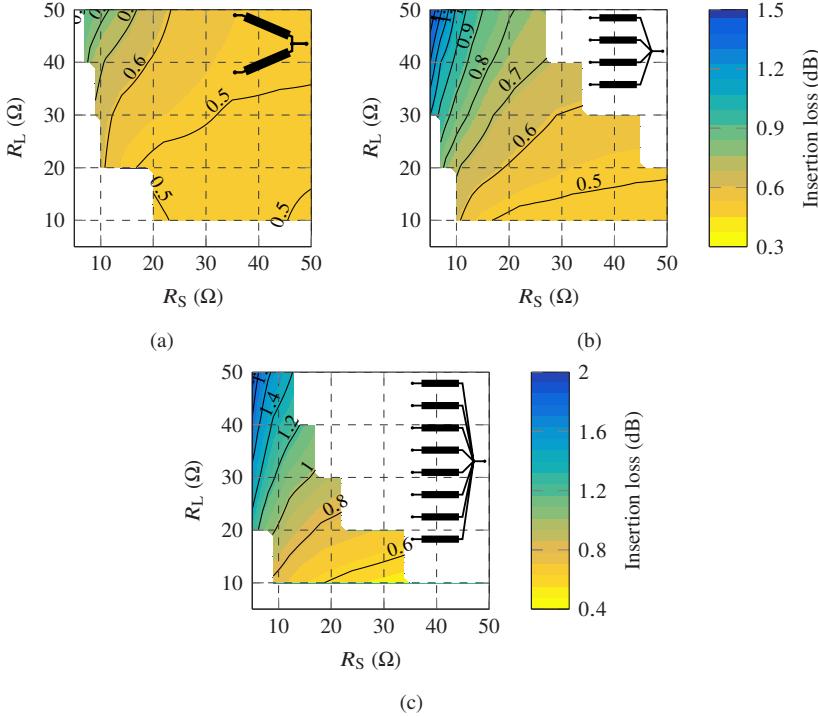

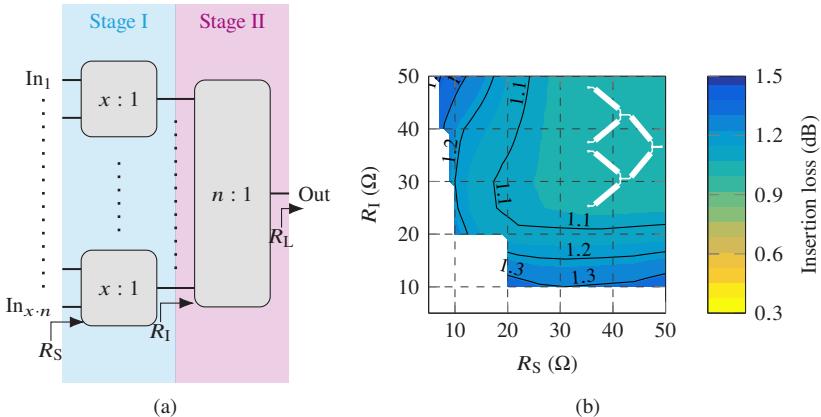

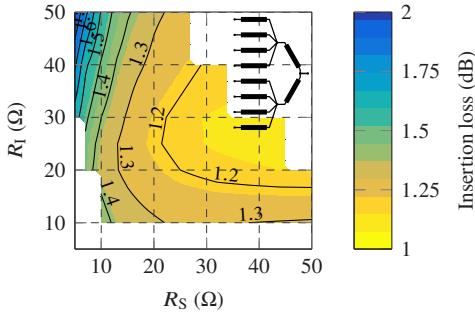

dable parasitics during implementation may reduce final network efficiency. Consequently, a simpler solution may be preferred. The network configurations investigated are L-, cascaded L-, Pi- and T-networks, as illustrated in Fig. 3.2.

Figure 3.2: LC-based matching network topologies: a) L-network; b) cascaded L-networks; c) Pi-network and d) T-network.

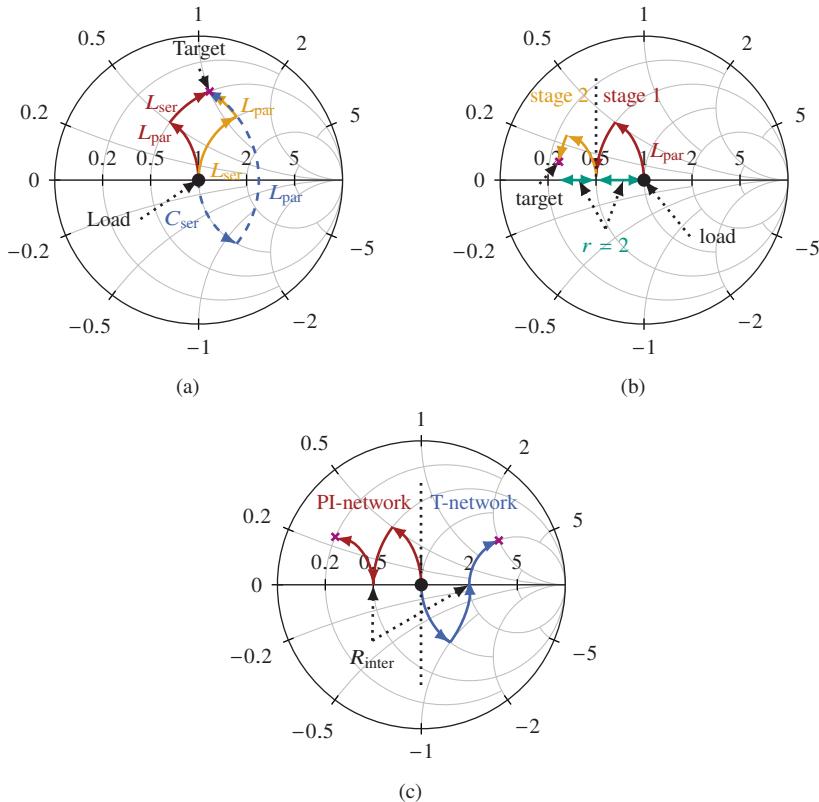

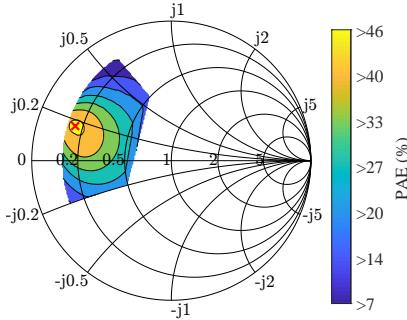

To choose the optimal topology depending on the required load-pull impedance, all possible network topologies are compared for the target  $Z_{LP}$  and then the most efficient topology is selected. To move beyond state of the art, the components inside the networks are more accurately modelled by including size dependent quality factors and a quality factor reduction for DC feeding inductors. To calculate the necessary network component values for a load and load-pull impedance combination ( $Z_L, Z_{LP}$ ), the following guidelines are used. The load impedance is assumed to be  $50\Omega$  and the starting point for the transformation. For L-networks the required component values can be directly calculated from the impedance pair. However, depending on the load-pull impedance different network arrangements can be used. This is illustrated in Fig. 3.3a. Three different example L-network transformation paths are shown in a Smith chart to reach the same  $Z_{LP}$ .

When multi-stage L-networks are investigated, the calculation of the network components is simplified to individual L-network stages, by choosing intermediate impedances between the network stages. The choice of the intermediate impedance influences the network efficiency and component values. The intermediate impedances are chosen to have equal transformation ratio,  $r$ , for the real part per stage and linearly adjust the imaginary part between  $Z_L$  and  $Z_{LP}$ .

Figure 3.3: LC-based matching network Smith chart transformation paths: a) L-network; b) cascaded L-networks and c) PI- & T-network.

per stage. This is illustrated in Fig. 3.3b. In the example shown, the normalized real part is transformed from 1 to 0.5 in the first stage, and from 0.5 to 0.25 in the second stage. The ratio,  $r$ , is 2 for both stages. The normalized imaginary part is linearly adjusted, by first transforming from 0 to 0.05 in the first stage and then from 0.05 to 0.1 in the second stage.

For PI- and T-networks, the first two components connected to the load form an L-network transforming the load to a real intermediate impedance,  $R_{\text{inter}}$ . The last component is used to compensate for the imaginary part of the targeted

load-pull impedance. This is shown in Fig. 3.3c for a PI- and T-network. As a consequence, PI- and T-networks can only reach impedances within the  $G = 1$  and  $R = 1$  circles, respectively. Using these guidelines to construct the transformations all component values within the networks can be calculated.

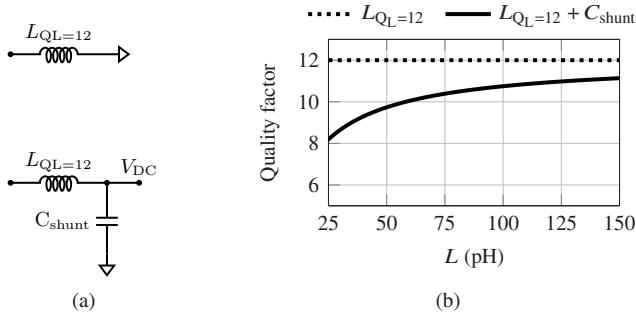

When a matching network is used at a PA output, a shunt inductance within the matching network is essential for efficient and convenient DC supply. A DC feeding shunt inductor requires a large parallel capacitor to ground at the DC supply node to ensure sufficient high-frequency termination. At mmWave frequencies these capacitors influence the overall quality factor of the used inductor. As an example, this is shown in Fig. 3.4. A varying inductance with a quality factor of  $Q_L = 12$  is combined with a lossy and finite parallel capacitor at 28 GHz. The used capacitor has a value of 5 pF and a quality factor of  $Q_C = 15$ . The negative effect on the quality factor is especially noticeable for small inductance values, which are required when the impedances become small, e.g., at a PA output. In the following analysis this effect is included for the first shunt inductance in the matching network.

Figure 3.4: Quality factor of DC feeding inductors at 28 GHz: a) schematic and b) quality factor versus inductance. ©IEEE

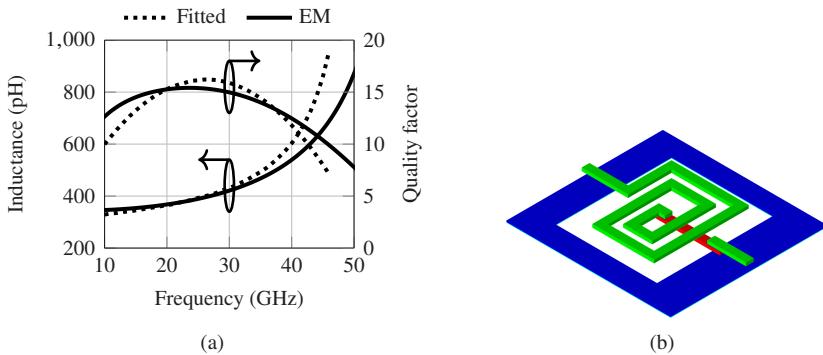

To determine the quality factor depending on component value and if the component value is below the self-resonant frequency (SRF) a curve fitting approach is used. As the basis for the curve fitting 9 example inductor and 7 example capacitor layouts are evaluated using electromagnetic (EM) simulation with their values ranging from 30 to 1500 pH and 28 to 1200 fF at 28 GHz, respectively. Based on these results, the following basic functions are used to model inductors

$$L(f) = a \left( b + \frac{1}{SRF - f} \right), \quad (3.1)$$

$$Q_L(f) = a - b(f - c)^2, \quad (3.2)$$

for which  $a$ ,  $b$ ,  $c$  and SRF are interpolated between the example layouts. For capacitors

$$C(f) = \left( ae^{bf \cdot \frac{1}{GHz}} + c \right) \text{fF}, \quad (3.3)$$

$$Q_C(f) = \left( a_Q e^{b_Q f \cdot \frac{1}{GHz}} + c_Q \right), \quad (3.4)$$

is used to model capacitance and quality factor. Again,  $a$ ,  $b$ ,  $c$  are interpolated between the results and differ from the constants used for the inductors. Fig. 3.5 compares the EM simulated and fitted results for an example inductor, showing good agreement.

Figure 3.5: Inductor modelling: a) Comparison of EM simulated and fitted results and b) corresponding 3D EM model. ©IEEE

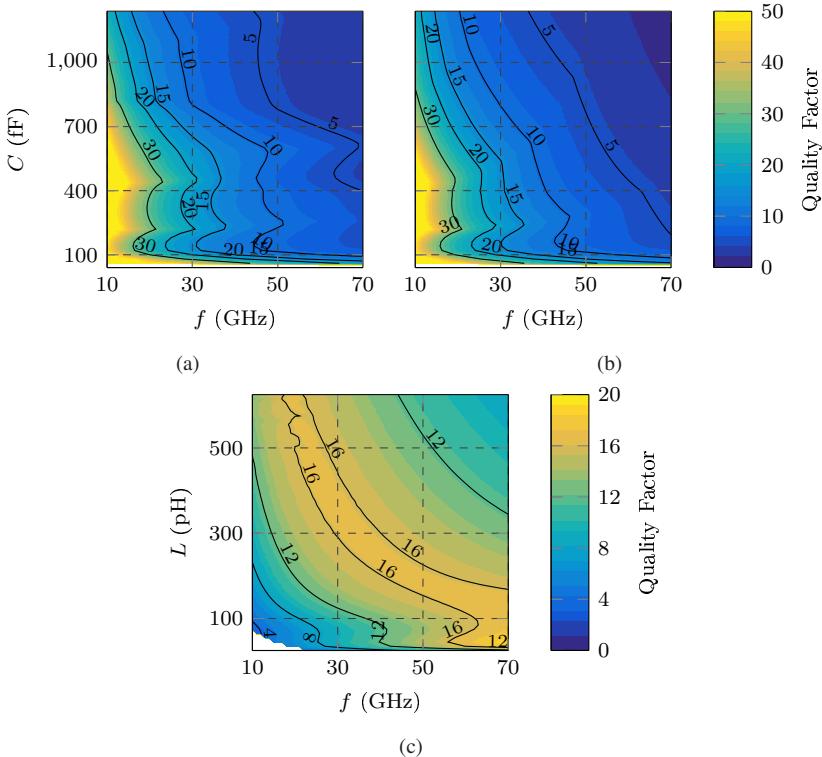

Based on the fitted results, quality factors accurately correspond to the component values. To illustrate this, Fig. 3.6 presents three maps of component size over frequency color-coded by the expected quality factor at each point

for series capacitors, shunt capacitors and inductors (either in shunt or series). The maps highlight that inductors tend to decrease in quality factor for very large or very small values. Capacitor quality factor decreases primarily with size, meaning decoupling capacitors will show a low quality factor. These maps must be recreated for varying frequencies of interest and technologies. By first calculating the required network component values and then using the presented component maps, the network performance can be accurately predicted w.r.t. network efficiency and bandwidth.

Figure 3.6: Capacitance and inductance versus frequency color-coded by expected quality factor for IHP's SG13G2Cu BEOL: a) shunt capacitors; b) series capacitors and c) inductors (series or shunt).

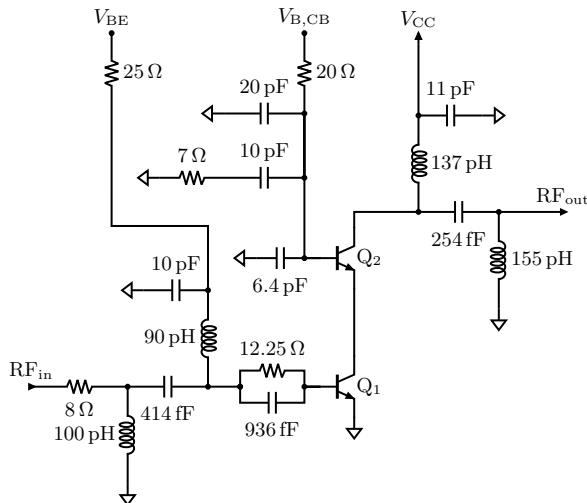

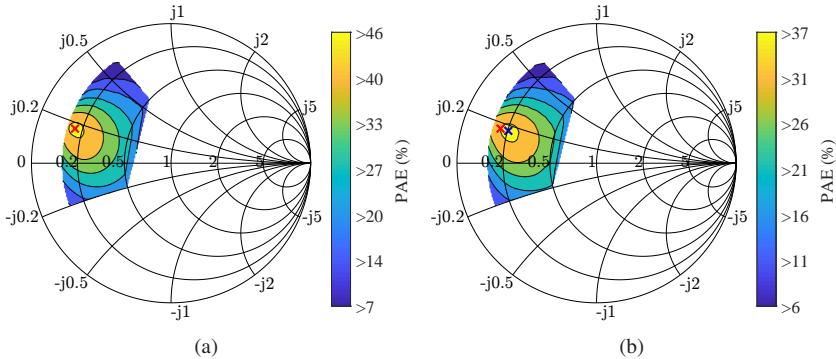

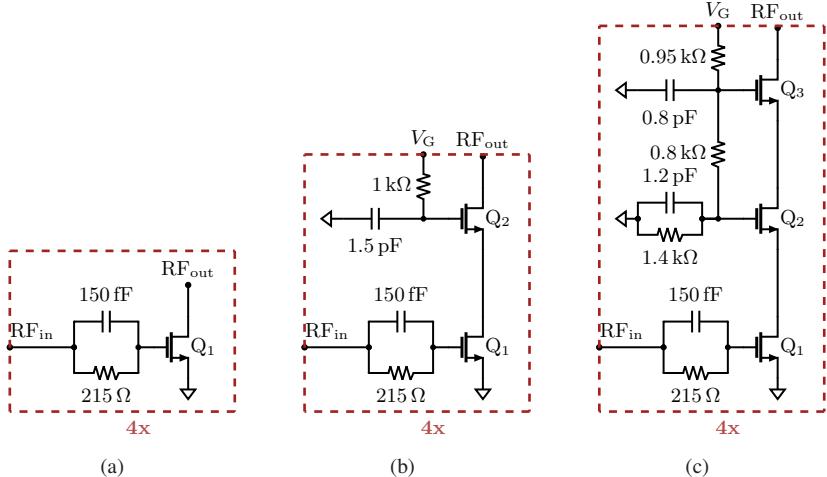

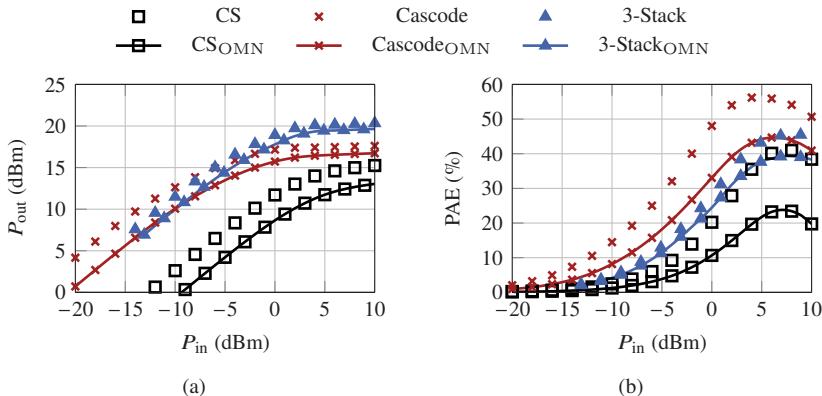

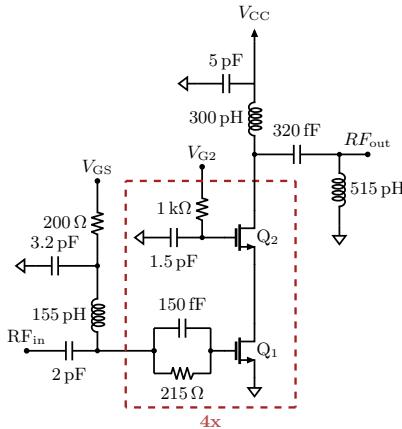

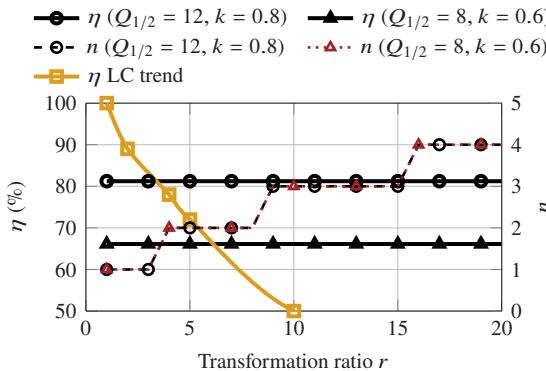

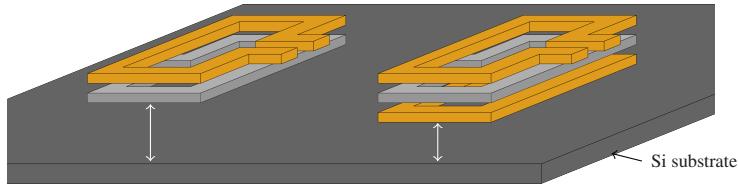

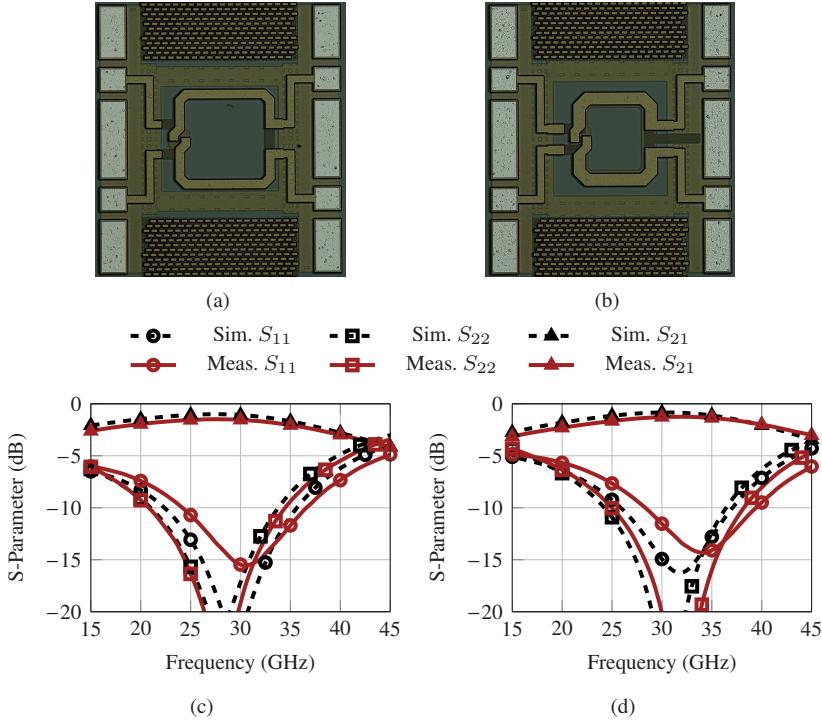

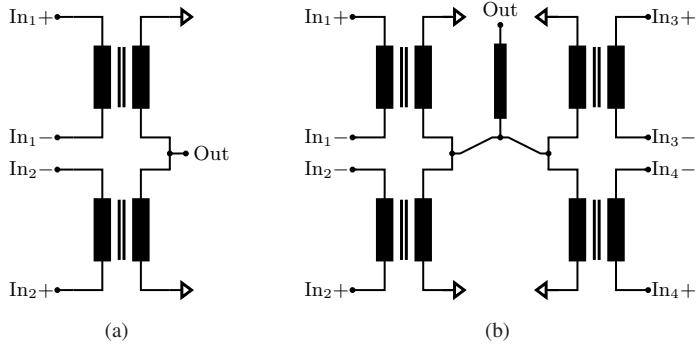

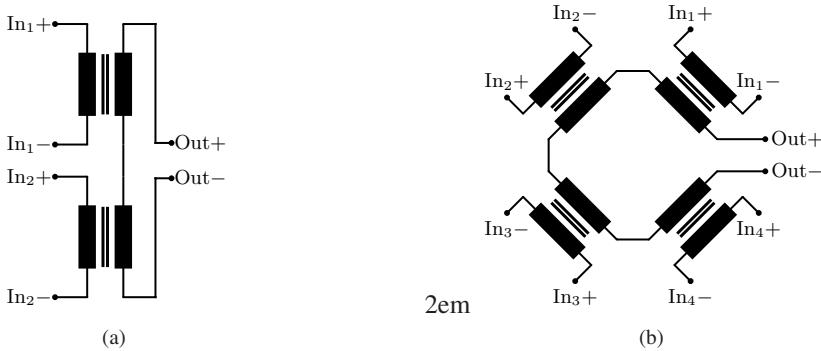

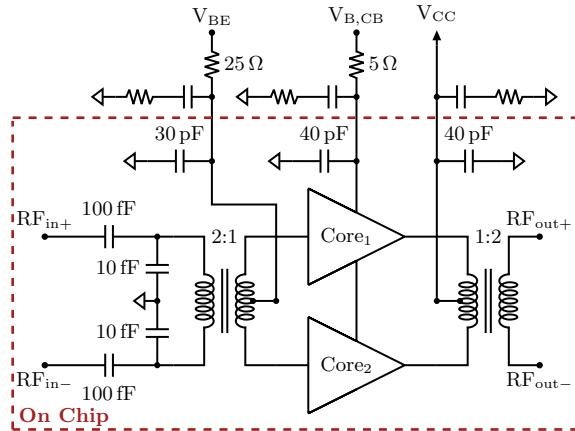

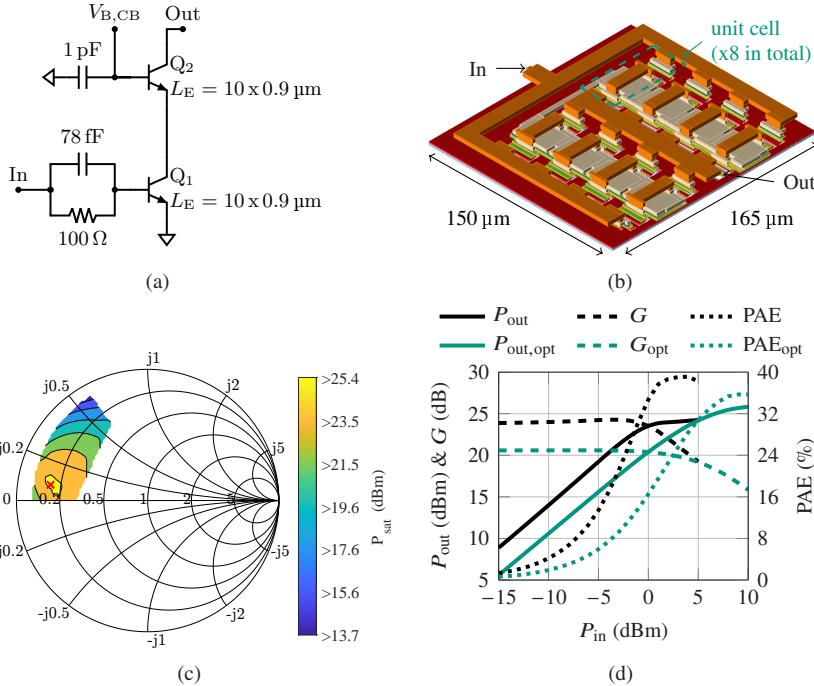

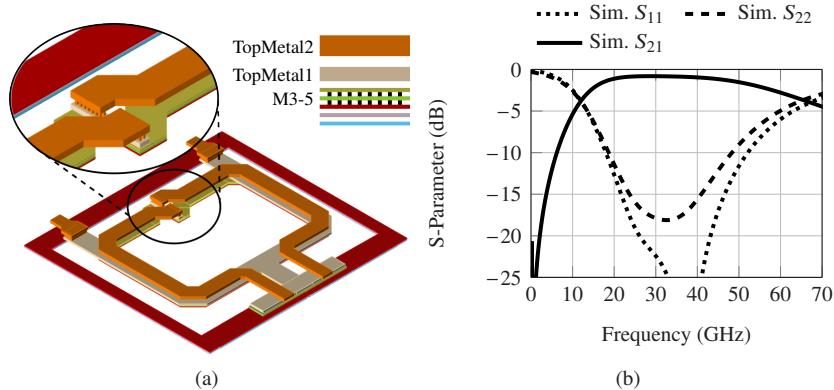

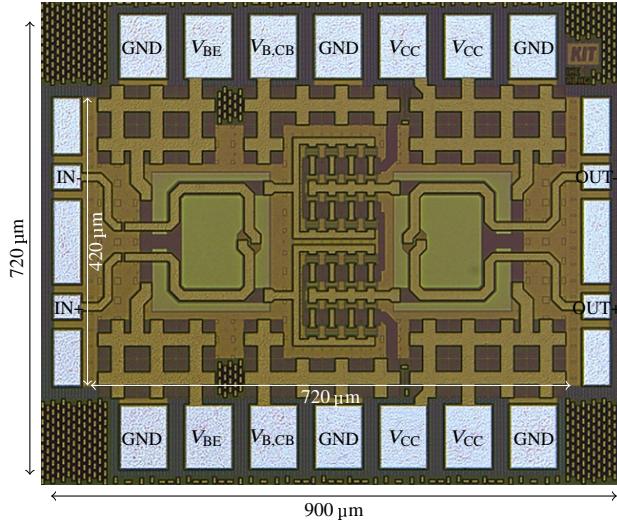

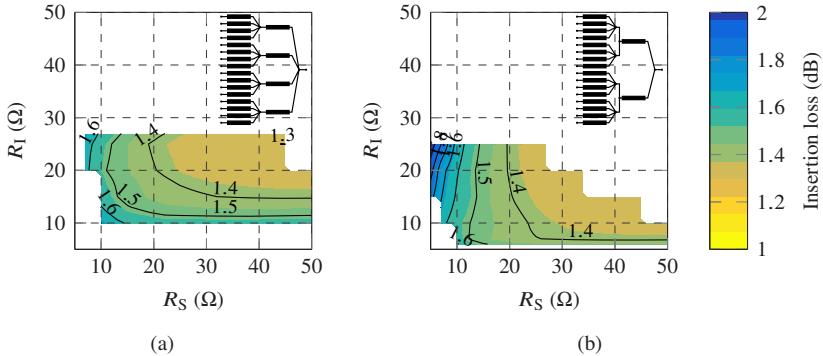

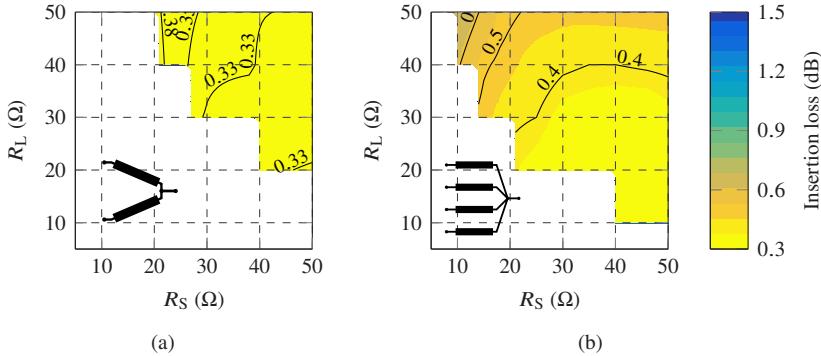

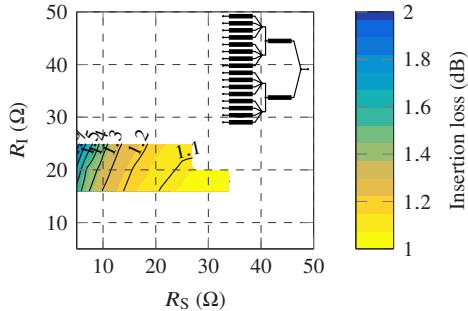

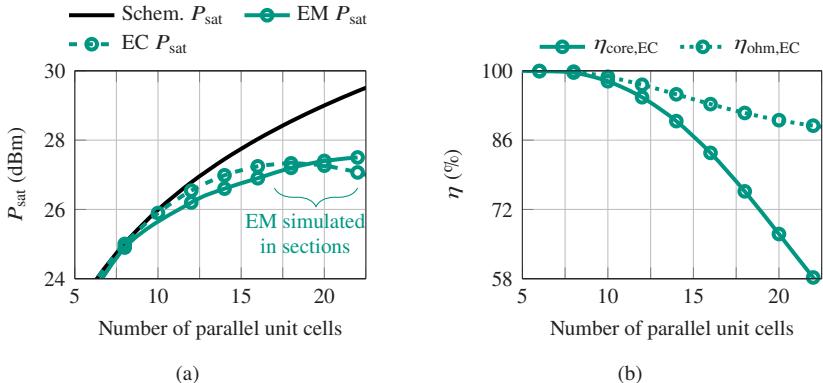

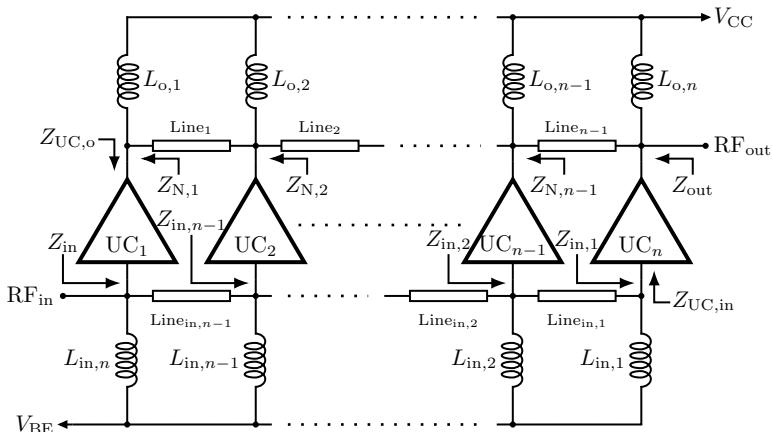

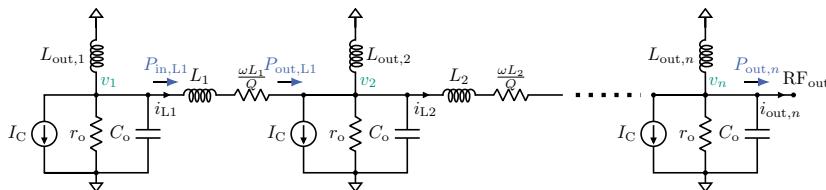

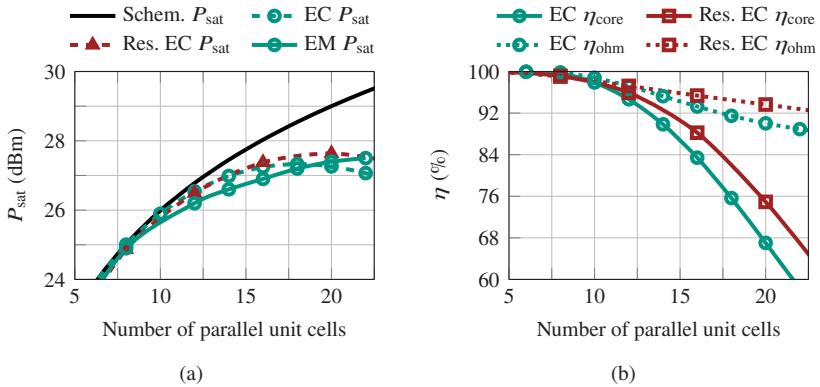

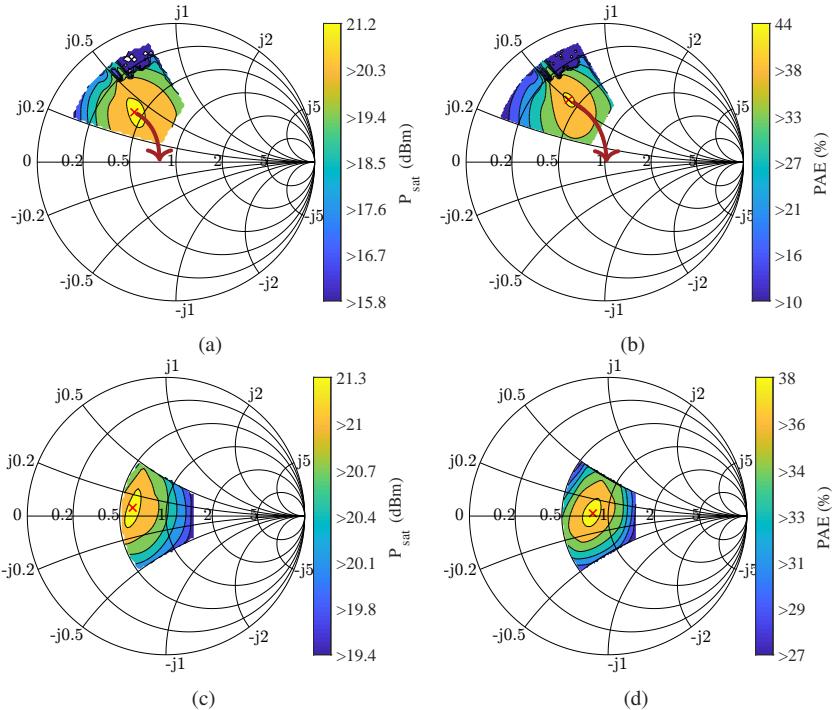

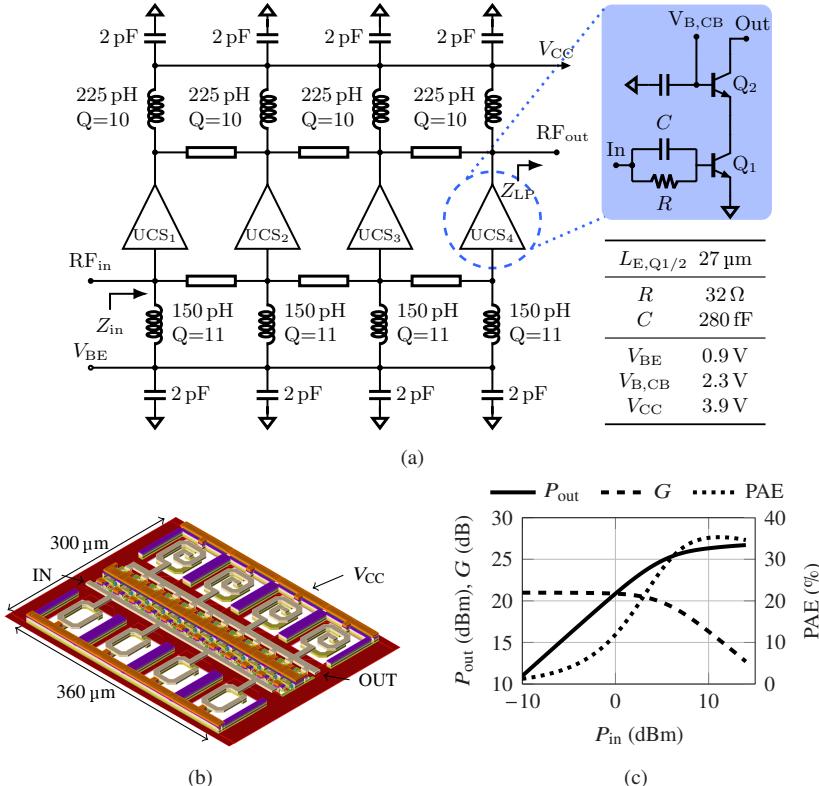

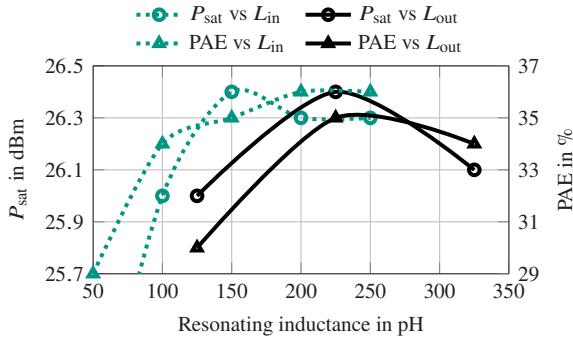

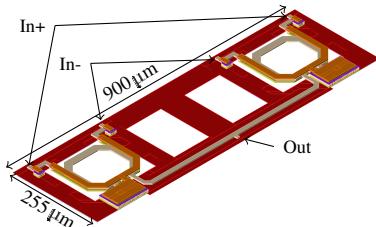

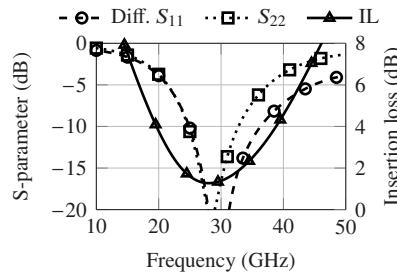

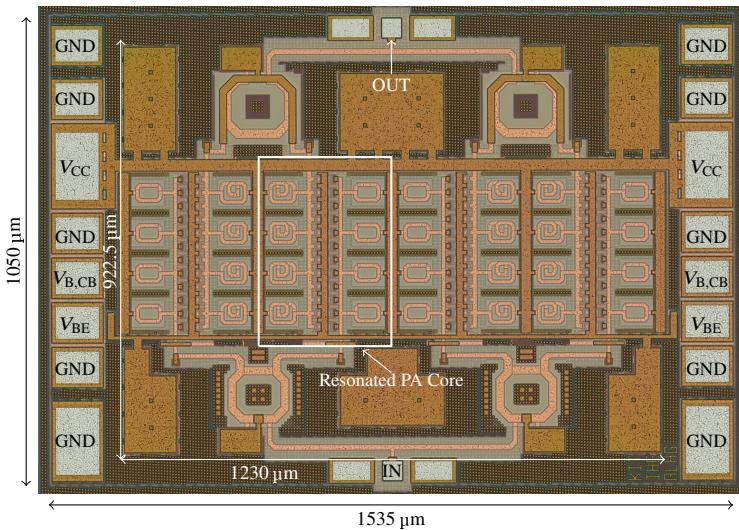

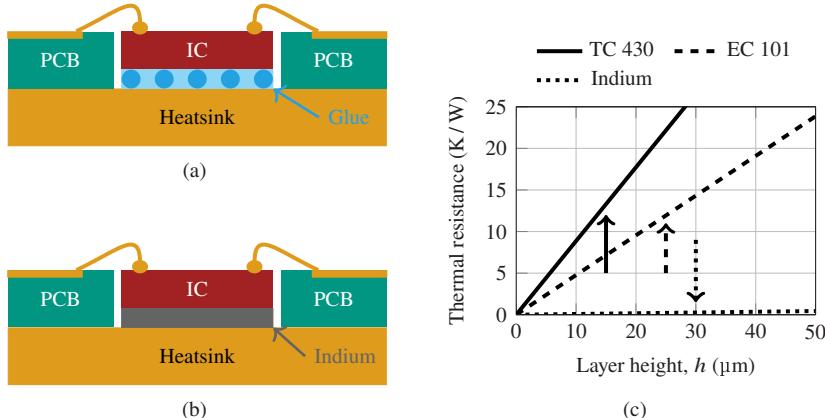

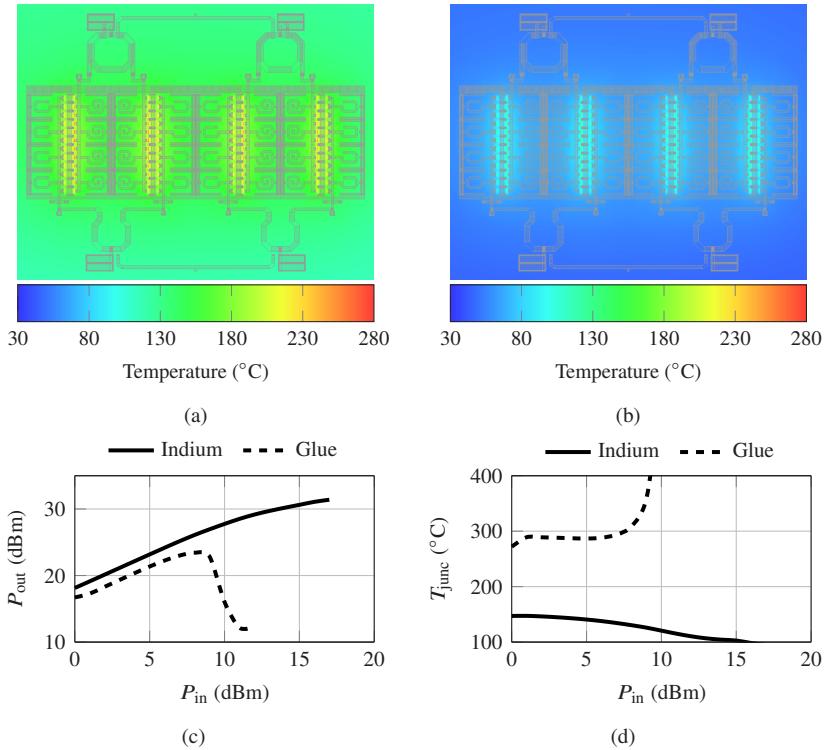

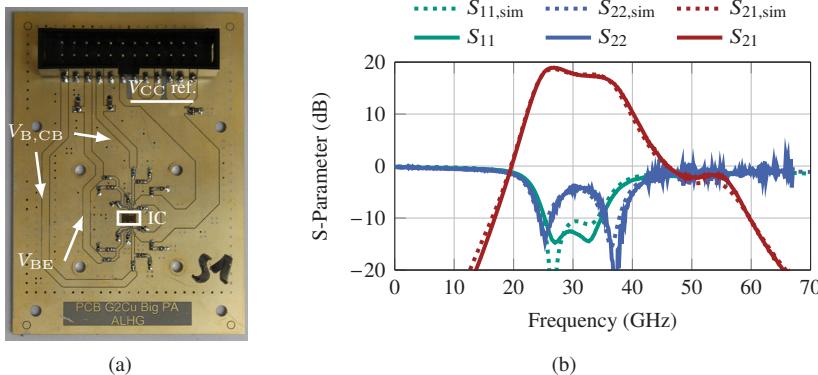

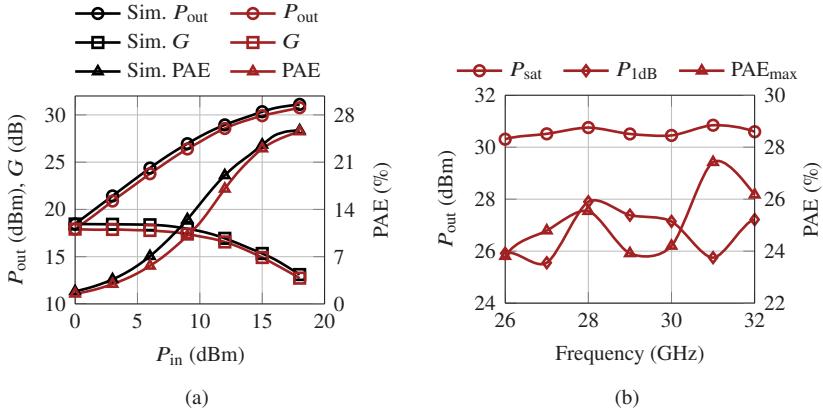

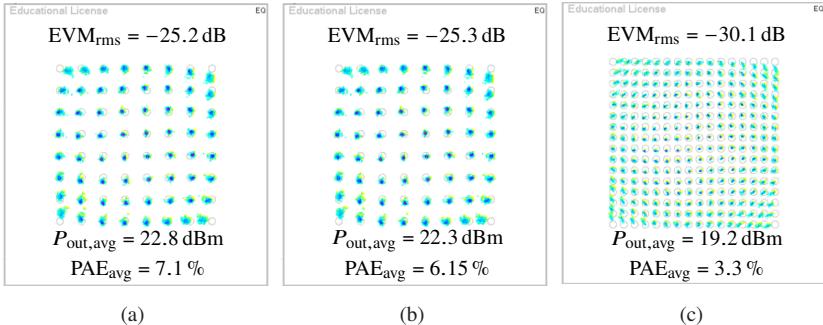

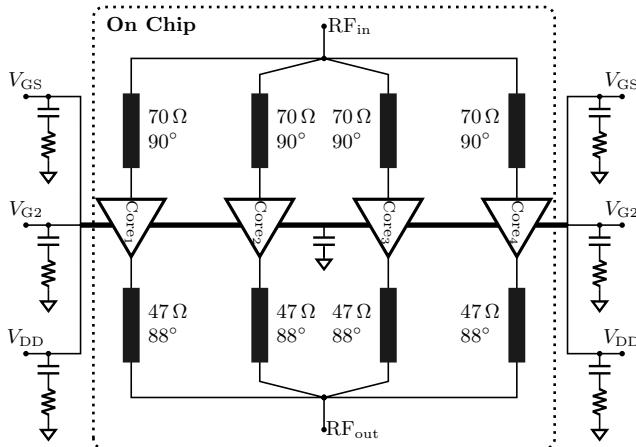

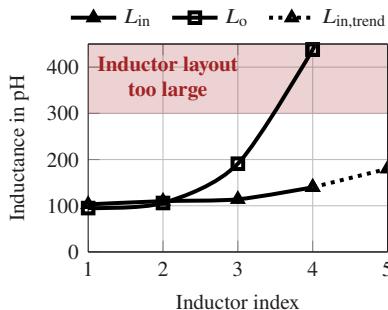

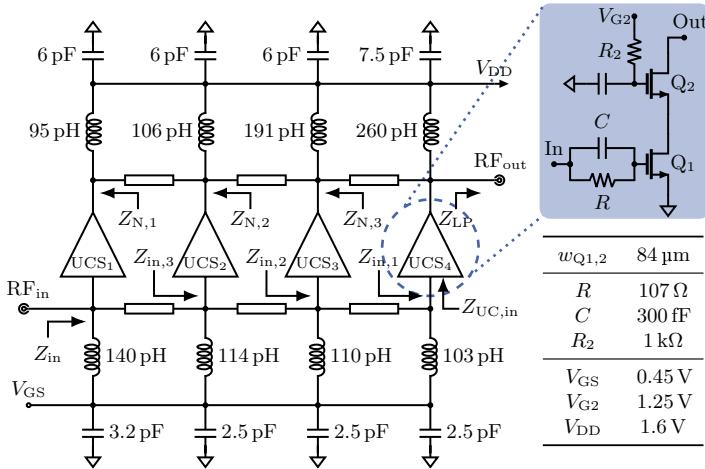

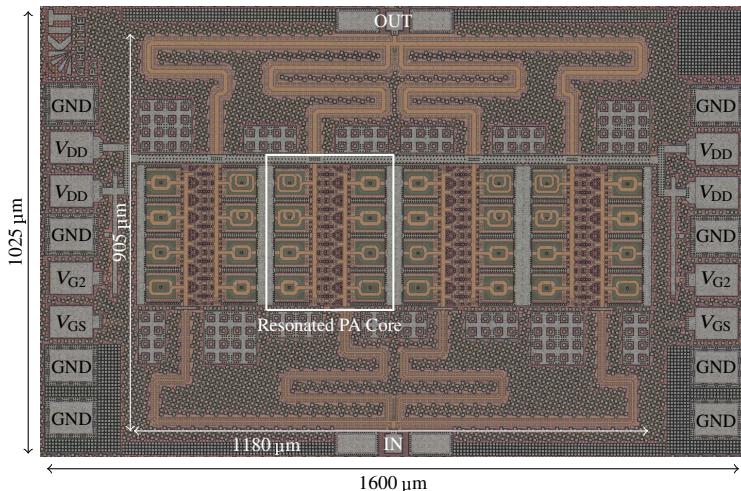

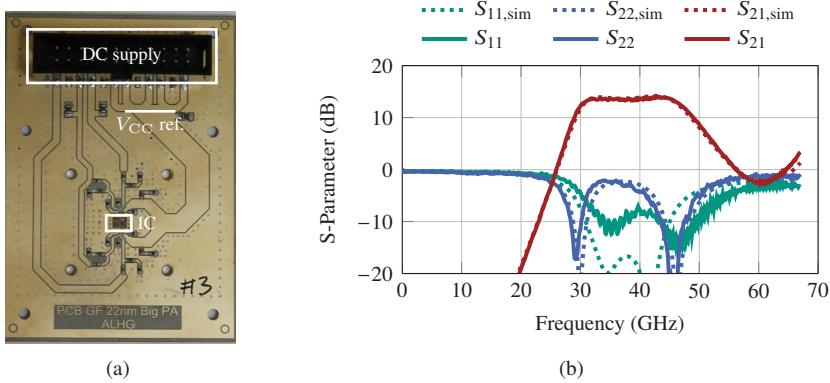

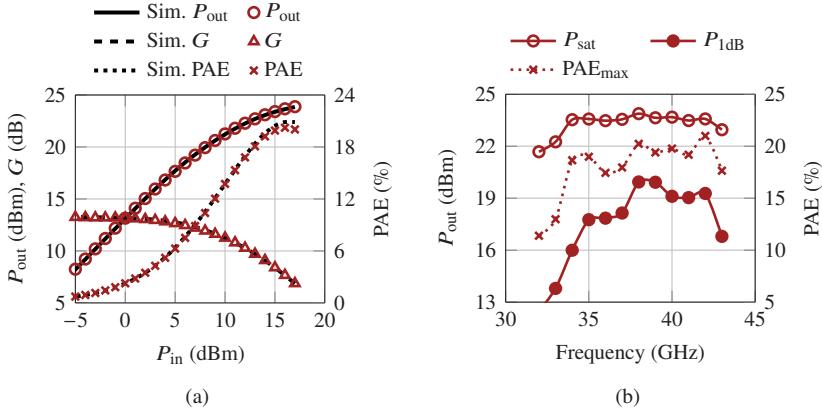

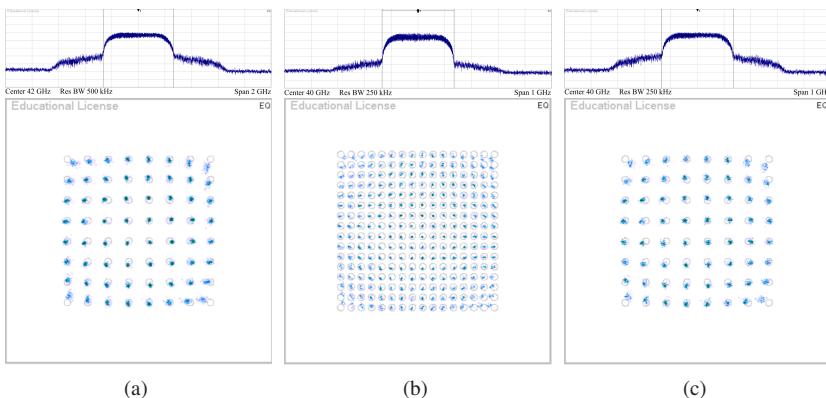

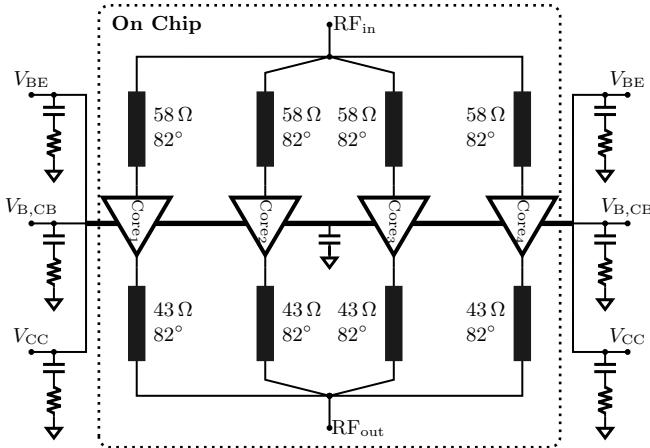

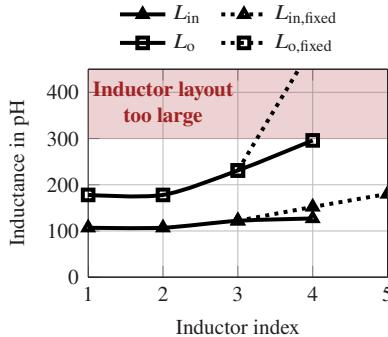

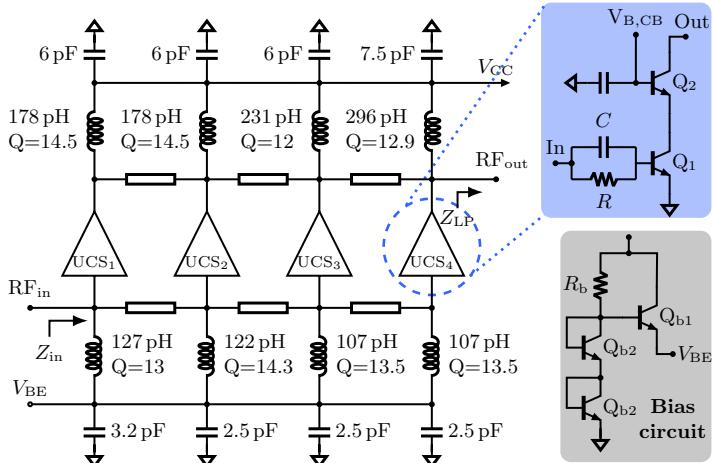

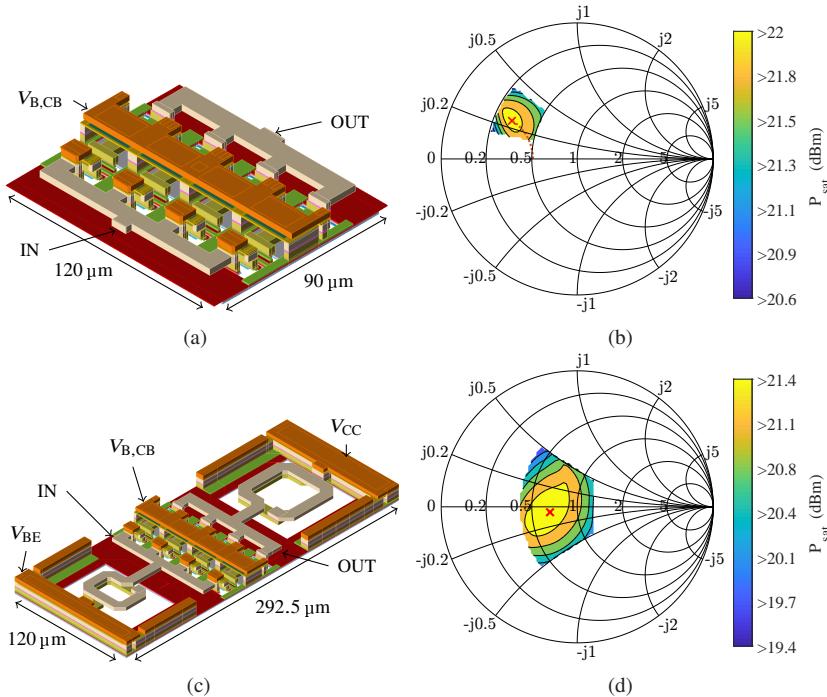

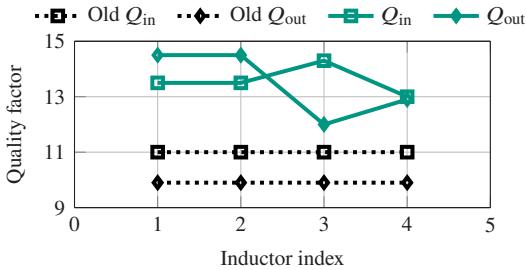

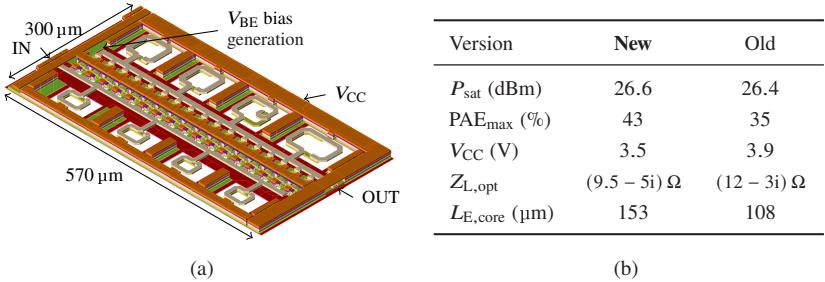

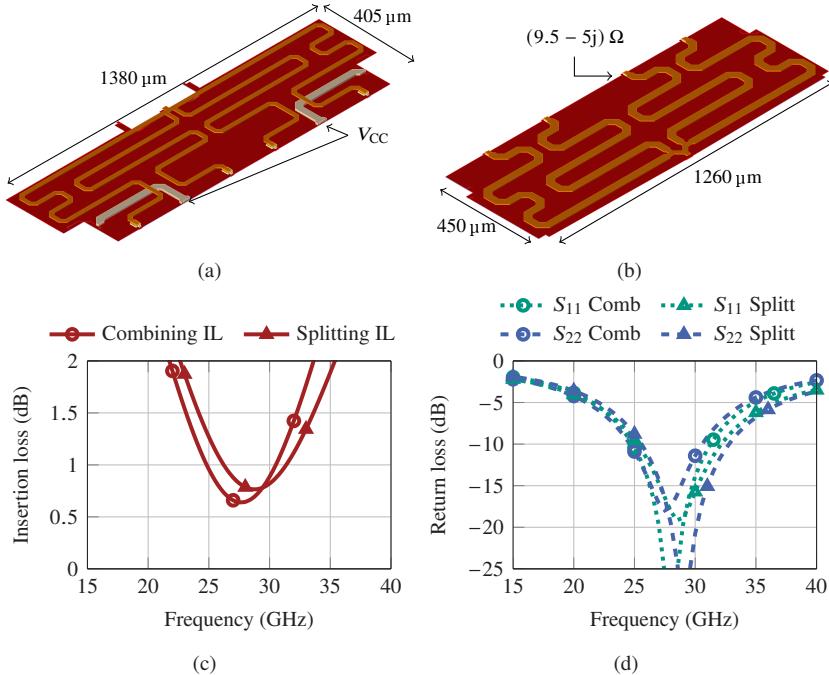

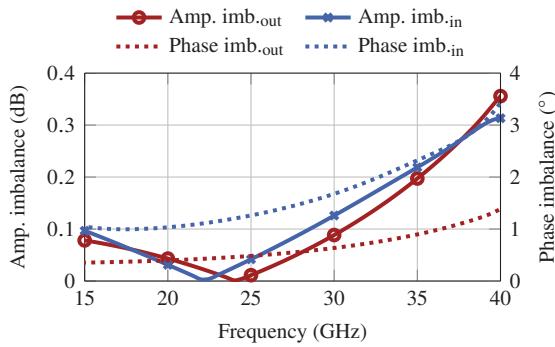

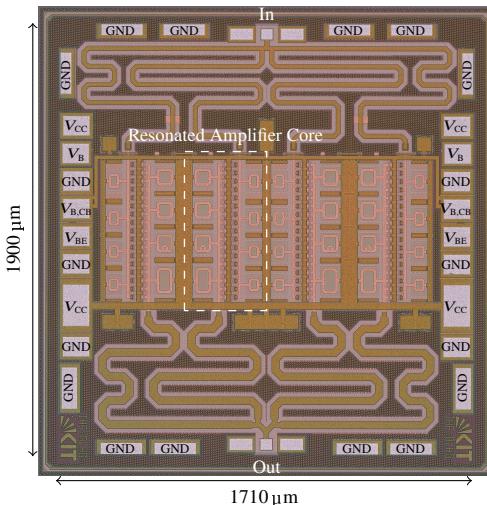

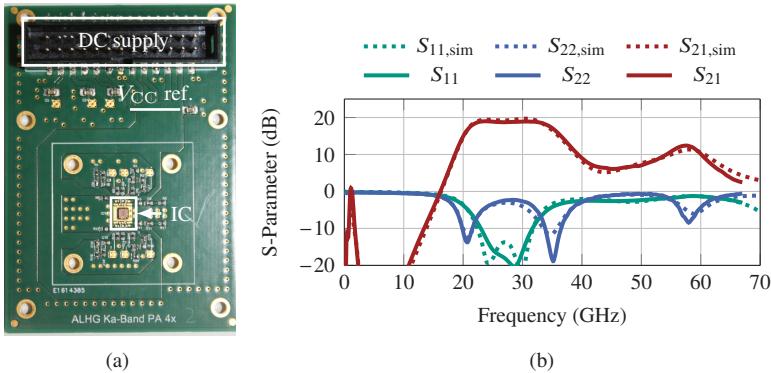

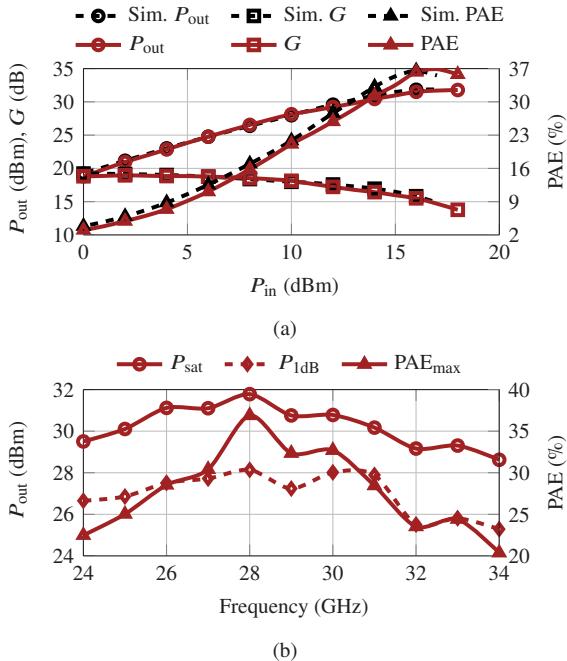

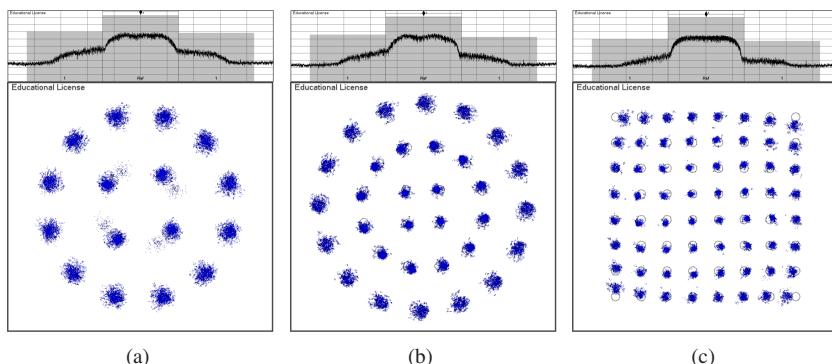

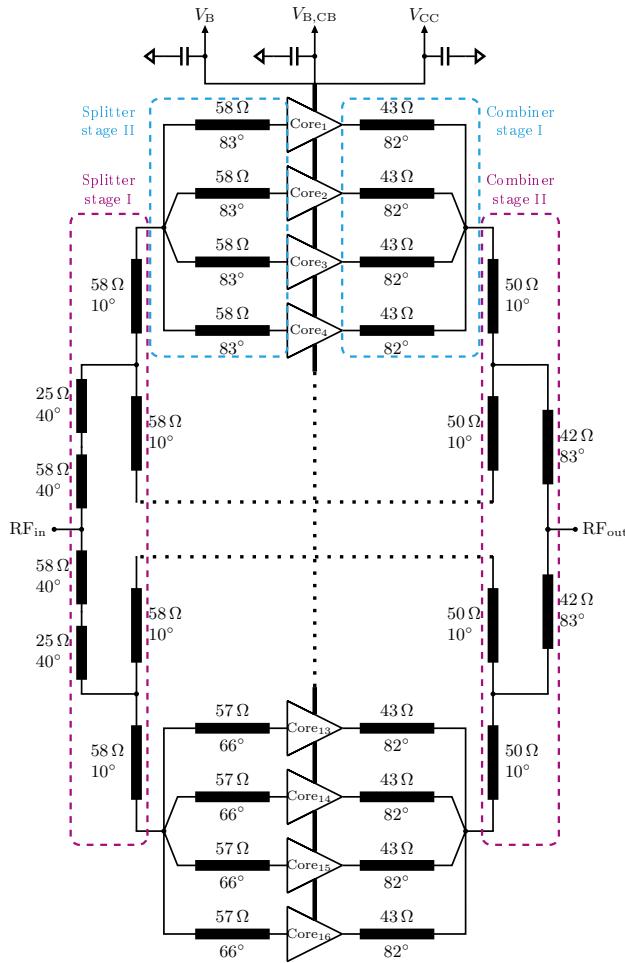

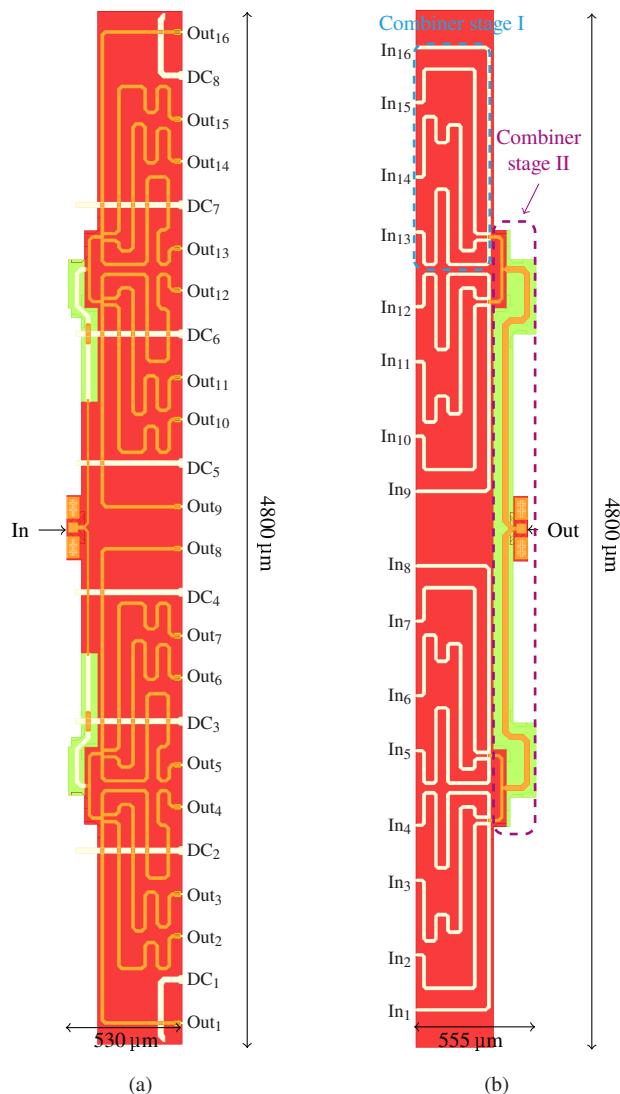

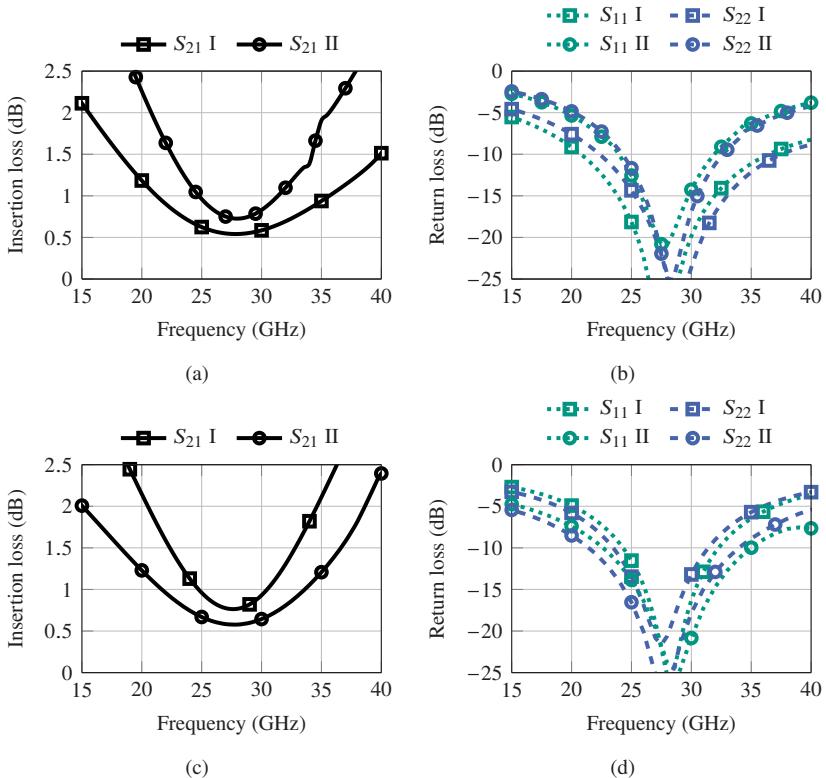

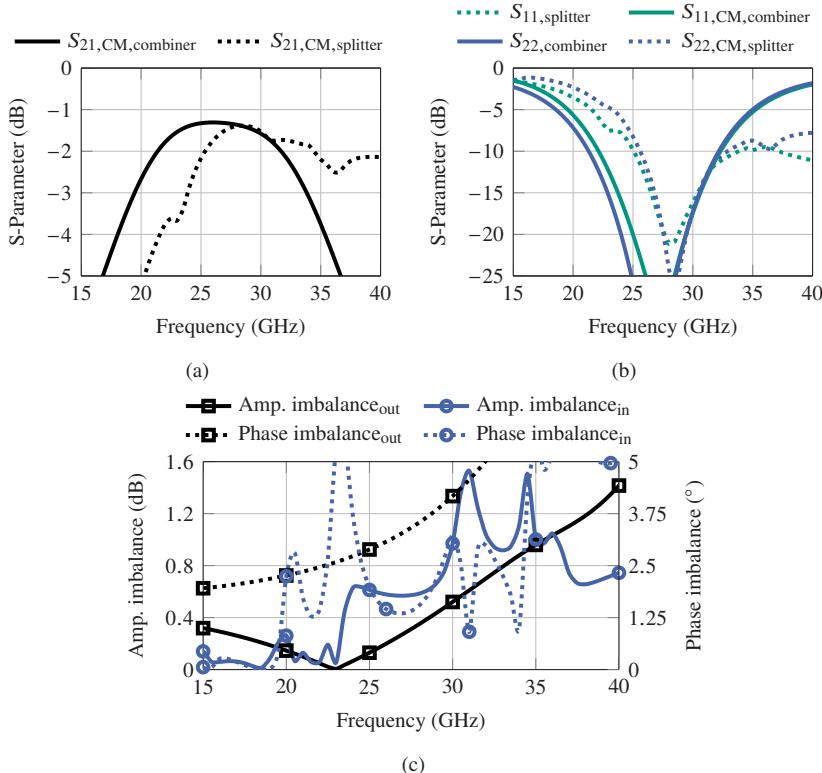

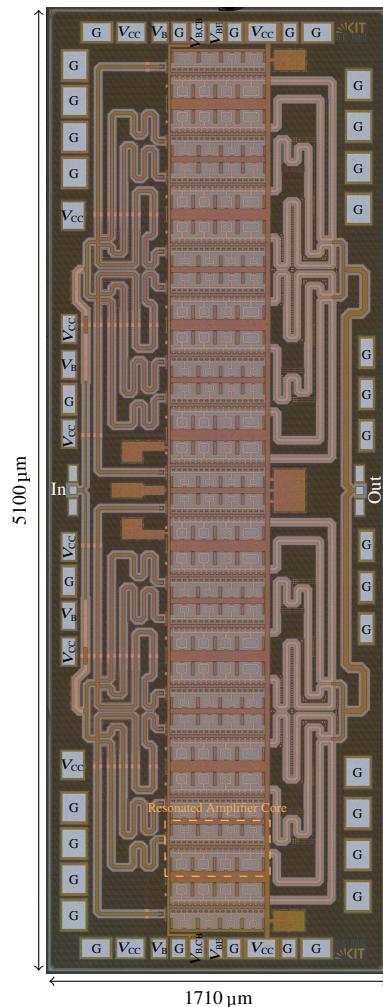

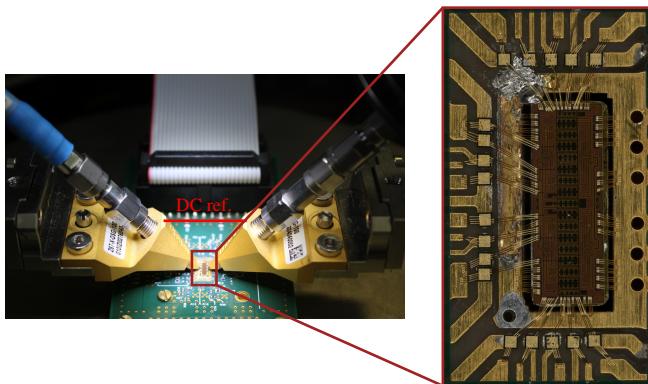

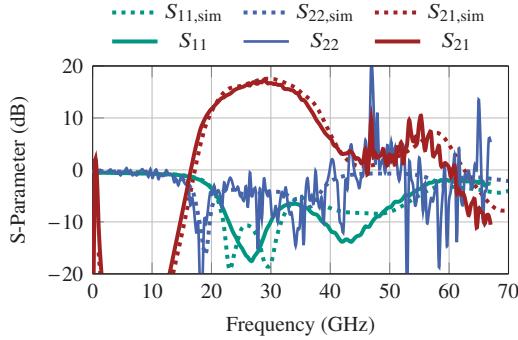

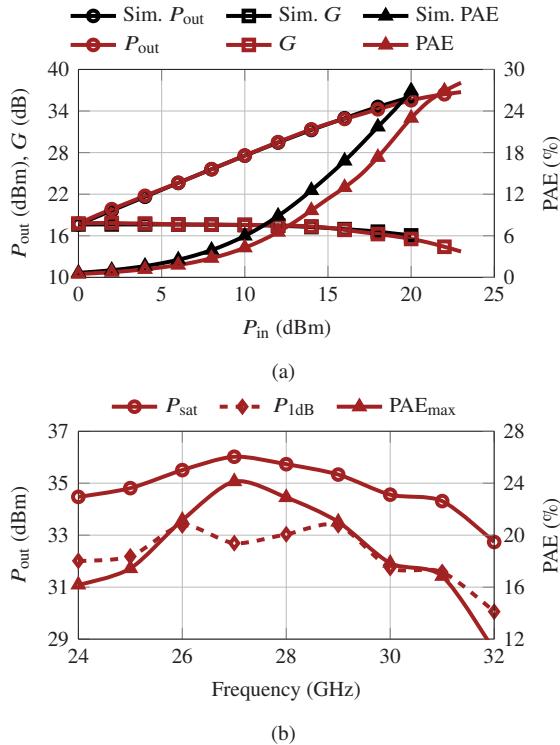

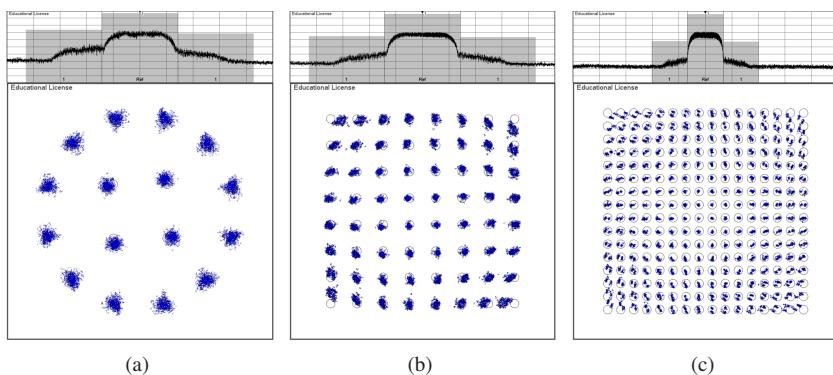

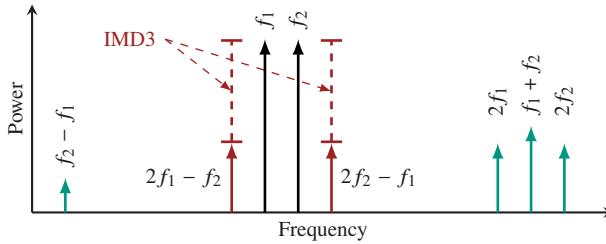

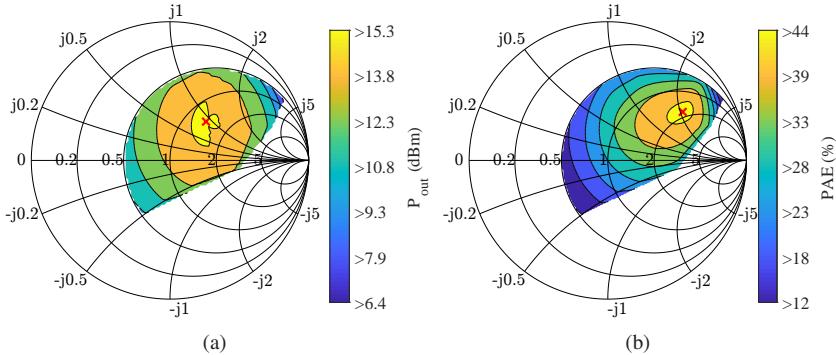

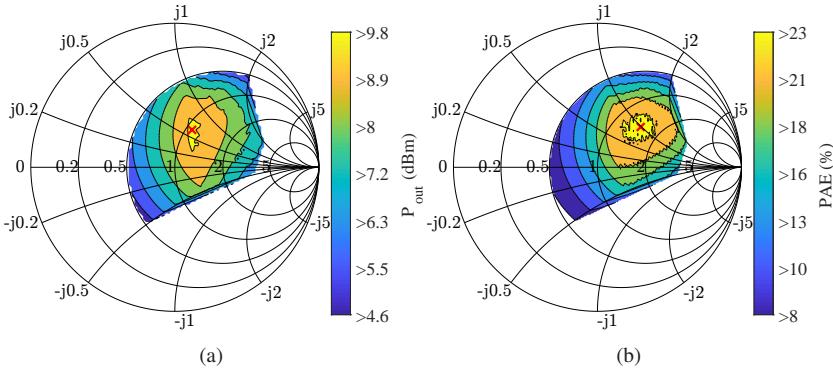

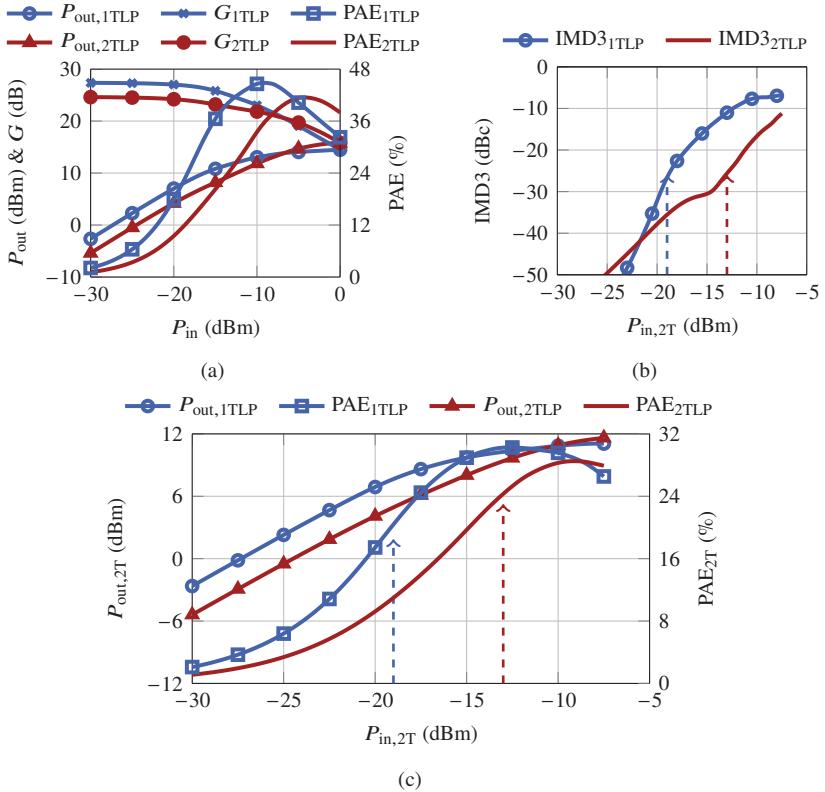

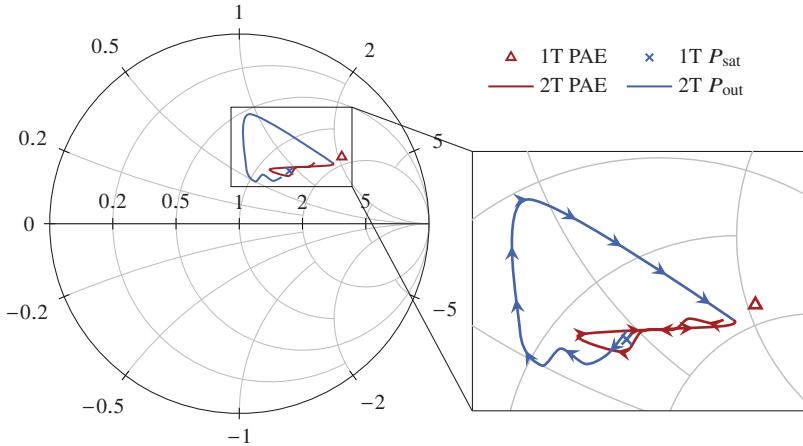

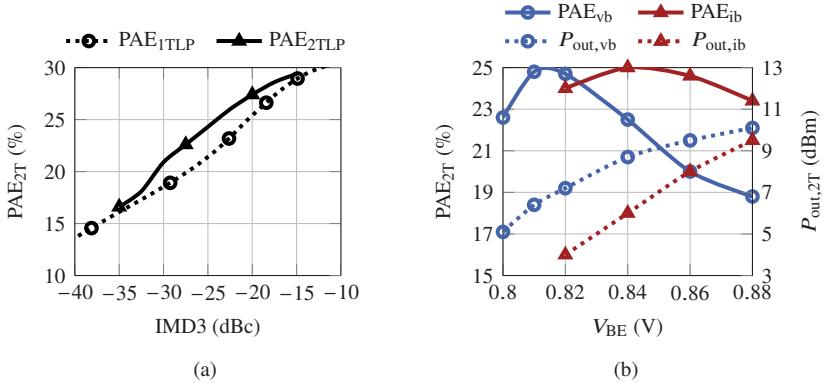

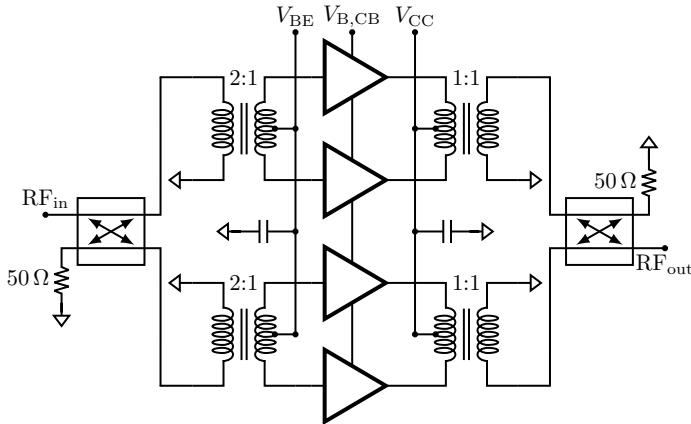

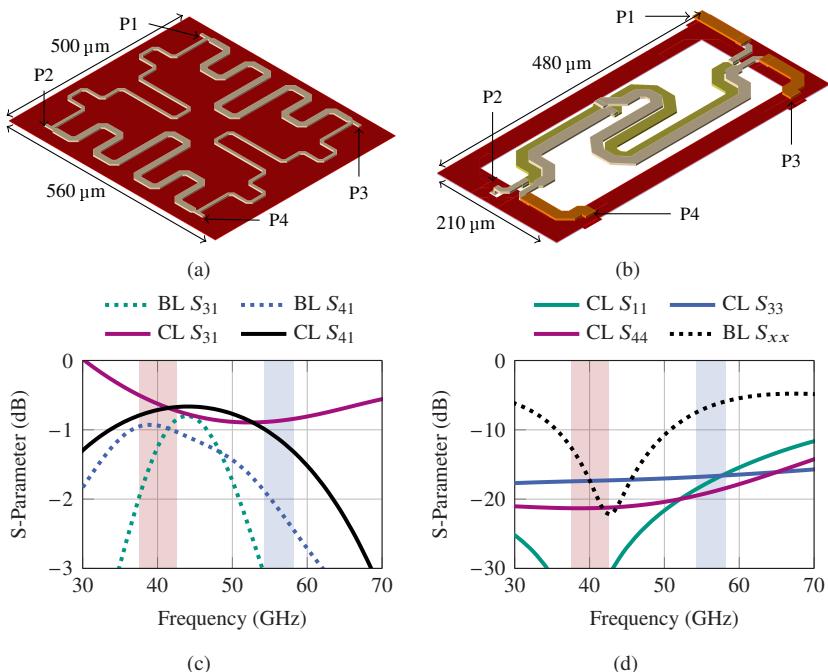

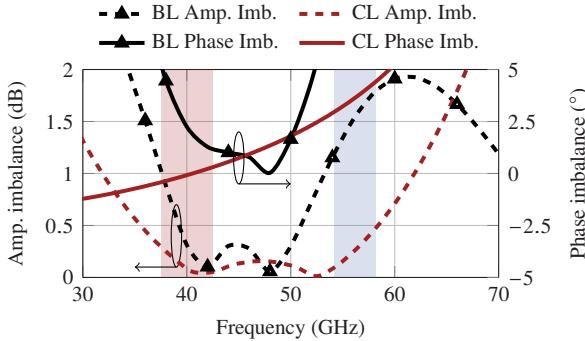

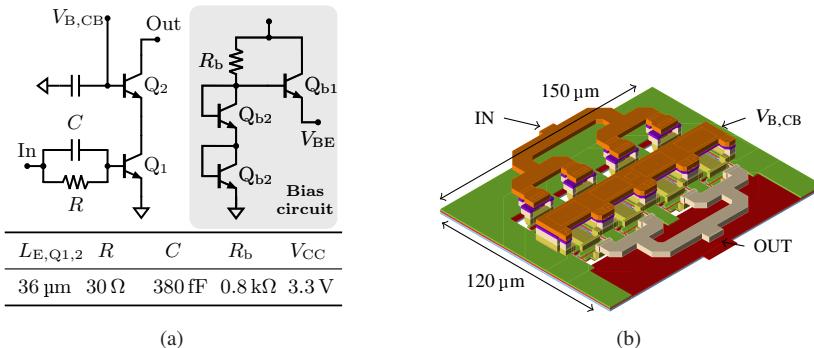

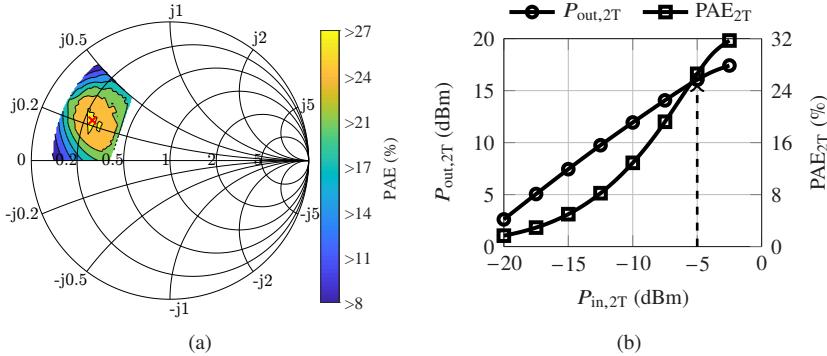

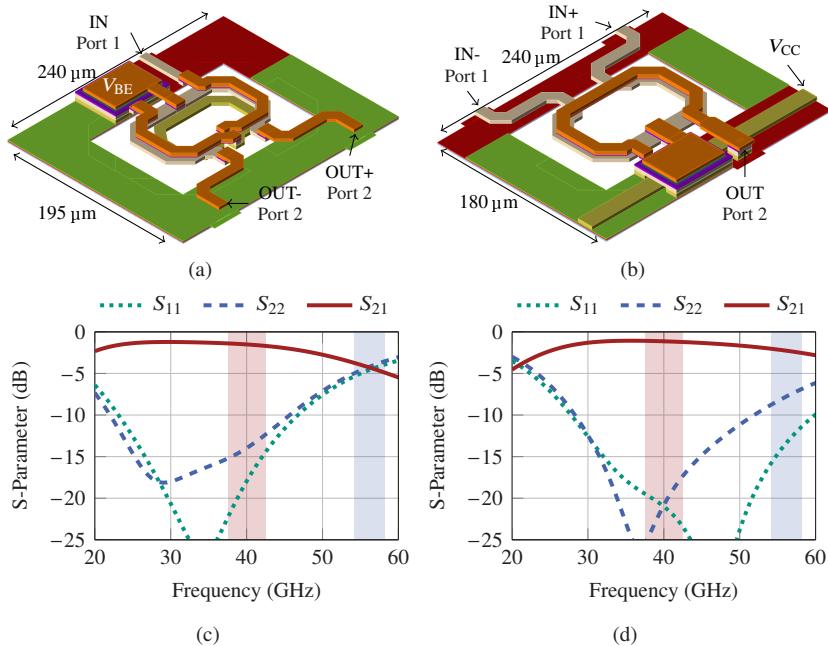

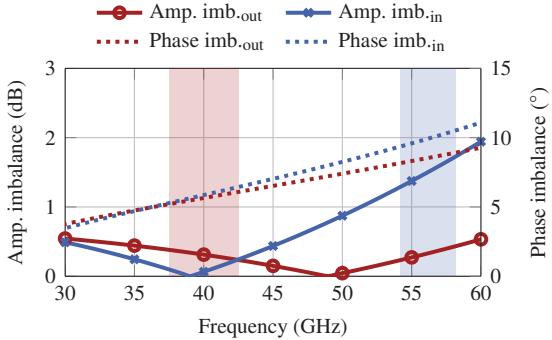

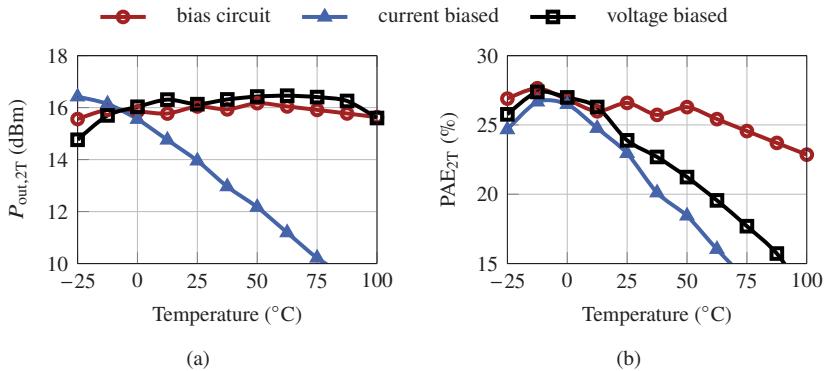

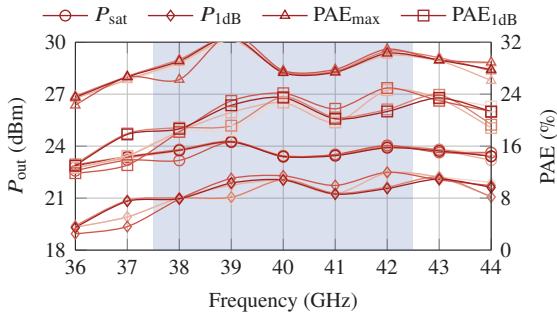

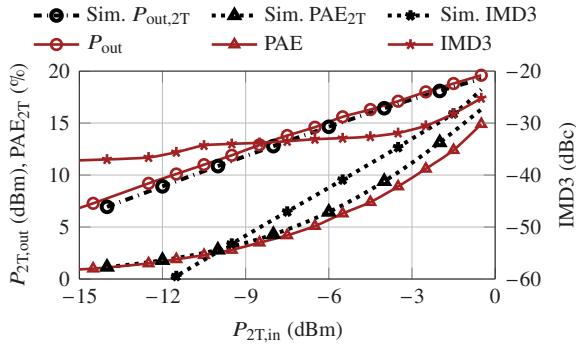

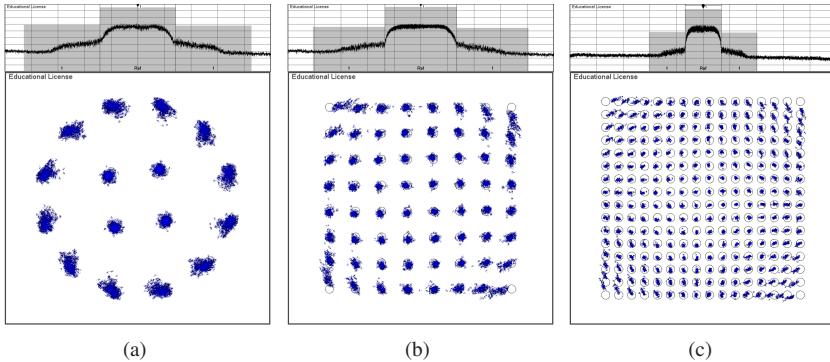

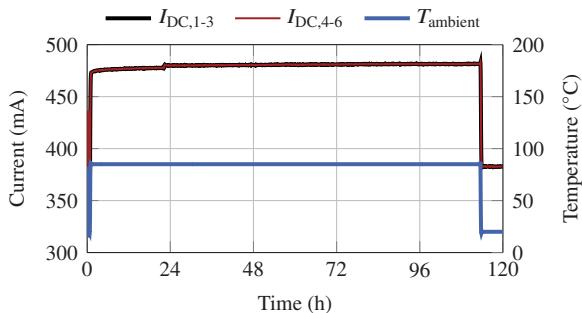

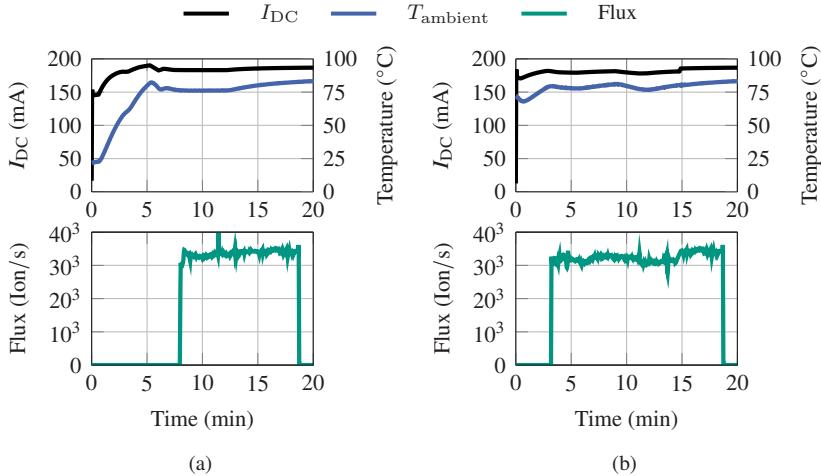

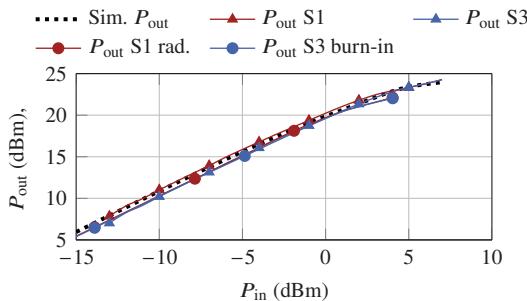

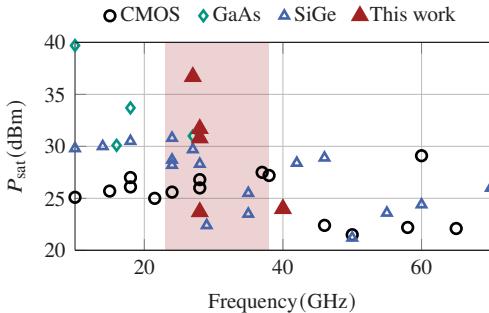

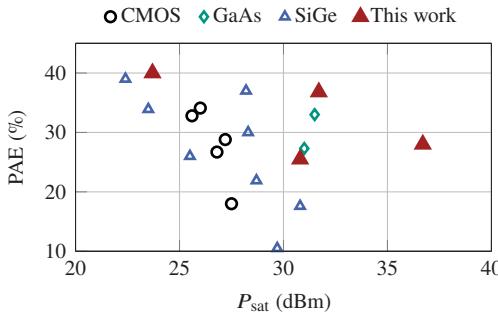

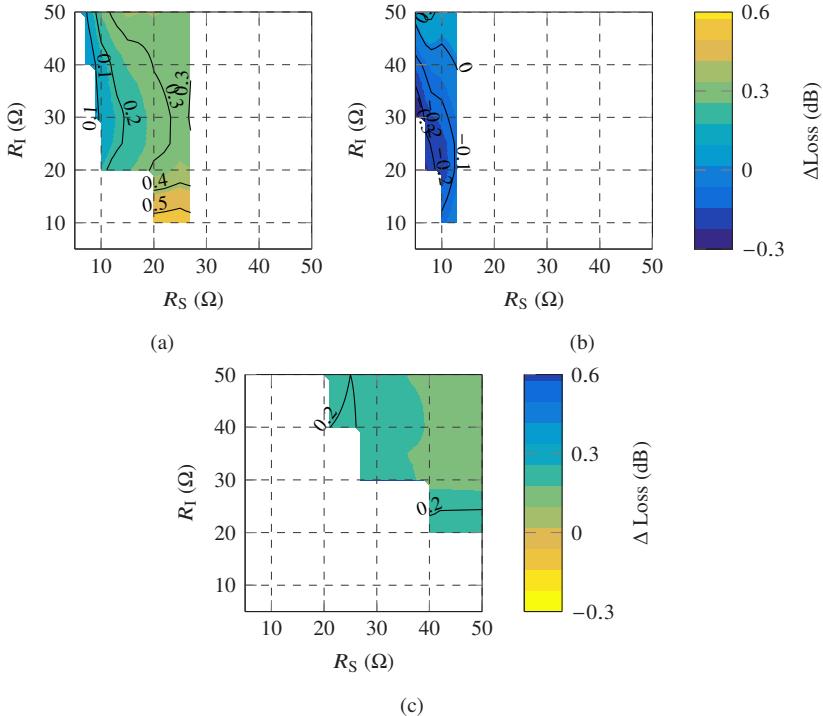

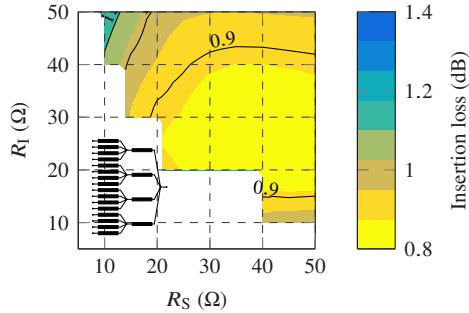

To co-optimize output power and efficiency, PA cores with different total device size are compared. To start, the load-pull data for each core is generated by load-pull simulations. The simulations are performed on the PA cores after EM simulation of the core layout. Fig. 3.7 shows the load-pull contours for maximum PAE. The simulated structure is a cascode PA core at 28 GHz with a total emitter length,  $L_E$ , of 72  $\mu\text{m}$ , or 80 fingers. Additionally, load-pull simulations are performed for PA cores with 40 ( $L_E = 36 \mu\text{m}$ ) and 140 ( $L_E = 126 \mu\text{m}$ ) fingers.