# **Effizientes Fuzzing von IoT-Geräten**

Zur Erlangung des akademischen Grades eines

Doktors der Ingenieurwissenschaften

von der KIT-Fakultät für Informatik

des Karlsruher Instituts für Technologie (KIT)

genehmigte

Dissertation

von

Matthias Börsig

---

---

Tag der mündlichen Prüfung: 18. Dezember 2025

- |              |                             |

|--------------|-----------------------------|

| 1. Referent: | PD Dr.-Ing. Ingmar Baumgart |

| 2. Referent: | Prof. Dr. Andreas Zeller    |

# Kurzzusammenfassung

Fuzzing ist eine bewährte Methode zur Identifizierung von Sicherheitslücken in Software. In dieser Dissertation wird untersucht, wie sich die Effizienz des Fuzzings für IoT-Geräte, am Beispiel des ESP32-Mikrocontrollers, steigern lässt. Während Fuzzing in klassischen Softwareumgebungen etabliert ist, fehlen speziell angepasste Verfahren für ressourcenarme IoT-Hardware. Das Ziel besteht in der Entwicklung eines konzeptionellen Frameworks, das eine umfassende und effiziente Testung trotz begrenzter IoT-Ressourcen ermöglicht. Zu diesem Zweck werden vier Ansätze zur Effizienzsteigerung sowie ein Konzept zur flexiblen Kombination dieser Ansätze vorgestellt.

Beim Binary Rewriting wird Binärkode so modifiziert, dass die Funktionalität erhalten bleibt. Für viele gängige Architekturen existieren bereits entsprechende Verfahren. Für die Xtensa-Architektur des ESP32 gab es jedoch bislang keine Lösung. In dieser Dissertation wird gezeigt, wie sich Binary Rewriting auf dem ESP32 umsetzen lässt, um Fuzzing-Instrumentierungen direkt in die Firmware zu integrieren und Laufzeitinformationen an den Fuzzer zurückzumelden.

Zudem wurde die Emulationsumgebung des ESP32 erheblich erweitert. Dadurch ist nun Fuzzing von beliebiger Firmware möglich, auch von Firmware mit zuvor nicht unterstützten Hardwarekomponenten. Im Vergleich zur realen Hardware arbeitet die Emulation deutlich effizienter. Während hardwarebasiertes Fuzzing vier bis 40 Anfragen pro Sekunde verarbeitet, sind es in der Emulation bis zu 320 Anfragen pro Sekunde.

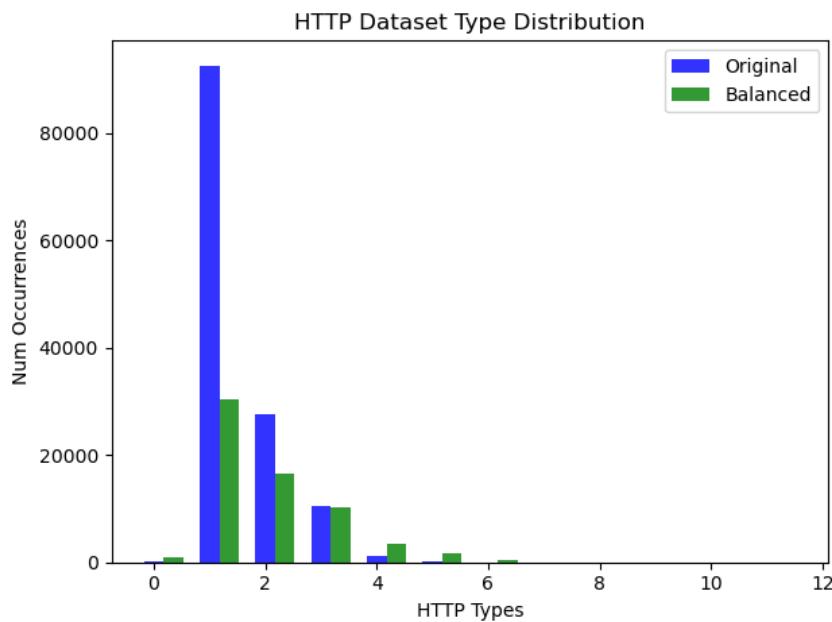

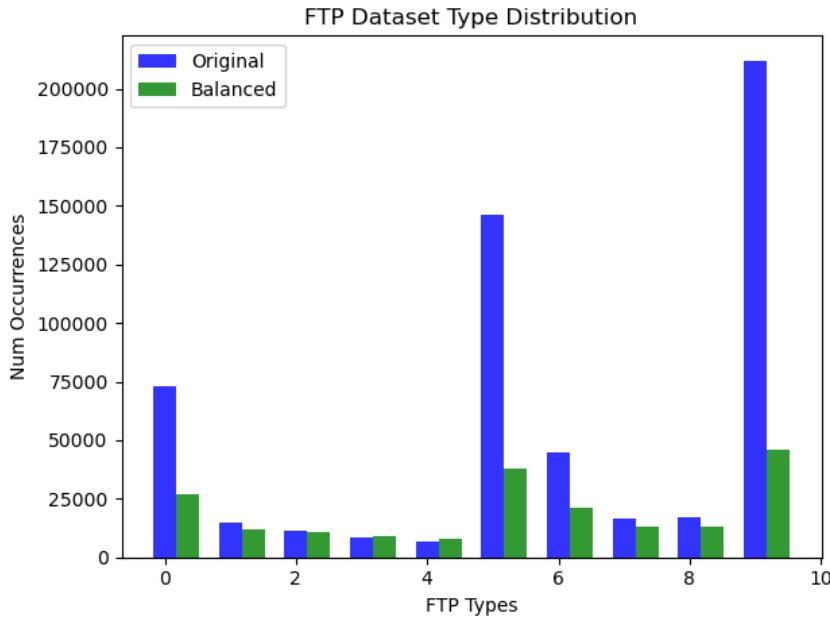

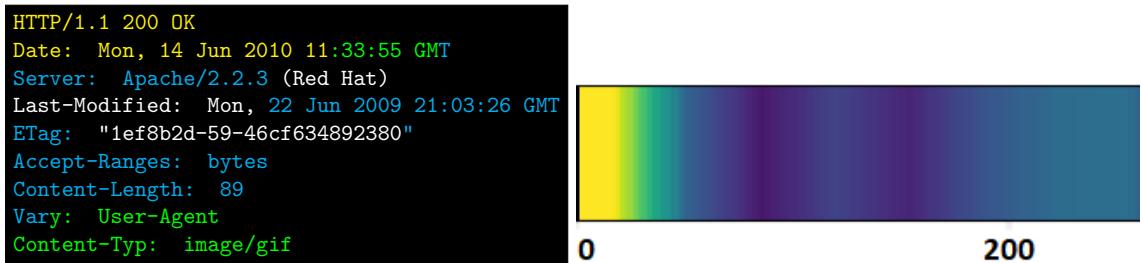

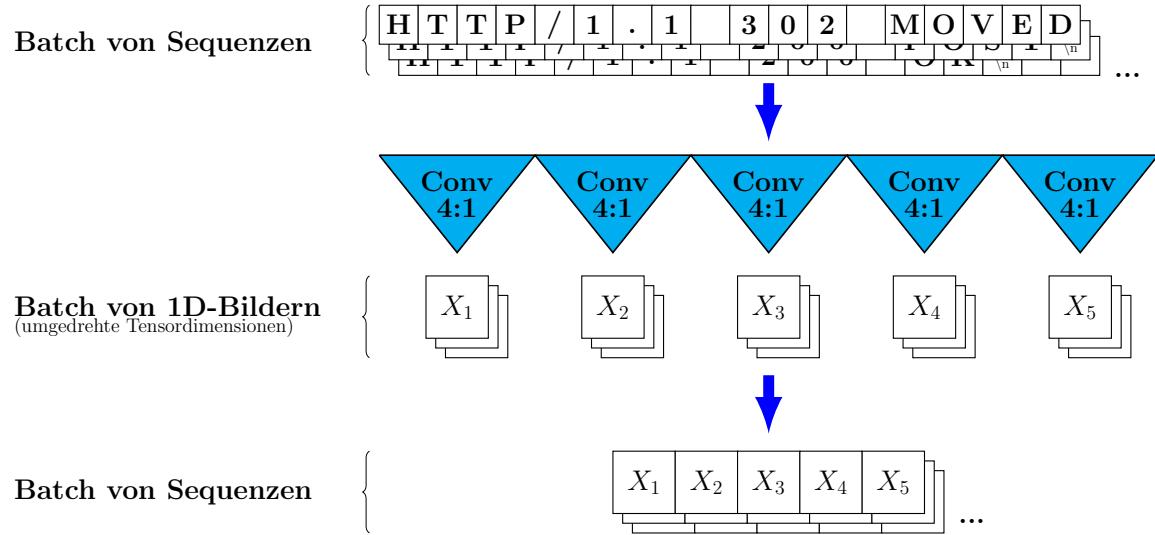

Zur Generierung valider Eingaben wurde ein Verfahren zum automatisierten Protocol Reverse Engineering (PRE) entwickelt, das Künstliche Neuronale Netze (KNNs) verwendet. Während PRE bislang manuell erfolgen musste, können nun Protokollstrukturen automatisch abgeleitet und damit syntaktisch korrekte Netzwerkpakete erzeugt werden. In den Tests waren 67,6 % der erzeugten HTTP-Pakete und 100 % der FTP-Pakete gültig.

Für das grammatikbasierte Fuzzing wird ein Ansatz mittels Large Language Models (LLMs) vorgestellt. Die zentrale Herausforderung bestand in der effizienten Integration des LLM in den Fuzzing-Prozess. Mithilfe der entwickelten Methode lassen sich syntaktisch und semantisch korrekte XML-Dateien generieren. Dies steigert die Programmflussabdeckung um den Faktor sechs gegenüber einer Ausführung ohne LLM und erreicht eine um 50 % höhere Abdeckung als klassische grammatikbasierte Fuzzer.

Abschließend wird ein Integrationskonzept präsentiert, das eine flexible Kombination der Ansätze ermöglicht und deren Verbesserungen additiv nutzbar macht. Dadurch trägt das Framework zur Effizienzsteigerung des Fuzzings von IoT-Geräten bei. Die Dissertation leistet somit einen wichtigen Beitrag zur praxisnahen Absicherung von IoT-Geräten.

# Abstract

Fuzzing is a well-established method of identifying security vulnerabilities in software. This dissertation explores ways to improve the efficiency of fuzzing for Internet of Things (IoT) devices, using the ESP32 microcontroller as a case study. While fuzzing is widely used in traditional software environments, few methods have been developed to address the limited resources available on IoT hardware.

The aim is to develop a conceptual framework that enables thorough and effective testing despite the limited resources available on IoT devices. To this end, four approaches to increasing efficiency are presented, along with a concept for combining these approaches flexibly.

In binary rewriting, the functionality of the machine code is preserved, but the code itself is modified. Although techniques already exist for many common architectures, there has been no solution available for the Xtensa architecture of the ESP32. This dissertation demonstrates how binary rewriting can be implemented on the ESP32 to integrate fuzzing instrumentation directly into the firmware, feeding runtime information back to the fuzzer.

The ESP32's emulation environment has also been significantly expanded. Consequently, fuzzing is now feasible for arbitrary firmware, including that which previously relied on unsupported hardware components. Compared to physical hardware, the emulation runs far more efficiently: while hardware-based fuzzing processes four to 40 requests per second, the emulation achieves up to 320.

To generate valid inputs, an automated Protocol Reverse Engineering (PRE) approach using Neural Networks (NN) was developed. While protocol reverse engineering had previously required manual effort, protocol structures can now be derived automatically, enabling the generation of syntactically correct network packets. During testing, 67.6 % of the generated HTTP packets and 100 % of the FTP packets were valid.

A new approach leveraging a Large Language Model (LLM) for grammar-based fuzzing has been introduced. The main challenge was integrating the LLM efficiently into the fuzzing process. The resulting method can generate XML files that are both syntactically and semantically correct. Compared to execution without an LLM, program flow coverage increases sixfold, achieving 50 % higher coverage than classical grammar-based fuzzers.

Finally, an approach is presented that integrates these concepts, enabling improvements to be applied additively. This enhances the efficiency of fuzzing for IoT devices. Consequently, this dissertation makes a significant contribution to the practical security of IoT systems.

# Inhaltsverzeichnis

|                                                                |            |

|----------------------------------------------------------------|------------|

| <b>Kurzzusammenfassung</b>                                     | <b>i</b>   |

| <b>Abstract</b>                                                | <b>iii</b> |

| <b>Abkürzungsverzeichnis</b>                                   | <b>xi</b>  |

| <b>1 Einleitung</b>                                            | <b>1</b>   |

| 1.1 Motivation . . . . .                                       | 1          |

| 1.2 Zielsetzung und wissenschaftlicher Beitrag . . . . .       | 3          |

| 1.3 Aufbau der Dissertation . . . . .                          | 5          |

| <b>2 Grundlagen</b>                                            | <b>7</b>   |

| 2.1 Besonderheiten von IoT-Geräten . . . . .                   | 7          |

| 2.1.1 Architekturen und Protokolle von IoT-Geräten . . . . .   | 7          |

| 2.1.2 Herausforderungen beim Fuzzing von IoT-Geräten . . . . . | 8          |

| 2.2 ESP32 Mikrocontroller . . . . .                            | 8          |

| 2.2.1 Architektur . . . . .                                    | 9          |

| 2.2.2 Firmware . . . . .                                       | 10         |

| 2.2.3 Xtensa ISA . . . . .                                     | 11         |

| 2.3 Rewriting . . . . .                                        | 12         |

| 2.3.1 Code Location Problem . . . . .                          | 12         |

| 2.3.2 Binary Rewriting . . . . .                               | 13         |

| 2.4 Fuzzing . . . . .                                          | 14         |

| 2.4.1 Definition von Fuzzing . . . . .                         | 14         |

| 2.4.2 Ungültige Eingaben . . . . .                             | 15         |

| 2.4.3 Fuzzing-Szenarien . . . . .                              | 15         |

| 2.4.4 Eingabegenerierung . . . . .                             | 16         |

| 2.4.5 Feedbackgesteuertes Fuzzing . . . . .                    | 17         |

| 2.4.6 Codeabdeckung und Messbarkeit von Fuzzing . . . . .      | 17         |

| 2.4.7 Effizientes Fuzzing . . . . .                            | 18         |

| 2.4.8 Syntaktische und semantische Korrektheit . . . . .       | 19         |

| 2.5 Grammatiken für Fuzzing . . . . .                          | 20         |

| 2.5.1 Aufbau der Grammatik . . . . .                           | 20         |

| 2.5.2 Formale Beschreibung von Grammatiken . . . . .           | 21         |

| 2.5.3 Kontextfreie Grammatiken . . . . .                       | 21         |

| 2.5.4 Grammatik von XML . . . . .                              | 21         |

| 2.5.5 Vorteile des grammatischen Fuzzings . . . . .            | 22         |

|          |                                                                                      |           |

|----------|--------------------------------------------------------------------------------------|-----------|

| 2.6      | Fuzzing im Emulator . . . . .                                                        | 22        |

| 2.7      | Netzwerkprotokolle . . . . .                                                         | 23        |

| 2.7.1    | Struktur eines TCP-Headers . . . . .                                                 | 25        |

| 2.7.2    | File Transfer Protocol (FTP) . . . . .                                               | 25        |

| 2.7.3    | Hypertext Transfer Protocol (HTTP) . . . . .                                         | 26        |

| 2.7.4    | Angriffsvektoren auf Netzwerkprotokolle . . . . .                                    | 26        |

| 2.7.5    | Protocol Reverse Engineering (PRE) . . . . .                                         | 27        |

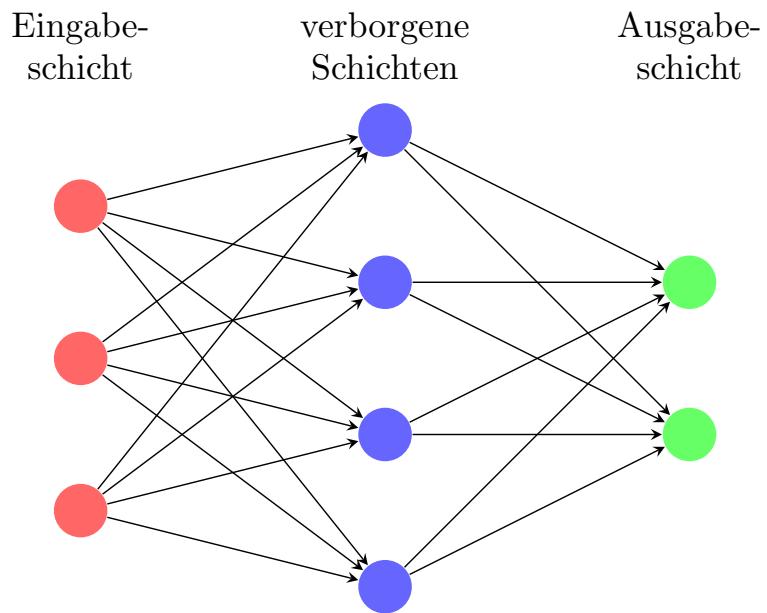

| 2.8      | Neuronale Netzwerkarchitekturen . . . . .                                            | 28        |

| 2.8.1    | Künstliches neuronales Netz (KNN) . . . . .                                          | 28        |

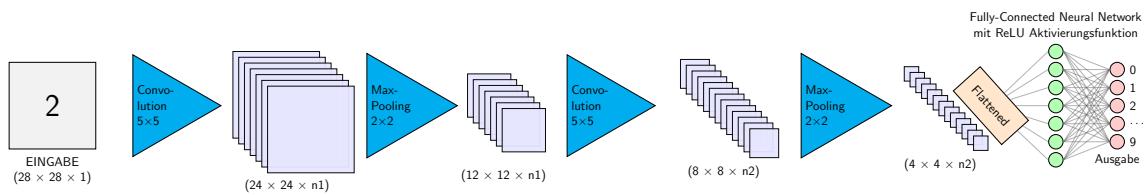

| 2.8.2    | Convolutional Neural Network (CNN) . . . . .                                         | 31        |

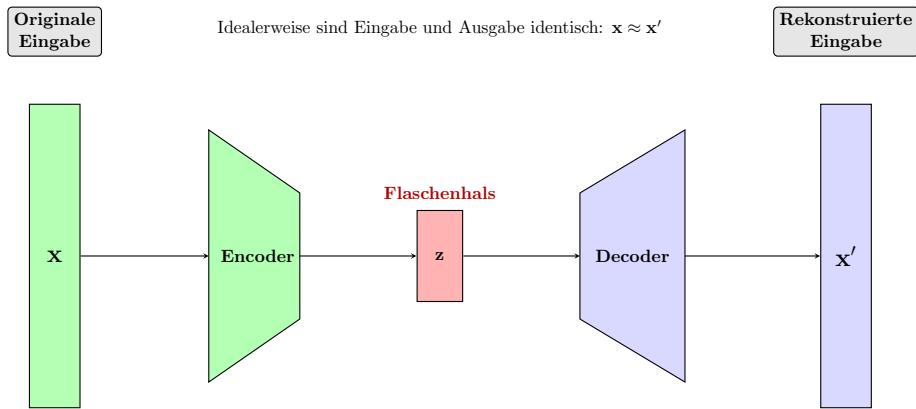

| 2.8.3    | Autoencoder (AE) . . . . .                                                           | 32        |

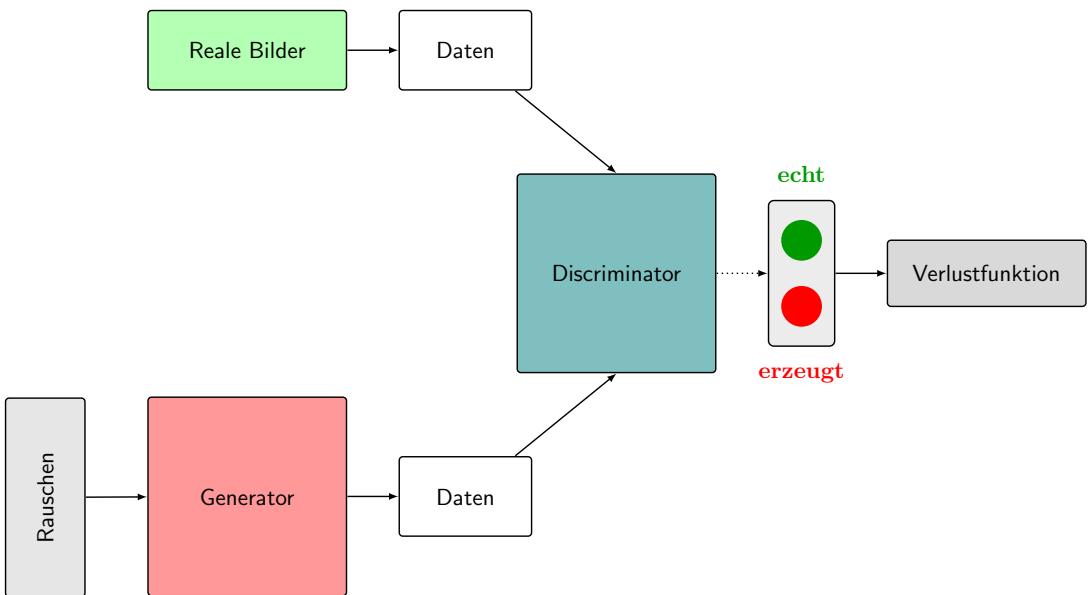

| 2.8.4    | Generative Adversarial Network (GAN) . . . . .                                       | 33        |

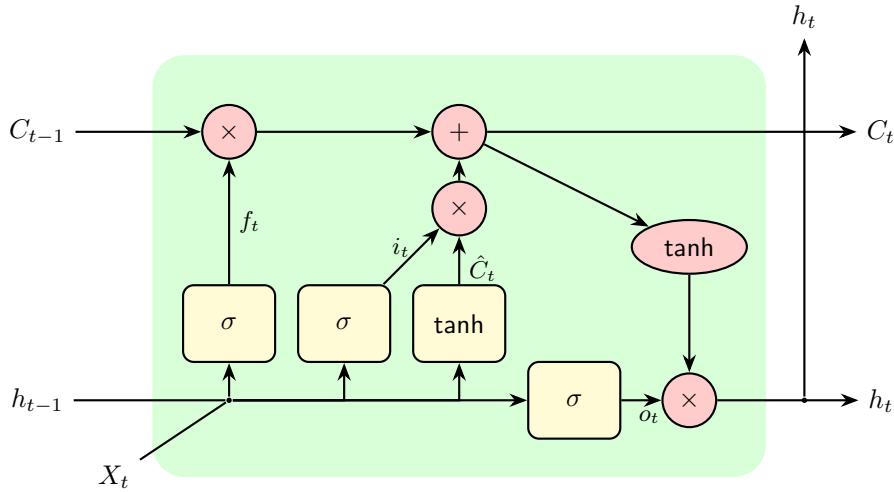

| 2.8.5    | Long Short-Term Memory (LSTM) . . . . .                                              | 33        |

| 2.8.6    | Self-Organizing Map (SOM) . . . . .                                                  | 34        |

| 2.8.7    | Large Language Model (LLM) . . . . .                                                 | 35        |

| 2.9      | Density-Based Spatial Clustering of Applications with Noise (DBSCAN) .               | 37        |

| <b>3</b> | <b>ESP32 Code-Injektion bei unverändertem Kontrollfluss mittels Binary Rewriting</b> | <b>39</b> |

| 3.1      | Einleitung . . . . .                                                                 | 39        |

| 3.2      | Stand der Technik . . . . .                                                          | 40        |

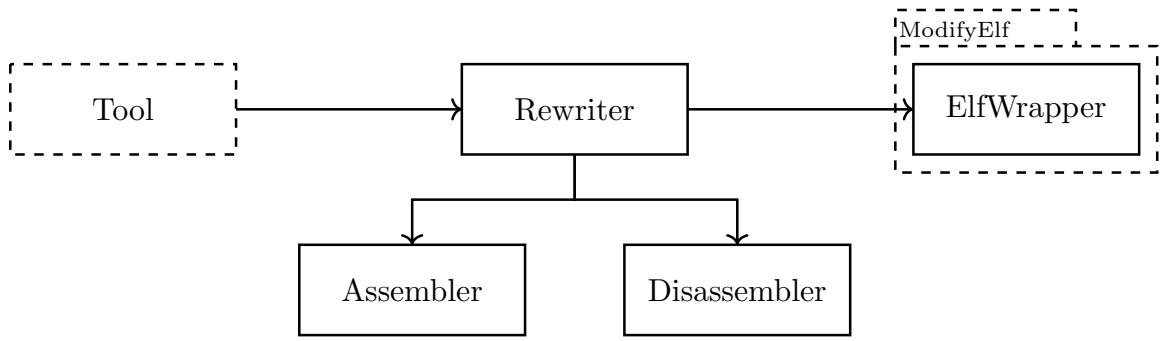

| 3.3      | Design . . . . .                                                                     | 41        |

| 3.3.1    | Binary Recovery . . . . .                                                            | 41        |

| 3.3.2    | Rewriter . . . . .                                                                   | 41        |

| 3.4      | Implementierung . . . . .                                                            | 44        |

| 3.4.1    | Binary Recovery . . . . .                                                            | 45        |

| 3.4.2    | Rewriter . . . . .                                                                   | 45        |

| 3.4.3    | Flashen nach dem Binary Rewriting zurück auf das Gerät . . . . .                     | 46        |

| 3.5      | Proof of Concept . . . . .                                                           | 46        |

| 3.5.1    | Entwicklung eines Beispiel-Tools . . . . .                                           | 47        |

| 3.5.2    | Implementierung des Beispiel-Tools . . . . .                                         | 47        |

| 3.5.3    | Verwendung des Beispiel-Tools . . . . .                                              | 49        |

| 3.6      | Einschränkungen und Ausblick . . . . .                                               | 50        |

| 3.7      | Zusammenfassung . . . . .                                                            | 52        |

| 3.8      | Fazit . . . . .                                                                      | 52        |

| <b>4</b> | <b>Fuzzing von ESP32-Mikrocontrollern mittels QEMU-Emulation</b>                     | <b>53</b> |

| 4.1      | Einleitung . . . . .                                                                 | 53        |

| 4.2      | Stand der Technik . . . . .                                                          | 54        |

| 4.3      | Konzeption . . . . .                                                                 | 55        |

| 4.3.1    | Fehlererkennung . . . . .                                                            | 56        |

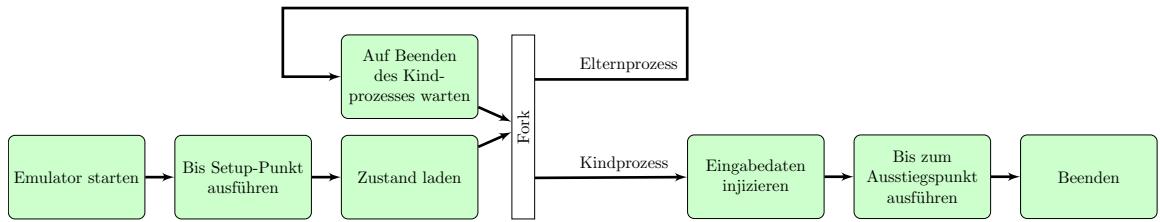

| 4.3.2    | Zielausführung mit Fuzzing-Hooks . . . . .                                           | 56        |

| 4.3.3    | Feedbackgesteuerte Eingabegenerierung . . . . .                                      | 57        |

| 4.4      | Implementierung . . . . .                                                            | 58        |

| 4.4.1    | Blackbox-Fuzzing auf ESP32-Anwendungen . . . . .                                     | 58        |

| 4.4.2    | Whitebox-Fuzzing mit compilerinstrumentiertem Code . . . . .                         | 59        |

|          |                                                              |           |

|----------|--------------------------------------------------------------|-----------|

| 4.4.3    | Whitebox-Fuzzing mit ESP32-QEMU-FUZZ . . . . .               | 60        |

| 4.4.4    | Blackbox- und Greybox-Fuzzing mit ESP32-QEMU-FUZZ . . . . .  | 61        |

| 4.5      | Evaluation . . . . .                                         | 63        |

| 4.5.1    | Fuzzing der TCP-Testanwendung . . . . .                      | 63        |

| 4.5.2    | Greybox-Fuzzing der LIFX Mini . . . . .                      | 64        |

| 4.6      | Einschränkungen und Ausblick . . . . .                       | 66        |

| 4.7      | Zusammenfassung . . . . .                                    | 66        |

| 4.8      | Fazit . . . . .                                              | 67        |

| <b>5</b> | <b>Protocol Reverse Engineering mittels neuronaler Netze</b> | <b>69</b> |

| 5.1      | Einleitung . . . . .                                         | 69        |

| 5.2      | Stand der Technik . . . . .                                  | 70        |

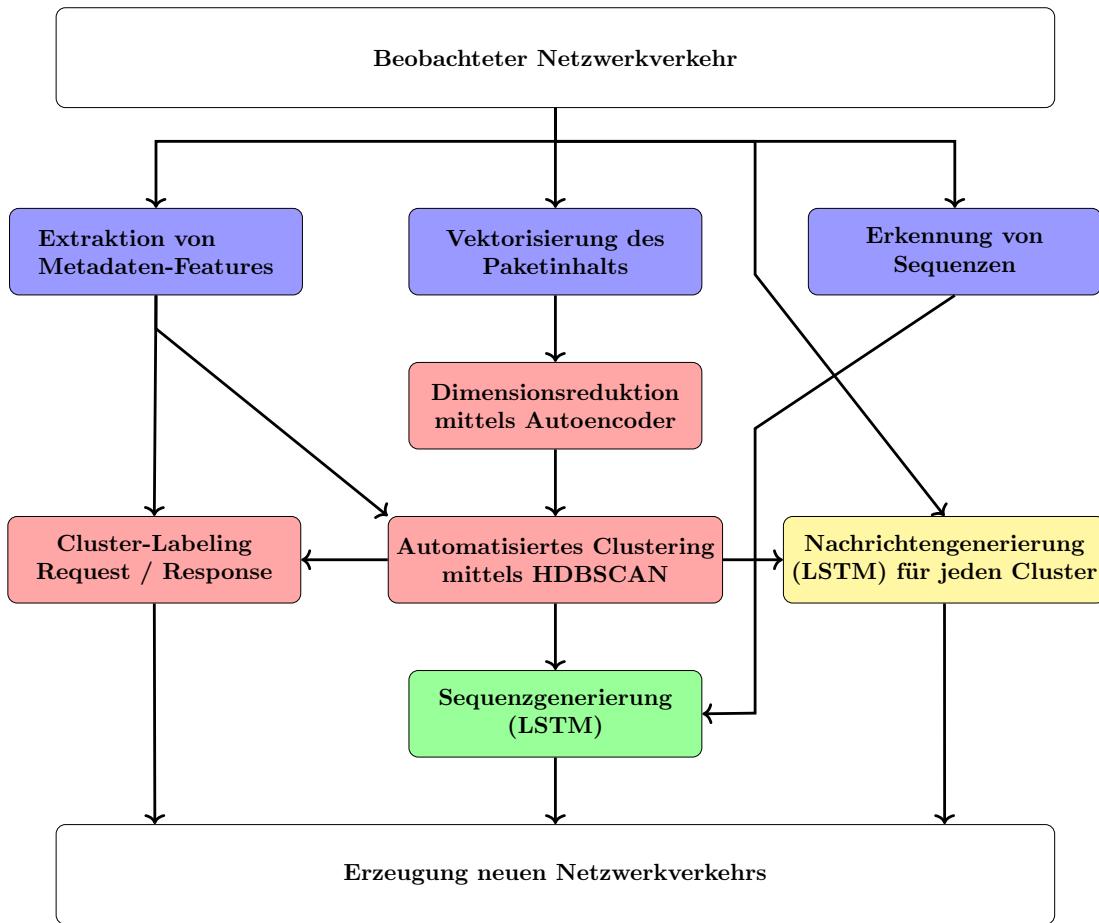

| 5.3      | Hauptansatz . . . . .                                        | 72        |

| 5.3.1    | Datenerfassung . . . . .                                     | 73        |

| 5.3.2    | Feature Extraction . . . . .                                 | 73        |

| 5.3.3    | Reverse Engineering von Features . . . . .                   | 73        |

| 5.3.4    | Clustering . . . . .                                         | 73        |

| 5.3.5    | Zustandserkennung . . . . .                                  | 74        |

| 5.3.6    | Sequenzgenerierung . . . . .                                 | 74        |

| 5.4      | Implementierung von PREUNN . . . . .                         | 74        |

| 5.4.1    | Datenvorverarbeitung . . . . .                               | 75        |

| 5.4.2    | Feature Extraction . . . . .                                 | 76        |

| 5.4.3    | Feature Reverse Engineering . . . . .                        | 79        |

| 5.4.4    | Clustering . . . . .                                         | 82        |

| 5.4.5    | Zustandserkennung . . . . .                                  | 84        |

| 5.4.6    | Sequenzgenerierung . . . . .                                 | 86        |

| 5.5      | Weiterentwicklung . . . . .                                  | 88        |

| 5.5.1    | Vorverarbeitung der Daten . . . . .                          | 88        |

| 5.5.2    | Klassifizierung von Nachrichtentypen und Zustandsübergängen  | 90        |

| 5.5.3    | Erlernen des Nachrichtenaufbaus . . . . .                    | 90        |

| 5.5.4    | Generierung neuer Testfälle . . . . .                        | 91        |

| 5.6      | Implementierung von PREUNN2 . . . . .                        | 92        |

| 5.6.1    | Vorverarbeitung . . . . .                                    | 92        |

| 5.6.2    | Clustering . . . . .                                         | 92        |

| 5.6.3    | Generierung neuer Pakete und Sequenzen . . . . .             | 92        |

| 5.7      | Evaluation . . . . .                                         | 93        |

| 5.7.1    | ProFuzzBench . . . . .                                       | 93        |

| 5.7.2    | AFLNet . . . . .                                             | 93        |

| 5.7.3    | Integration der Machine-Learning-Methoden . . . . .          | 93        |

| 5.7.4    | Implementierung der Fuzzing-Ziele . . . . .                  | 94        |

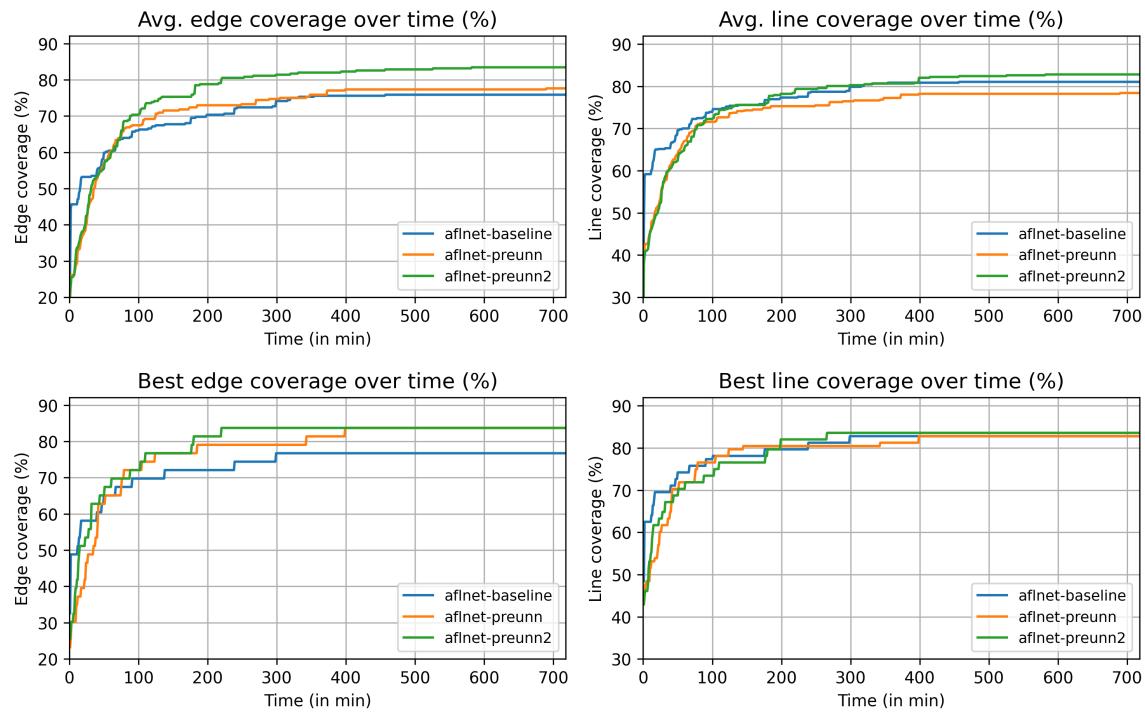

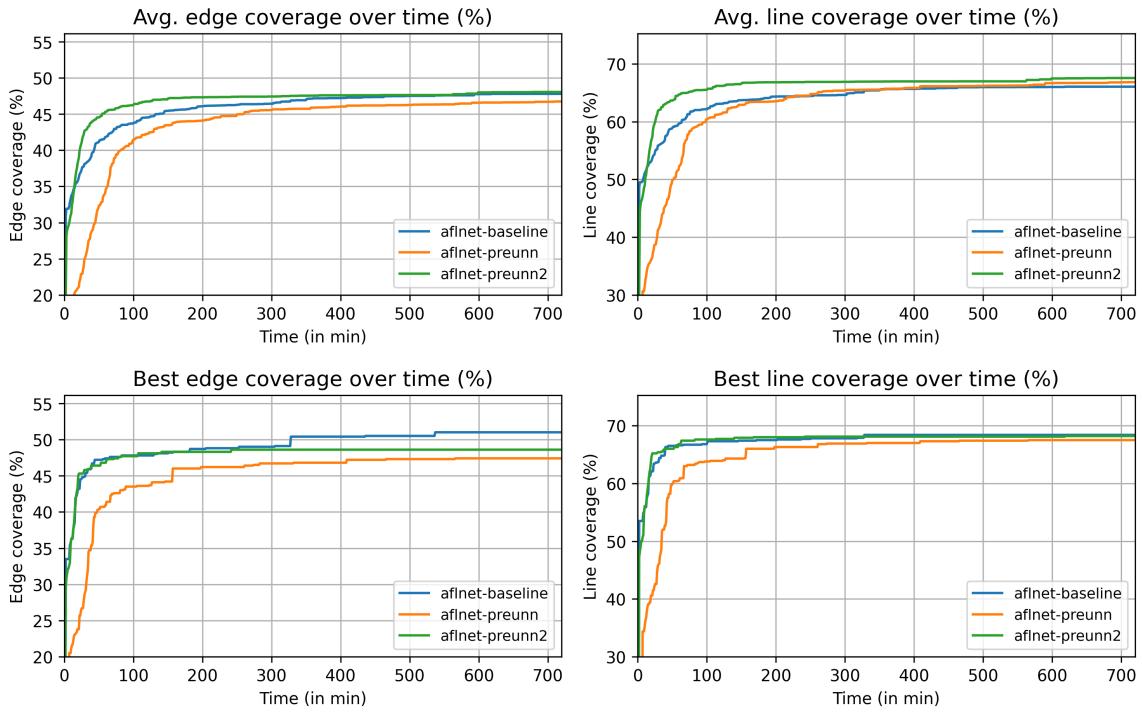

| 5.7.5    | Auswertung der Ergebnisse . . . . .                          | 95        |

| 5.8      | Zusammenfassung . . . . .                                    | 98        |

| 5.9      | Fazit . . . . .                                              | 98        |

|                                                                               |            |

|-------------------------------------------------------------------------------|------------|

| <b>6 Effizientes grammatikbasiertes Fuzzing mittels Large Language Models</b> | <b>101</b> |

| 6.1 Einleitung . . . . .                                                      | 101        |

| 6.2 Stand der Technik . . . . .                                               | 102        |

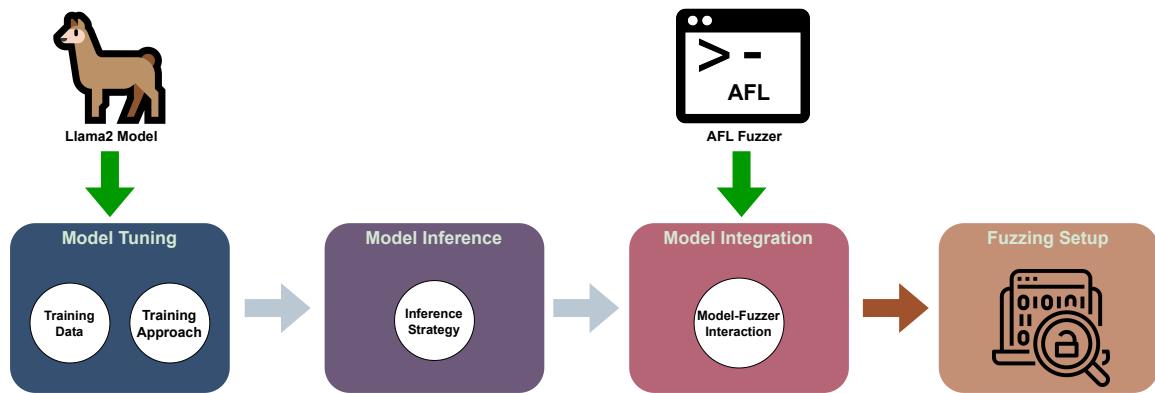

| 6.3 Entwurf . . . . .                                                         | 103        |

| 6.3.1 Datensatz . . . . .                                                     | 104        |

| 6.3.2 Trainingsansatz . . . . .                                               | 105        |

| 6.3.3 Inferenzstrategie . . . . .                                             | 105        |

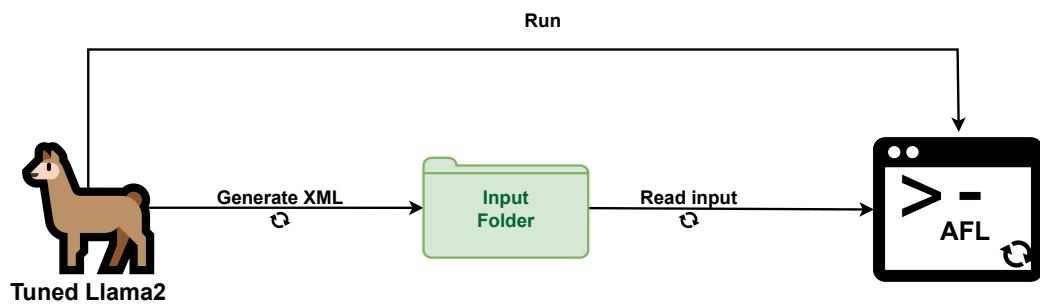

| 6.3.4 Modell-Integration . . . . .                                            | 106        |

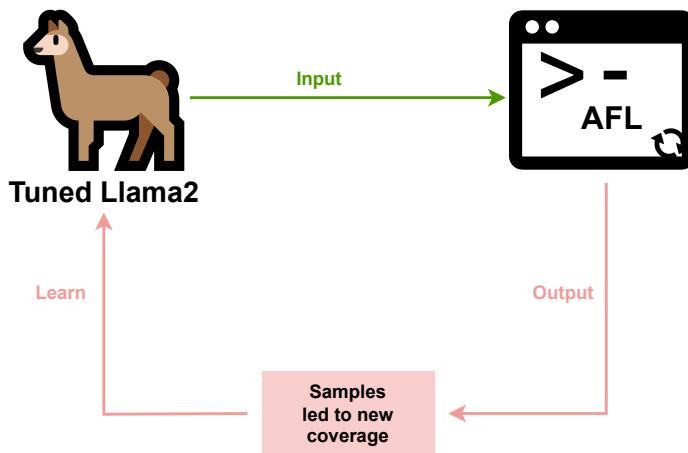

| 6.3.5 Feedback-Schleife . . . . .                                             | 106        |

| 6.4 Implementierung . . . . .                                                 | 107        |

| 6.4.1 Modelltraining und Integration mit AFL . . . . .                        | 107        |

| 6.4.2 Kontinuierlicher Datenintegrationsmechanismus . . . . .                 | 108        |

| 6.4.3 Optimierungstechnologien . . . . .                                      | 108        |

| 6.4.4 Dynamischer Feedback-Mechanismus . . . . .                              | 109        |

| 6.5 Evaluation . . . . .                                                      | 109        |

| 6.5.1 Bewertungsmetriken . . . . .                                            | 109        |

| 6.5.2 Experimentelle Ansätze . . . . .                                        | 110        |

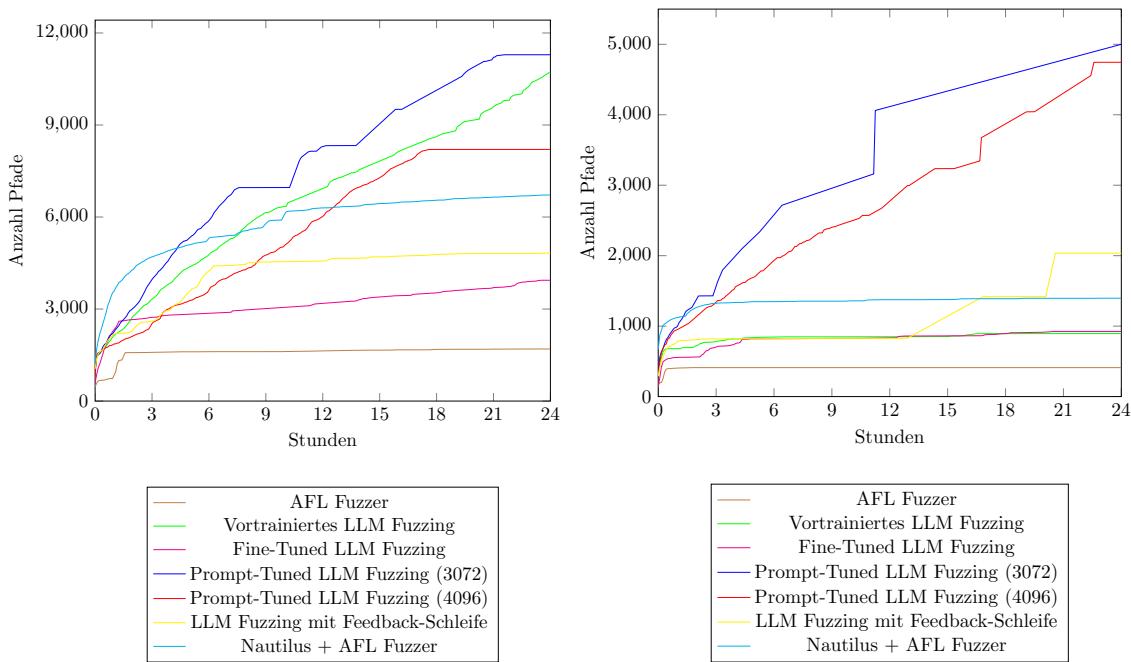

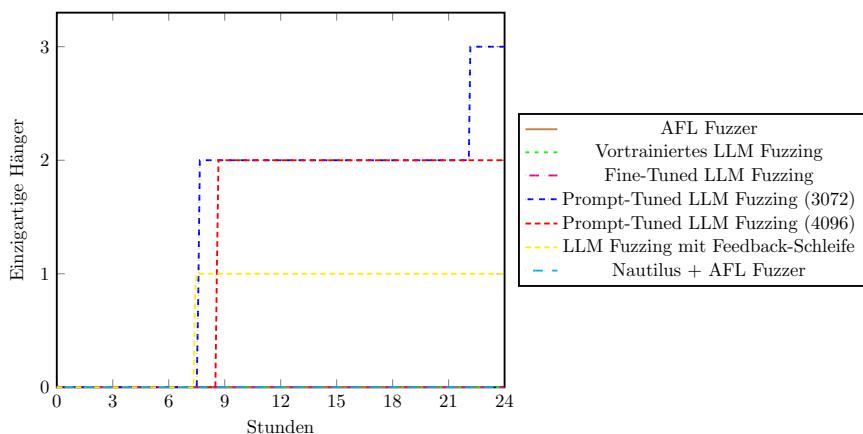

| 6.5.3 Experimentelle Ergebnisse . . . . .                                     | 111        |

| 6.5.4 Inferenzbewertung . . . . .                                             | 113        |

| 6.6 Einschränkungen und zukünftige Arbeiten . . . . .                         | 113        |

| 6.7 Zusammenfassung . . . . .                                                 | 115        |

| 6.8 Fazit . . . . .                                                           | 115        |

| <b>7 Ansatz für ein integriertes Fuzzing-Framework</b>                        | <b>117</b> |

| 7.1 Konzeptionelle Integration der Module . . . . .                           | 117        |

| 7.1.1 Flexibilität der Module . . . . .                                       | 118        |

| 7.1.2 PREUNN und HTTYL als parallele Module . . . . .                         | 118        |

| 7.1.3 Kombination der Module . . . . .                                        | 118        |

| 7.2 Diskussion und Interpretation der Ergebnisse . . . . .                    | 119        |

| 7.3 Limitationen . . . . .                                                    | 120        |

| <b>8 Verwandte Arbeiten</b>                                                   | <b>123</b> |

| 8.1 Binary Rewriting . . . . .                                                | 123        |

| 8.2 Hardware Fuzzing von IoT-Geräten . . . . .                                | 124        |

| 8.3 IoT Fuzzing mittels Emulation . . . . .                                   | 125        |

| 8.4 Fuzzing von Netzwerkprotokollen . . . . .                                 | 126        |

| 8.5 Grammatik-basiertes Fuzzing . . . . .                                     | 127        |

| 8.6 Fuzzing mittels Machine Learning . . . . .                                | 129        |

| 8.7 Optimierung des Fuzzing-Prozesses . . . . .                               | 130        |

| <b>9 Zusammenfassung und Ausblick</b>                                         | <b>133</b> |

| 9.1 Zusammenfassung . . . . .                                                 | 133        |

| 9.2 Ausblick und zukünftige Arbeiten . . . . .                                | 135        |

| <b>Begriffsdefinitionen</b>                                                   | <b>137</b> |

|                              |            |

|------------------------------|------------|

| <b>Abbildungsverzeichnis</b> | <b>146</b> |

| <b>Tabellenverzeichnis</b>   | <b>148</b> |

| <b>Listings</b>              | <b>149</b> |

| <b>Eigene Arbeiten</b>       | <b>153</b> |

| <b>Weitere Literatur</b>     | <b>155</b> |

# Abkürzungsverzeichnis

|                |                                                                          |

|----------------|--------------------------------------------------------------------------|

| <b>AE</b>      | Autoencoder                                                              |

| <b>AFL</b>     | American Fuzzy Lop                                                       |

| <b>AiFF</b>    | Ansatz für ein integriertes Fuzzing-Framework                            |

| <b>API</b>     | Application Programming Interface                                        |

| <b>BCE</b>     | Binary Cross-Entropy                                                     |

| <b>BLE</b>     | Bluetooth Low Energy                                                     |

| <b>BMU</b>     | Best Matching Unit                                                       |

| <b>CCE</b>     | Categorical Cross-Entropy                                                |

| <b>CE</b>      | Cross-Entropy                                                            |

| <b>CISC</b>    | Complex Instruction Set Computer                                         |

| <b>CNN</b>     | Convolutional Neural Network                                             |

| <b>CoAP</b>    | Constrained Application Protocol                                         |

| <b>CSV</b>     | Comma-Separated Values                                                   |

| <b>DBSCAN</b>  | Density-Based Spatial Clustering of Applications with Noise              |

| <b>DDoS</b>    | Distributed Denial of Service                                            |

| <b>DL</b>      | Deep Learning                                                            |

| <b>DoS</b>     | Denial of Service                                                        |

| <b>EBR</b>     | ESP32 Binary Rewriting                                                   |

| <b>ELF</b>     | Executable and Linkable Format                                           |

| <b>EOP</b>     | End of Package                                                           |

| <b>EQF</b>     | ESP32-QEMU-FUZZ                                                          |

| <b>FTP</b>     | File Transfer Protocol                                                   |

| <b>GAN</b>     | Generative Adversarial Network                                           |

| <b>GDB</b>     | GNU Debugger                                                             |

| <b>GPU</b>     | Graphics Processing Unit                                                 |

| <b>HDBSCAN</b> | Hierarchical Density-Based Spatial Clustering of Applications with Noise |

| <b>HTTP</b>    | Hypertext Transfer Protocol                                              |

| <b>HTTYL</b>   | How to Train Your Llama                                                  |

| <b>IDF</b>     | IoT Development Framework                                                |

| <b>IoT</b>     | Internet of Things                                                       |

| <b>IR</b>      | Intermediate Representation                                              |

| <b>ISA</b>     | Instruction Set Architecture                                             |

| <b>ISO</b>     | International Organization for Standardization                           |

| <b>KI</b>      | Künstliche Intelligenz                                                   |

| <b>KNN</b>     | Künstliches Neuronales Netz                                              |

| <b>LLM</b>     | Large Language Model                                                     |

| <b>LoRA</b>    | Low-Rank Adaptation                                                      |

|                |                                                    |

|----------------|----------------------------------------------------|

| <b>LSTM</b>    | Long Short-Term Memory                             |

| <b>ML</b>      | Machine Learning                                   |

| <b>MQTT</b>    | Message Queueing Telemetry Transport               |

| <b>MSB</b>     | Most Significant Bit                               |

| <b>MSE</b>     | Mean Squared Error                                 |

| <b>NLL</b>     | Negative Log-Likelihood                            |

| <b>NVS</b>     | Non-Volatile Storage                               |

| <b>PEFT</b>    | Parameter-Efficient Fine-Tuning                    |

| <b>PoC</b>     | Proof of Concept                                   |

| <b>PREUNN</b>  | Protocol Reverse Engineering using Neural Networks |

| <b>PRE</b>     | Protocol Reverse Engineering                       |

| <b>PUT</b>     | Program Under Test                                 |

| <b>ReLU</b>    | Rectified Linear Unit                              |

| <b>RISC</b>    | Reduced Instruction Set Computer                   |

| <b>RNN</b>     | Recurrent Neural Network                           |

| <b>Seq2Seq</b> | Sequence to Sequence                               |

| <b>SOM</b>     | Self-Organizing Map                                |

| <b>SOP</b>     | Start of Package                                   |

| <b>TCP</b>     | Transmission Control Protocol                      |

| <b>TPU</b>     | Tensor Processing Unit                             |

| <b>TTM</b>     | Time-to-Market                                     |

| <b>UDP</b>     | User Datagram Protocol                             |

| <b>XML</b>     | Extensible Markup Language                         |

| <b>XMPP</b>    | Extensible Messaging and Presence Protocol         |

# 1 Einleitung

Dieses Kapitel führt in die Dissertation ein und erläutert ihre wissenschaftliche Relevanz. Im Fokus stehen die Sicherheit im Internet der Dinge (engl. Internet of Things, kurz IoT) und das Fuzzing von IoT-Geräten als zentrale Forschungsfelder. Anschließend werden die Ziele und Beiträge der Dissertation vorgestellt sowie ihr Aufbau erläutert.

## 1.1 Motivation

In den letzten Jahren ist die Anzahl von IoT-Geräten signifikant gewachsen. Intelligente Sensoren und vernetzte Geräte finden zunehmend Anwendung in der Industrie, in Smart-Home-Systemen und in der kritischen Infrastruktur. Laut Fortune Business Insights betrug die weltweite Marktgröße für IoT im Jahr 2019 rund \$251 Milliarden und wird bis 2027 voraussichtlich auf über \$1,463 Milliarden anwachsen [For20]. Trotz dieser Dynamik wurden Sicherheitsaspekte in der IoT-Entwicklung lange vernachlässigt. Der IoT Threat Report 2020 zeigt, dass 57 % der untersuchten Geräte Schwachstellen mittlerer oder hoher Schwere aufwiesen [Uni20]. Dies macht IoT-Systeme zu attraktiven Zielen für Angriffe, beispielsweise können sie übernommen und in sogenannte Botnetze vereint werden, die dann ferngesteuert für Distributed Denial of Service (DDoS)-Angriffe genutzt werden, um Webseiten lahmzulegen [BSI25].

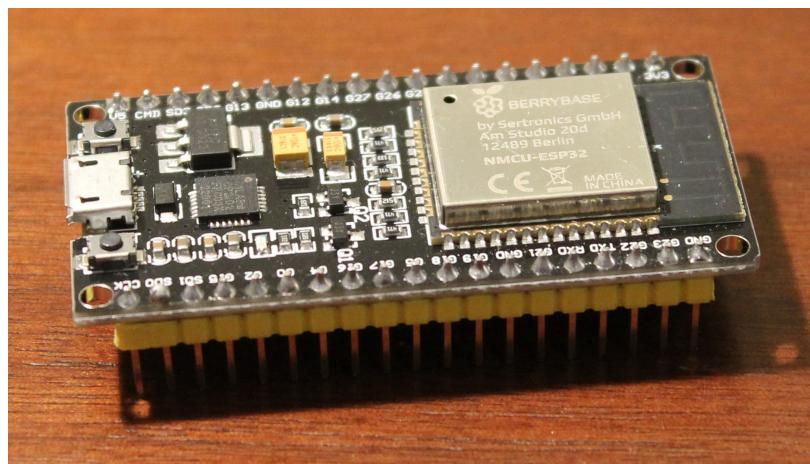

Eine wichtige Rolle in der IoT-Landschaft spielt der ESP32-Mikrocontroller, der 2016 veröffentlicht und seitdem über 100 Millionen Mal verkauft wurde [Esp18; Eli22]. Aufgrund seiner hohen Integrationsdichte, des günstigen Preises und der Unterstützung von WLAN- und Bluetooth-Kommunikation ist der ESP32 in zahlreichen kommerziellen Produkten weit verbreitet [Mil21]. Seine Popularität macht ihn zugleich zu einem lohnenden Ziel für Angreifer.

Ein zentrales Problem in der IoT-Entwicklung ist das sogenannte Time-to-Market (TTM)-Dilemma: Um möglichst schnell marktreife Produkte zu liefern, wird IT-Sicherheit oft nachrangig behandelt oder erst nachträglich berücksichtigt [Bau+19]. Dies führt regelmäßig zu gravierenden Sicherheitslücken, die Angreifern einen einfachen Zugang zu sensiblen Daten oder vollständige Kontrolle über Geräte ermöglichen [Kre16].

Eine etablierte Methode zur Identifikation von Sicherheitslücken ist neben der statischen Codeanalyse das *Fuzzing* [Lia+18; GPS17]. Dabei wird Software automatisiert mit zufälligen oder gezielt generierten Eingaben getestet, um fehlerhafte Zustände wie Abstürze, Speicherlecks oder unbehandelte Ausnahmen zu provozieren. Ein vollständiges Durchtesten aller möglichen Eingaben wäre ideal, ist in der Praxis jedoch aufgrund der enormen

Größe des Eingaberaums nicht realisierbar [AIB11]. Stattdessen werden gezielte Strategien eingesetzt, um den Suchraum effizient einzugrenzen.

Typische Ziele des Fuzzings sind Software-Komponenten, Netzwerkprotokolle, Schnittstellen oder Anwendungen, wie etwa XML-Parser. Durch die systematische Eingabe fehlerhafter, unerwarteter oder zufälliger Daten lassen sich Schwachstellen und Stabilitätsprobleme aufdecken. Mithilfe von Fuzzing lassen sich unter anderem Pufferüberläufe, Speicherlecks, unbehandelte Ausnahmen und Logikfehler identifizieren [TDM08].

Im Kontext des IoT stößt Fuzzing jedoch auf besondere Herausforderungen. Zum einen sind viele Geräte durch knappe Hardware-Ressourcen wie begrenzten Speicher, geringe Rechenleistung und fehlende Debugging-Schnittstellen eingeschränkt, was die direkte Analyse auf den Geräten erheblich erschwert [Yun+22; Tou+24]. Zum anderen führt die große Vielfalt an Mikrocontroller-Architekturen und Betriebssystemen dazu, dass etablierte Fuzzing-Tools nur eingeschränkt wiederverwendet werden können [Mue+18]. Darüber hinaus setzen IoT-Geräte häufig auf komplexe Kommunikationsschnittstellen wie WLAN, Bluetooth Low Energy (BLE) oder ZigBee, deren vielfältige Zustandsräume das systematische Testen zusätzlich erschweren [Tou+24].

Um diese Probleme gezielt anzugehen, bieten sich zwei technische Ansätze an. Binary Rewriting adressiert insbesondere die Einschränkungen durch fehlende Debugging-Schnittstellen und begrenzte Ressourcen: Durch das gezielte Injektieren von Analysecode in Firmware-Binaries kann die Codeabdeckung verfolgt und der Kontrollfluss direkt an den Fuzzer zurückgemeldet werden, ohne das ursprüngliche Verhalten zu verändern [DGR20]. Dadurch wird das Testen selbst auf ressourcenarmen Geräten ermöglicht. Emulation ergänzt diesen Ansatz, indem die Firmware in einer kontrollierten und reproduzierbaren Umgebung ausgeführt wird. Dadurch lassen sich interne Zustände, Speicherzugriffe und Kommunikationsabläufe beobachten, während sich Fuzzing-Kampagnen parallelisieren und beschleunigen lassen. Gleichzeitig reduziert die Emulation die Abhängigkeit von der konkreten Hardwarearchitektur und erleichtert so die Wiederverwendbarkeit der Tests über verschiedene Geräte hinweg [Cle+20; Wri+21; Yun+22].

Darüber hinaus eröffnen Künstliche Intelligenz (KI)-gestützte Methoden neue Perspektiven für das Fuzzing. Verfahren aus den Bereichen Machine Learning (ML) und Deep Learning (DL) werden bereits erfolgreich in der statischen Codeanalyse, Malware-Erkennung und Spam-Filterung eingesetzt [DB25; Kna+25; KY24; GAJ24]. Im Fuzzing ermöglichen diese Methoden eine gezielte Optimierung der Eingabegenerierung: Mithilfe von Mustererkennung können Protokollstrukturen approximiert und synthetische, wohldefinierte Testdaten erzeugt werden. Dadurch steigt die Wahrscheinlichkeit, dass Eingaben vom Program Under Test (PUT) akzeptiert werden, was die Testabdeckung verbessert und die Effizienz der Schwachstellensuche erheblich steigert [Zha+24a].

## 1.2 Zielsetzung und wissenschaftlicher Beitrag

Die zentrale Forschungsfrage dieser Dissertation lautet:

„Wie kann das Fuzzing von IoT-Geräten effizienter gestaltet werden?“

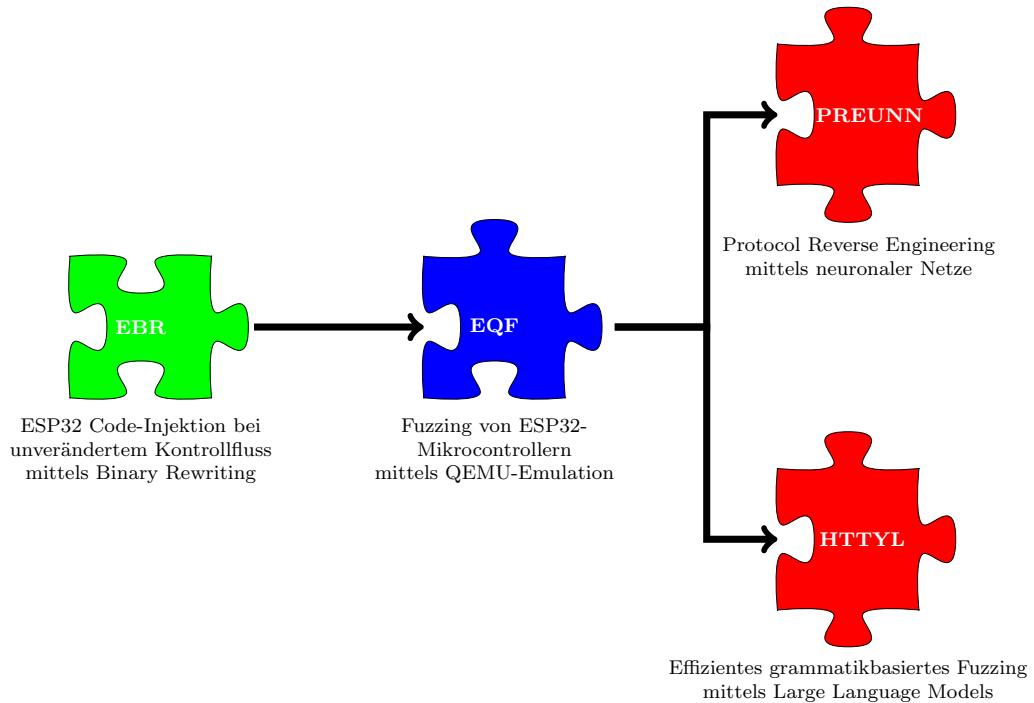

Zu diesem Zweck wird ein konzeptionelles Framework für ESP32-Anwendungen entwickelt. Dieses Framework integriert verschiedene Ansätze zur Effizienzsteigerung systematisch und macht deren Synergien nutzbar (siehe Definition von effizientem Fuzzing in Abschnitt 2.4.7). Der ESP32 dient dabei als exemplarische Plattform, da seine Architektur die typischen Einschränkungen ressourcenarmer IoT-Geräte, wie begrenzte Rechenleistung, Speicher- und Energie-Ressourcen, widerspiegelt. Als methodische Grundlage werden vier Techniken realisiert: ESP32 Code-Injektion bei unverändertem Kontrollfluss mittels Binary Rewriting, Fuzzing von ESP32-Mikrocontrollern mittels QEMU-Emulation, Protocol Reverse Engineering (PRE) mittels neuronaler Netze und effizientes grammatikbasiertes Fuzzing mittels Large Language Models (LLMs). Die praktischen Implementierungen demonstrieren den Nutzen dieser Ansätze, während das Framework ihre flexible Kombination für unterschiedliche Anwendungsszenarien aufzeigt.

Die wesentlichen Beiträge dieser Dissertation lassen sich wie folgt zusammenfassen:

- **ESP32 Code-Injektion bei unverändertem Kontrollfluss mittels Binary Rewriting:** Beim Binary Rewriting kann beliebiger Code nachträglich in ein Programm eingefügt werden, ohne dessen ursprüngliches Verhalten zu verändern. Dazu zählt auch die Instrumentierung, also Code, der während der Ausführung zusätzliche Informationen erfasst – beispielsweise über Speicherzugriffe, Funktionsaufrufe oder den Kontrollfluss. Bislang existierten Ansätze hierfür nur für andere Architekturen wie x86 und ARM. Eine zentrale Herausforderung bestand darin, diese Technik für die Xtensa-Architektur des ESP32 technisch umsetzbar zu machen. Es wurde ein Verfahren entwickelt, das den Binärkode erfolgreich modifiziert und erlaubt relevante Laufzeitinformationen direkt an den Fuzzer zu übertragen. Dadurch wird die Analyse beschleunigt und die Datenmenge reduziert. Praktische Tests zeigen, dass sämtliche Instrumentierungen korrekt ausgeführt werden und die Integrität der ursprünglichen Firmware erhalten bleibt.

- **Fuzzing von ESP32-Mikrocontrollern mittels QEMU-Emulation:** Auf Basis von QEMU wurde eine vollständige Emulationsumgebung mit einem integrierten Fuzzer für den ESP32 realisiert. Die zentrale Herausforderung bestand einerseits darin, die Emulationssoftware inklusive der fehlenden Hardwarekomponenten (z. B. WLAN-Unterstützung) durch gezielte Anpassungen so zu verändern, dass beliebige ESP32-Software lauffähig wird. Andererseits musste ein Fuzzer nahtlos in die Emulation integriert werden, um automatisierte Tests innerhalb derselben Umgebung zu ermöglichen. Das resultierende System erlaubt direkten Zugriff auf interne Systeminformationen und erleichtert die effiziente Erkennung von Speicherfehlern und Schwachstellen. Zudem ermöglicht es parallele Ausführung und schnellere Fuzzing-Durchläufe auf der leistungsstarken PC-Hardware, was die Effizienz erheblich

steigert. Für den Vergleich wurde auf Parallelisierung verzichtet, um gleiche Bedingungen zur Hardwareausführung sicherzustellen: Während hardwarebasiertes Fuzzing vier bis 40 Eingaben pro Sekunde verarbeitet, erreicht die Emulation bis zu 320 Eingaben pro Sekunde.

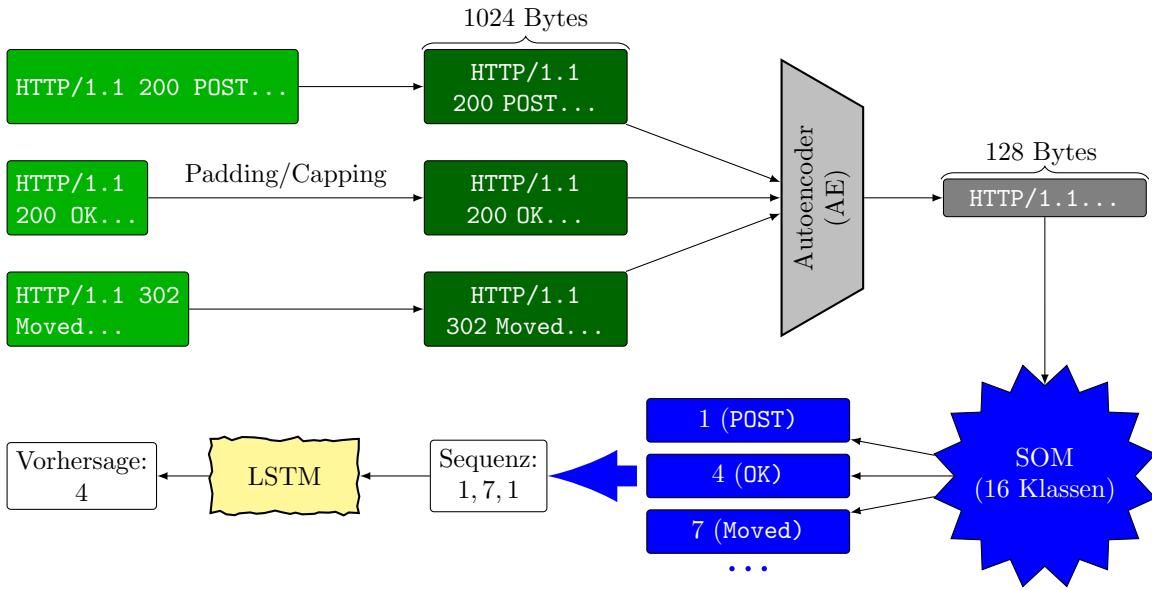

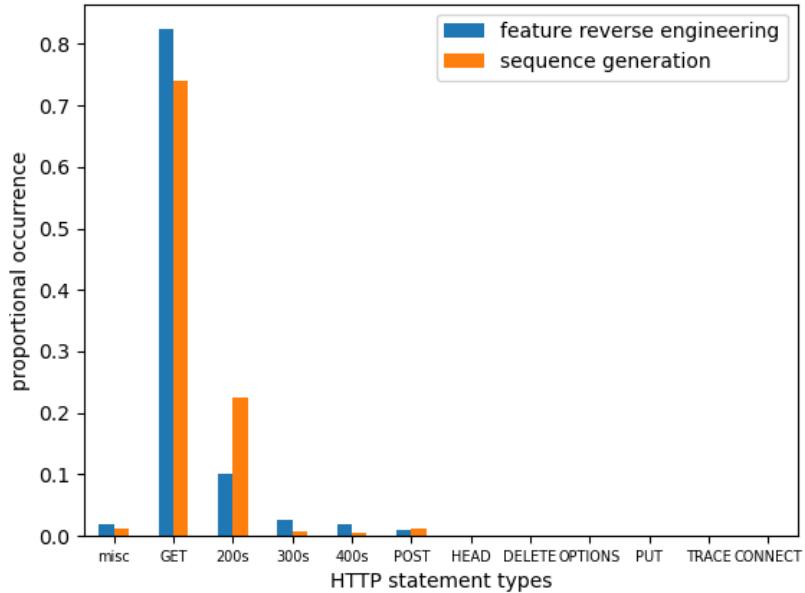

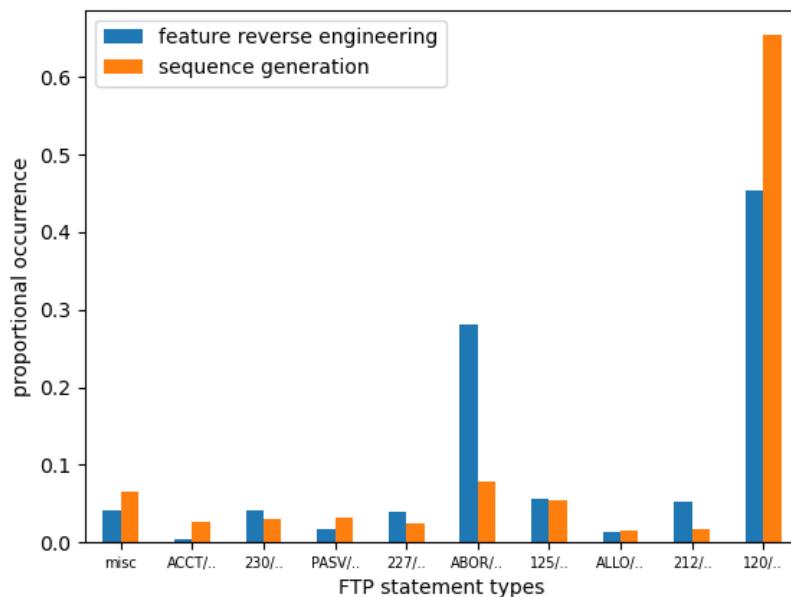

- **Protocol Reverse Engineering mittels neuronaler Netze:** Es wurde ein KI-basierter Ansatz für das automatisierte PRE von Netzwerkprotokollen entwickelt. Die zentrale Herausforderung bestand darin, geeignete ML- und DL-Modelle auszuwählen und zu kombinieren, um Protokollstrukturen ohne vorhandene Spezifikationen zuverlässig abzuleiten. Während das PRE bisher manuell durchgeführt werden musste, lassen sich mit diesem Ansatz nun Protokollstrukturen automatisiert ableiten und syntaktisch sowie semantisch korrekte Netzwerkpakete erzeugen. In den Tests waren 67,6 % der generierten Hypertext Transfer Protocol (HTTP)-Pakete und 100 % der File Transfer Protocol (FTP)-Pakete gültig. Dadurch erhöht sich die Testabdeckung signifikant, da im Vergleich zu zufällig generierten Daten ein größerer Anteil der Eingaben vom PUT akzeptiert wird und somit verwertbare Rückmeldungen erzeugt werden, statt sofort als ungültig verworfen zu werden.

- **Effizientes grammatikbasiertes Fuzzing mittels Large Language Models:** Für den Fuzzing-Prozess wurde ein Ansatz entwickelt, der mithilfe von LLMs syntaktisch und semantisch korrekte Dateien (z. B. Extensible Markup Language (XML)-Dateien) als Eingaben erzeugt. Die zentrale Herausforderung bestand darin, die LLMs effizient in bestehende Testabläufe zu integrieren. Im Rahmen dieser Untersuchung konnte gezeigt werden, dass diese Integration erfolgreich umgesetzt werden kann. Die Programmflussabdeckung steigt im Vergleich zu Ausführungen ohne LLM um den Faktor 6 und erreicht zudem eine um 50 % höhere Abdeckung, als klassische grammatikbasierte Fuzzer.

- **Ansatz für ein integriertes Fuzzing-Framework:** Es wird ein Ansatz vorgestellt, bei dem die vier vorgestellten Techniken flexibel kombiniert werden, um Synergien gezielt zu nutzen. Binary Rewriting ermöglicht eine effiziente Gewinnung von Laufzeitinformationen und unterstützt die Schwachstellenerkennung. Die Emulation erhöht die Anzahl der pro Sekunde verarbeiteten Eingaben und trägt ebenfalls zur Verbesserung der Schwachstellenerkennung bei. Je nach Anwendungsfall können mit dem PRE-Ansatz entweder gültige Netzwerkpakete automatisiert generiert oder mit dem LLM-Ansatz strukturierte Eingabedateien (z. B. im XML-Format) erstellt werden. Das Konzept zeigt, dass sich die Effizienzsteigerungen der einzelnen Methoden kombinieren lassen, um die Gesamteffektivität der Testgenerierung zu erhöhen.

Die Dissertation beantwortet somit die Frage, wie das Fuzzing von IoT-Geräten effizienter gestaltet werden kann. Zu diesem Zweck werden vier Ansätze vorgestellt und ein konzeptionelles Framework zu deren Kombination entwickelt. Damit schließt sie zentrale Forschungslücken im Bereich des Fuzzings von IoT-Geräten, insbesondere bei ressourcenschwachen Plattformen und heterogenen Protokollen. Gleichzeitig demonstriert sie die Machbarkeit und Effektivität der Methoden und schafft eine fundierte Grundlage für die praxisnahe Absicherung von IoT-Geräten.

## 1.3 Aufbau der Dissertation

Die Dissertation ist so strukturiert, dass zunächst die theoretischen Grundlagen vermittelt und anschließend die entwickelten Methoden, ihre Umsetzung und ihre Anwendung im IoT-Fuzzing systematisch vorgestellt werden.

Kapitel 2 (Grundlagen) führt in die grundlegenden Konzepte ein, die für das Verständnis der Dissertation erforderlich sind. Neben den theoretischen Grundlagen des Fuzzings werden auch die Besonderheiten der Sicherheitsanalyse von IoT-Geräten erläutert.

Kapitel 3 (ESP32 Code-Injektion bei unverändertem Kontrollfluss mittels Binary Rewriting) stellt die Methode des Binary Rewriting vor und erläutert die Umsetzung für den ESP32-Mikrocontroller. Es wird gezeigt, wie sich Firmware gezielt instrumentieren lässt, um relevante Laufzeitinformationen ohne vollständiges Speicherauslesen an den Fuzzer zu übertragen. Dies schafft die Grundlage für effizientere Testabläufe.

In Kapitel 4 (Fuzzing von ESP32-Mikrocontrollern mittels QEMU-Emulation) wird die Umsetzung praxisnaher Fuzzing-Methoden am Beispiel des ESP32-Mikrocontrollers beschrieben. Es wird erläutert, wie durch Emulation die Einschränkungen realer Hardware umgangen und parallele Fuzzing-Instanzen realisiert werden können.

Kapitel 5 (Protocol Reverse Engineering mittels neuronaler Netze) erläutert die KI-gestützte Protokollanalyse. Es wird beschrieben, wie mittels PRE unbekannte textbasierte Kommunikationsprotokolle aus dem Datenverkehr rekonstruiert und durch den Einsatz von neuronalen Netzwerken gezielt valide Netzwerkpakete als Eingaben für das Fuzzing erzeugt werden.

Kapitel 6 (Effizientes grammatikbasiertes Fuzzing mittels Large Language Models) behandelt den Einsatz von LLMs zur Generierung von Eingaben. Es wird gezeigt, wie diese Modelle variantenreiche, syntaktisch und semantisch korrekte Eingaben für komplexe Programme erzeugen.

In Kapitel 7 (Ansatz für ein integriertes Fuzzing-Framework) wird ein konzeptioneller Ansatz zur Kombination der vier vorgestellten Techniken beschrieben. Es wird erläutert, welche Synergieeffekte möglich sind und wie unterschiedliche Anwendungsfälle von einer Integration profitieren könnten.

In Kapitel 8 (Verwandte Arbeiten) werden die vorgestellten Verfahren in den aktuellen Stand der Forschung eingeordnet und bestehende Ansätze sowie deren Limitationen aufgezeigt.

Kapitel 9 (Zusammenfassung und Ausblick) fasst die wichtigsten Ergebnisse der Dissertation zusammen und gibt einen Ausblick auf zukünftige Forschungsrichtungen im Bereich IoT-Fuzzing.

## 2 Grundlagen

Dieses Kapitel legt die theoretischen und technischen Grundlagen, die für diese Dissertation erforderlich sind. Es werden zentrale Konzepte aus den Bereichen IoT-Geräte, Mikrocontroller-Architekturen, Binary Rewriting, Fuzzing, Netzwerkprotokolle und neuronale Netzwerke systematisch vorgestellt. Ziel ist es, ein einheitliches Verständnis zu schaffen, das die spätere Analyse und praktische Umsetzung erleichtert.

Zu Beginn widmet sich das Kapitel den Besonderheiten von IoT-Geräten, die sich durch spezifische Architekturen, Kommunikationsprotokolle und Fuzzing-Herausforderungen auszeichnen. Anschließend wird der ESP32-Mikrocontroller als exemplarische Plattform mit seiner Architektur, Firmware-Struktur und der Xtensa-Instruction Set Architecture (ISA) vorgestellt. Darauf aufbauend werden die wesentlichen Konzepte des Binary Rewritings sowie die Grundlagen des Fuzzings einschließlich grammatischem Fuzzing und der Nutzung von Emulatoren präsentiert. Abschließend werden relevante Netzwerkprotokolle wie Protocol Reverse Engineering erläutert. Zentrale neuronale Netzwerkarchitekturen und weitere grundlegende Definitionen, die die methodische und theoretische Basis dieser Dissertation bilden, werden abschließend präsentiert.

### 2.1 Besonderheiten von IoT-Geräten

IoT-Geräte weisen spezifische Eigenschaften auf, die sie von klassischen Computersystemen unterscheiden. Dazu zählen ihre starke Heterogenität, die Beschränkung der Hardware-Ressourcen, spezielle Kommunikationsprotokolle sowie vielfältige Einsatzumgebungen. Diese Faktoren haben unmittelbare Konsequenzen für die Entwicklung, die Sicherheit und die Testverfahren. Dies ist besonders relevant für den Einsatz von Fuzzing, das sich an die besonderen Randbedingungen dieser Geräte anpassen muss.

#### 2.1.1 Architekturen und Protokolle von IoT-Geräten

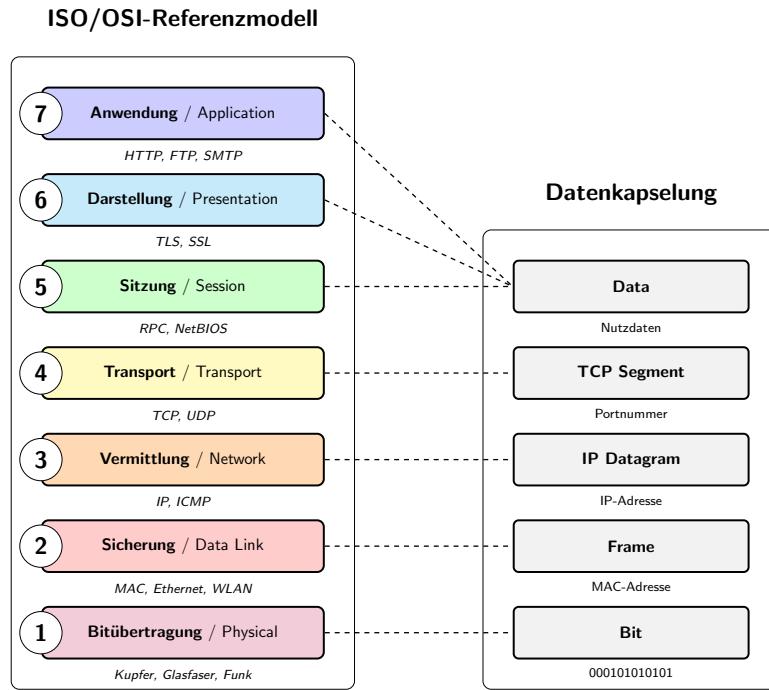

IoT-Geräte bestehen typischerweise aus eingebetteten Hardwareplattformen, die mit Sensoren, Aktoren und Kommunikationsmodulen ausgestattet sind. Typische Architekturen umfassen mikrocontrollerbasierte Systeme wie den ESP32 oder STM32, Einplatinencomputer wie den Raspberry Pi sowie FPGA-basierte Lösungen für spezialisierte Anwendungen [SBV23]. Zur Kommunikation nutzen IoT-Geräte standardisierte Protokolle auf Basis von TCP/IP [Pos81a; Pos81b], wie Message Queueing Telemetry Transport (MQTT) [Ban+19], Constrained Application Protocol (CoAP) [SHB14], Extensible

Tabelle 2.1: Übersicht über verschiedene 32-Bit-Mikrocontroller. Quelle: [SBV23]

| Mikrocontroller           | Taktfrequenz | RAM    | Schnittstellen                         |

|---------------------------|--------------|--------|----------------------------------------|

| STM32F4 [STM25]           | 180 MHz      | 96 KB  | UART, SPI, I <sup>2</sup> C            |

| Raspberry Pi Pico [Ras24] | 133 MHz      | 264 KB | UART, SPI, I <sup>2</sup> C            |

| ESP8266 [Esp23]           | 80 MHz       | 96 KB  | UART, SPI, I <sup>2</sup> C (Software) |

| ESP32 [Esp25a]            | 240 MHz      | 520 KB | UART, SPI, I <sup>2</sup> C, WLAN, BLE |

Messaging and Presence Protocol (XMPP) [Sai11] und HTTP [Nie+99], beispielsweise für REST-Application Programming Interfaces (APIs) [Fie00]. Außerdem nutzen sie verschiedene Technologien wie Bluetooth Low Energy (BLE) [Blu23], Z-Wave [Z-W21] und ZigBee [Con23] für die Kurzstreckenkommunikation. Diese sind speziell auf die ressourcenbeschränkten Anforderungen von IoT-Geräten zugeschnitten und ermöglichen eine effiziente Datenübertragung in verschiedenen Anwendungsbereichen [Has+19].

### 2.1.2 Herausforderungen beim Fuzzing von IoT-Geräten

Das Fuzzing von IoT-Geräten stellt aufgrund der begrenzten Rechenressourcen und spezifischen Hardwarearchitekturen besondere Anforderungen an Fuzzing-Methoden dar. Repräsentative IoT-Plattformen auf Basis von 32-Bit-Mikrocontrollern wie dem STM32F4 [STM25], dem Raspberry Pi Pico [Ras24], dem ESP8266 [Esp23] oder dem ESP32 [Esp25a] verfügen typischerweise über folgende Ressourcen [SBV23]:

- **Rechenleistung:** Prozessoren mit Taktfrequenzen von 80 MHz bis zu 240 MHz

- **Speicher:** RAM-Kapazitäten zwischen 32 KB und 520 KB

- **Kommunikationsschnittstellen** [Gup19]: UART, SPI, I<sup>2</sup>C, WLAN, BLE

Tabelle 2.1 gibt eine exemplarische Übersicht über gängige 32-Bit-Mikrocontroller und verdeutlicht die Vielfalt verfügbarer Plattformen. Die begrenzten Ressourcen von IoT-Geräten wirken sich direkt auf die Durchführung von Fuzzing (siehe Abschnitt 2.4) aus. Die eingeschränkte Speicherkapazität limitiert die Verwaltung umfangreicher Testdaten im Arbeitsspeicher, während die begrenzte Rechenleistung die Anzahl gleichzeitig verarbeitbarer Eingaben limitiert. Zusätzlich können langsame Kommunikationsschnittstellen die Geschwindigkeit der Fehlerdetektion erheblich reduzieren. Darüber hinaus erfordern unterschiedliche Hardware- und Softwarekonfigurationen spezifische Anpassungen der Fuzzing-Methoden, was die Entwicklung universell einsetzbarer Fuzzer zusätzlich erschwert [SBV23].

## 2.2 ESP32 Mikrocontroller

Für diese Dissertation wurde der ESP32 (siehe Abbildung 2.1) als repräsentatives IoT-Gerät ausgewählt, da er zu den am weitesten verbreiteten Mikrocontrollern zählt und breit in

Abbildung 2.1: NMCU-ESP32: Ein ESP32 auf einem NodeMCU-Entwicklungsboard.

Forschung sowie Industrie eingesetzt wird. Der ESP32 bietet eine moderne Architektur mit integrierter WLAN- und Bluetooth-Konnektivität und unterstützt zahlreiche Schnittstellen. Diese Eigenschaften machen ihn zu einer vielseitigen Plattform, die typische Merkmale moderner IoT-Geräte repräsentiert. Darüber hinaus zeichnet sich der ESP32 durch seine offene Dokumentation, eine aktive Community und gute Verfügbarkeit aus, was ihn besonders geeignet macht, um experimentelle Ansätze systematisch zu untersuchen und zu evaluieren [Esp18; Eli22].

### 2.2.1 Architektur

Die ESP32-Familie von Espressif Systems umfasst energieeffiziente und kostengünstige Mikrocontroller, die speziell für IoT-Anwendungen entwickelt wurden. Im Vergleich zum Vorgängermodell ESP8266 verfügt der ESP32 über erweiterte Fähigkeiten hinsichtlich Rechenleistung, Speicherausstattung und Schnittstellenvielfalt. Abhängig von der Variante kommen entweder einzelne oder duale Xtensa LX6-Kerne [Cad25] bzw. LX7-Kerne [Cad24] oder ein Reduced Instruction Set Computer (RISC)-V-Kern [Wat+16; Esp25b] zum Einsatz. Während der LX7 gegenüber dem LX6 vor allem durch höhere Taktraten und optimierte Pipeline-Architektur mehr Leistung bietet, zeichnet sich RISC-V durch seine Offenheit, Modularität und breite Unterstützung in der Embedded-Community aus. Dabei implementieren alle Versionen die Xtensa-ISA (siehe Abschnitt 2.2.3) – eine anpassbare und erweiterbare RISC-basierte Befehlssatzarchitektur [Esp25a].

In dieser Dissertation wird der **ESP32-WR00M-32** [Esp25c] als Referenzplattform verwendet. Die wesentlichen technischen Eigenschaften sind in Tabelle 2.2 aufgeführt. Dank seiner integrierten WLAN- und BLE-Funktionen, seiner vergleichsweise hohen Rechenleistung und seines geringen Energieverbrauchs eignet sich der ESP32 besonders für ressourcenbeschränkte IoT-Szenarien. Gleichzeitig ist er aufgrund seiner in der Regel niedrigen Anschaffungskosten und seiner Vielseitigkeit auch in industriellen Anwendungen weit

Tabelle 2.2: Technische Spezifikationen des ESP32-WROOM-32 [Esp25c]

| Eigenschaft           | Wert              |

|-----------------------|-------------------|

| Mikroarchitektur      | Xtensa 32-bit LX6 |

| CPU-Kerne             | 2                 |

| Maximale Taktfrequenz | 240 MHz           |

| Flash-Speicher        | 4 MB              |

| ROM                   | 448 KB            |

| SRAM                  | 520 KB            |

| WLAN                  | IEEE 802.11 b/g/n |

| Bluetooth             | Classic und BLE   |

verbreitet. Dies unterstreichen nicht nur die hohen Verkaufszahlen, die bereits 2018 die Marke von 100 Millionen ausgelieferten Einheiten überschritten, sondern auch Berichte, die den ESP32 als wichtigen Treiber für vernetzte Anwendungen im Kontext von Industrie 4.0 und Industrie 5.0 hervorheben [Esp18; AAZ25].

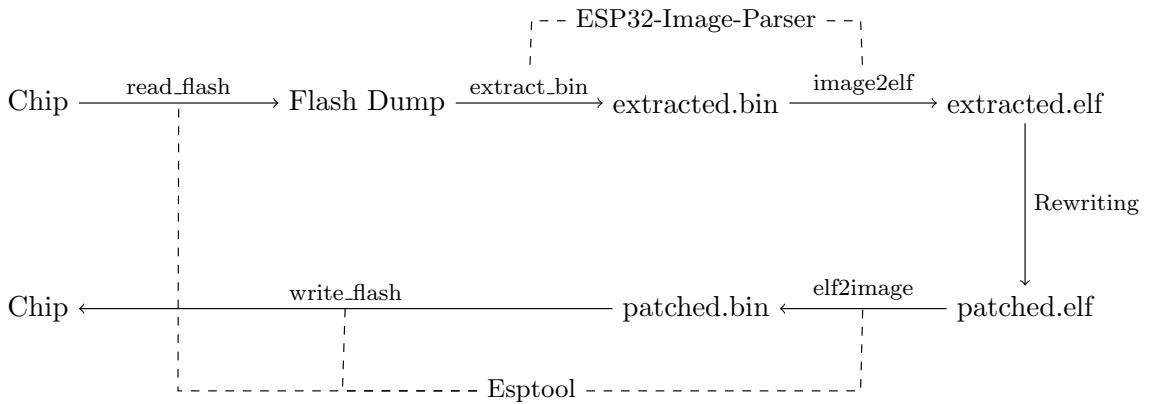

## 2.2.2 Firmware

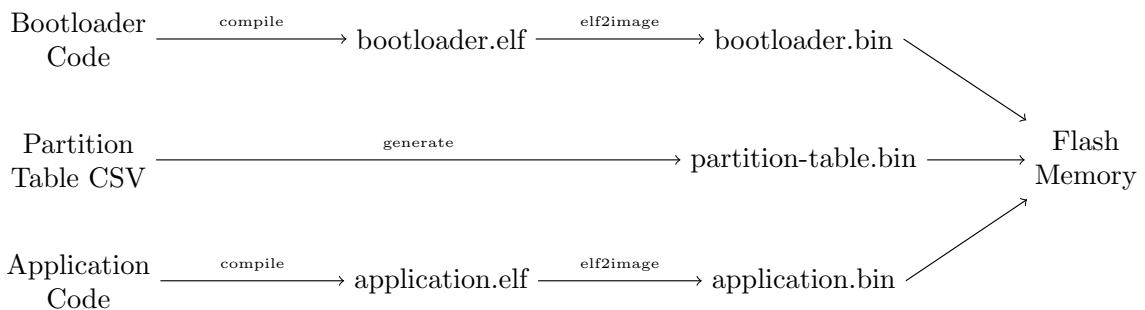

Eine Übersicht über die ESP32-Firmware ist in Abbildung 2.2 zu finden. Die Firmware enthält drei Hauptkomponenten: den Bootloader, die Partitionstabelle und mindestens eine App-Partition, die den Anwendungscode enthält. Der Bootloader und der Anwendungscode werden in Executable and Linkable Format (ELF)-Binärdateien kompiliert und anschließend in ein Binärformat umgewandelt, das für den ESP32 geeignet ist [Cir25].

Diese Binärdateien werden zusammen auf den Mikrocontroller geflasht. Obwohl sie nicht zu einer Datei zusammengefasst werden, werden der Bootloader, die Partitionstabelle und das Anwendungsabbild in dieser Dissertation gemeinsam als Firmware-Abbild bezeichnet. Das Modifizieren oder Austauschen einer dieser Komponenten führt in der Regel dazu, dass die Firmware nicht mehr korrekt funktioniert.

### 2.2.2.1 Bootloader

Der Bootloader wird zuerst ausgeführt, wenn der ESP32 eingeschaltet oder zurückgesetzt wird. Er initialisiert die Hardware, stellt die Systemuhr ein, konfiguriert den Speicher und überprüft die Integrität des Anwendungscodes, bevor er die Kontrolle an die Anwendung übergibt [Cir25].

### 2.2.2.2 Partitionstabelle

Die Partitionstabelle definiert die Anordnung des Flash-Speichers des ESP32, einschließlich der Position und Größe des Bootloaders, der Anwendung und anderer Partitionen.

Abbildung 2.2: Der Build- und Flash-Prozess der ESP32-Firmware. Quelle: [Pla+25]

Partitionstabellen werden dabei in einfachen Comma-Separated Values (CSV)-Dateiformat [Sha05] definiert und während des Build-Prozesses in ein Binärformat kompiliert [Cir25].

### 2.2.2.3 Anwendungsabbild

Das Anwendungsabbild ist die Haupt-Firmware, die den Code für die Funktionalität des ESP32 enthält. Nachdem der Bootloader das System initialisiert hat, übergibt er die Kontrolle an das Anwendungsabbild, das dann die beabsichtigten Operationen des Geräts ausführt [Cir25].

### 2.2.3 Xtensa ISA

Die Xtensa-ISA [Cad22] ist eine RISC-basierte Architektur, die von Cadence Tensilica entwickelt wurde und sich durch ihre hohe Konfigurierbarkeit auszeichnet. Sie erlaubt es Entwicklern, den Befehlssatz gezielt an Anforderungen bezüglich Leistung, Speicherbedarf und Energieeffizienz anzupassen, unter anderem durch benutzerdefinierte Instruktionen und Register [Cad22].

Obwohl die Xtensa-ISA den meisten klassischen RISC-Prinzipien folgt, wie etwa einer Load/Store-Architektur und dass Instruktionen in einem „Clock Cycle“ abgearbeitet werden, bietet sie mit der *Code Density Option* eine Besonderheit: Ist diese aktiviert (Standardfall), können viele reguläre 24-Bit-Instruktionen durch kompaktere 16-Bit-Varianten ersetzt werden. Laut offizieller Dokumentation lassen sich in typischem Code etwa die Hälfte aller Befehle in diesem komprimierten Format darstellen, was den Speicherbedarf signifikant reduziert [Cad22].

Die „Windowed Register Option“ führt zusätzliche allgemeine Register ein, wodurch die Gesamtzahl von 16 auf 64 steigt. Um zu vermeiden, dass neue Anweisungen mit größeren Registerkodierungen (von 4 auf 6 Bit pro Register, das in der Anweisung verwendet wird) eingeführt werden müssen, bleibt die Anzahl der sichtbaren Register bei 16. Während Funktionsaufrufen kann dieses Fenster sichtbarer Register um ein Vielfaches von 8 verschoben

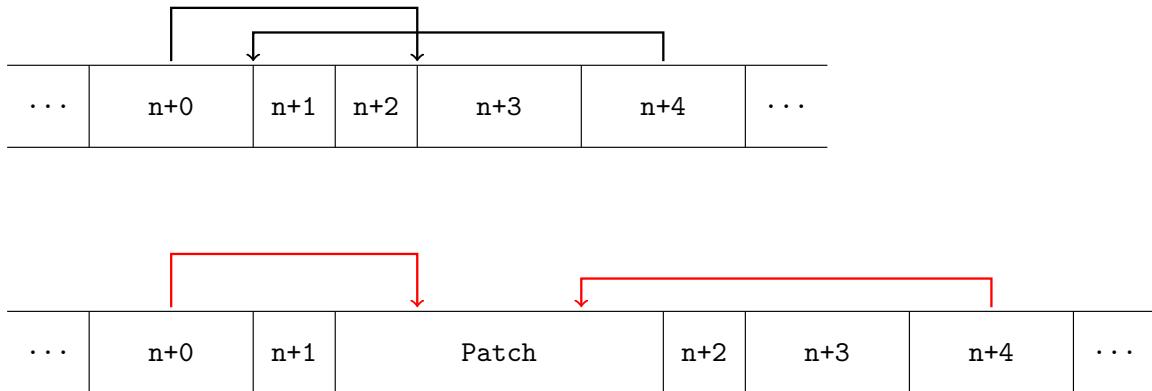

Abbildung 2.3: Das Code Location Problem wird beim Einfügen von Code deutlich: Verschobene Instruktionen führen zu fehlerhaften relativen Sprüngen und Abstürzen. Der Sprung von Instruktion  $n + 0$  zeigt nach dem Patch nicht mehr auf den Beginn von Instruktion  $n + 3$ , sondern auf den neu hinzugefügten Code. Es ist nicht sichergestellt, dass an dieser Stelle eine Instruktion beginnt, was zu einem Absturz führen kann. Quelle: [Pla+25]

werden. Diese Option reduziert die Anzahl der Register, die vor einem Funktionsaufruf auf dem Stack gespeichert werden müssen [Cad22].

Diese komplexen architektonischen Besonderheiten haben direkte Auswirkungen auf die Struktur der Firmware und die nachträgliche Modifikation des Binärcodes. Im folgenden Abschnitt wird daher Rewriting als Konzept vorgestellt. Dieses befasst sich mit den Herausforderungen und Verfahren zur Modifikation von Firmware-Abbildern.

## 2.3 Rewriting

Dieser Abschnitt gibt einen Überblick über ESP32-Firmware-Abbildner und das *Code Location Problem*, das beim Binary Rewriting auftritt, sowie verschiedene Kategorien des Binary Rewritings, d. h. statisches und dynamisches Rewriting.

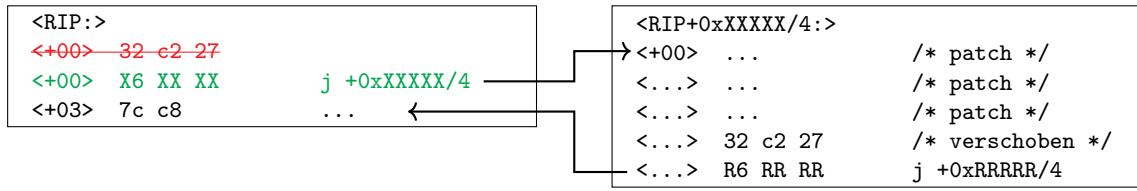

### 2.3.1 Code Location Problem

Das *Code Location Problem* tritt auf, wenn der Binärcode eines Programms verändert wird. Es betrifft insbesondere Systeme, die relative Adressierung verwenden, beispielsweise bei Sprung- oder Verzweigungsanweisungen, deren Zieladressen relativ zu ihrer Speicherposition berechnet werden. Durch das Einfügen neuer oder die Modifikation bestehender Instruktionen verschieben sich die Speicheradressen nachfolgender Instruktionen (siehe Abbildung 2.3). Für Debugger stellt dies ein zentrales Problem dar, da sie auf eine präzise Zuordnung von Quellcodezeilen zu Instruktionsadressen angewiesen sind, um Breakpoints, das Schritthalten und das gezielte Betreten und Verlassen von Subroutinen korrekt zu

realisieren. Nach einer Codeverschiebung verweisen viele Sprünge nicht mehr auf ihre vorgesehenen Ziele, was fehlerhafte Kontrollflüsse, Programmabstürze oder unvorhersehbares Verhalten zur Folge haben kann [TG00].

Die nachträgliche Korrektur solcher Sprungadressen ist insbesondere beim ESP32 anspruchsvoll. Die Architektur unterstützt sowohl 16-Bit- als auch 24-Bit-Instruktionen, wodurch die exakte Position einzelner Befehle schwer vorhersagbar ist. Schon kleine Änderungen können Verschiebungen im gesamten nachfolgenden Code verursachen. Hinzu kommt, dass Code und Daten im Flash-Speicher häufig eng miteinander vermischt sind, was eine lineare Disassemblierung erschwert [Cad22; Esp25a].

### 2.3.2 Binary Rewriting

Unter *Binary Rewriting* versteht man das nachträgliche Verändern von bereits kompiliertem Maschinencode, ohne dass der ursprüngliche Quellcode benötigt wird. Typische Ziele sind das Einfügen von Instrumentierungscode (z. B. für Logging oder Fuzzing), das Anpassen von Programmlogik, das Einfügen von Sicherheitsmechanismen oder das Beheben von Fehlern direkt im Binärcode.

Das Binary Rewriting lässt sich grob in statische und dynamische Methoden unterteilen, die jeweils unterschiedliche Ansätze und Kompromisse aufweisen.

Beim dynamischen Rewriting erfolgen Anpassungen basierend auf dem tatsächlichen Verhalten des Programms zur Laufzeit. Diese Methode eignet sich besser für dynamischen oder selbstmodifizierenden Code, verursacht jedoch einen spürbaren Laufzeit-Overhead, da bei jeder Ausführung zusätzliche Kontroll- und Umleitungslogik berücksichtigt werden muss. Während dieser Mehraufwand bei Desktop- oder Serversystemen oft nur wenige Prozent Leistung kostet und durch hohe Rechenressourcen kompensiert werden kann, wirkt er sich in IoT-Szenarien deutlich stärker aus. Begrenzte Taktfrequenzen und kleiner Arbeitsspeicher machen dynamisches Rewriting für den ESP32 und vergleichbare Mikrocontroller meist unpraktikabel [SBF22].

Beim statischen Rewriting wird der Binärcode verändert, ohne ihn auszuführen, und es wird eine neue, modifizierte Binärdatei erzeugt. Diese Methode erlaubt eine gründliche Analyse und Optimierung vor der Ausführung. Allerdings kann das Neuberechnen von Sprungzielen innerhalb des Codes schwierig sein, insbesondere bei selbstmodifizierendem Code. Änderungen können dabei den ursprünglichen Kontrollfluss stören und neue Fehler einführen. Statische Rewriter arbeiten häufig auf einer sogenannten Intermediate Representation (IR) [Cho13], also einer Zwischendarstellung eines Programms zwischen Quellcode und Maschinencode, beispielsweise auf Assembler-Ebene. Auf dieser Ebene werden Anpassungen vorgenommen, bevor die Binärdatei wieder zusammengesetzt wird [SBF22].

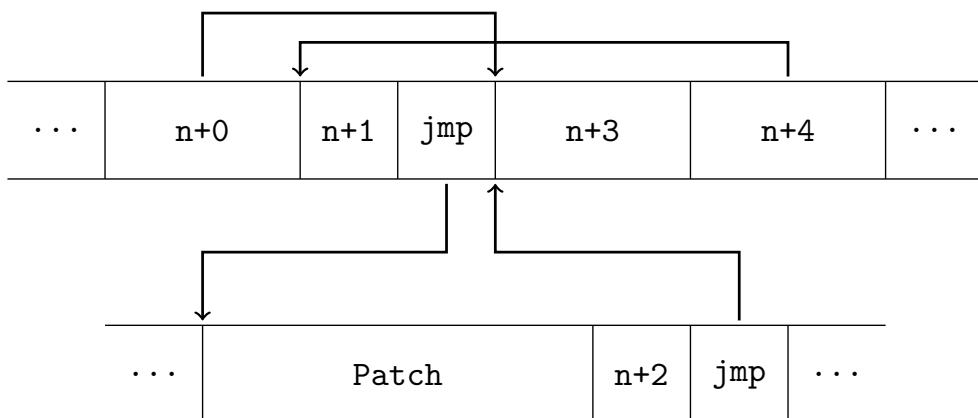

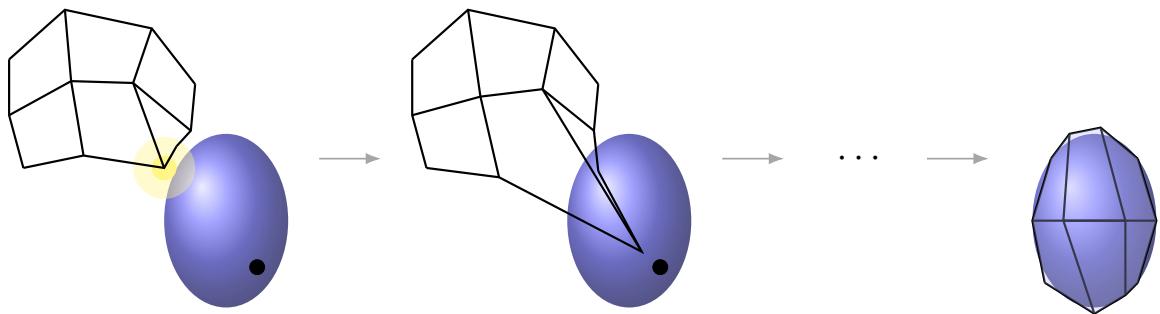

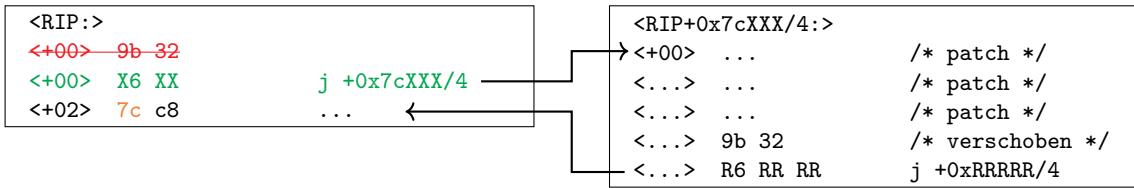

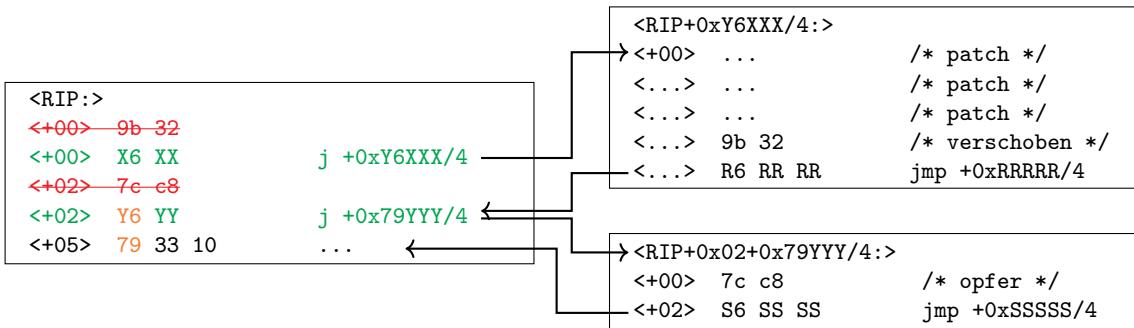

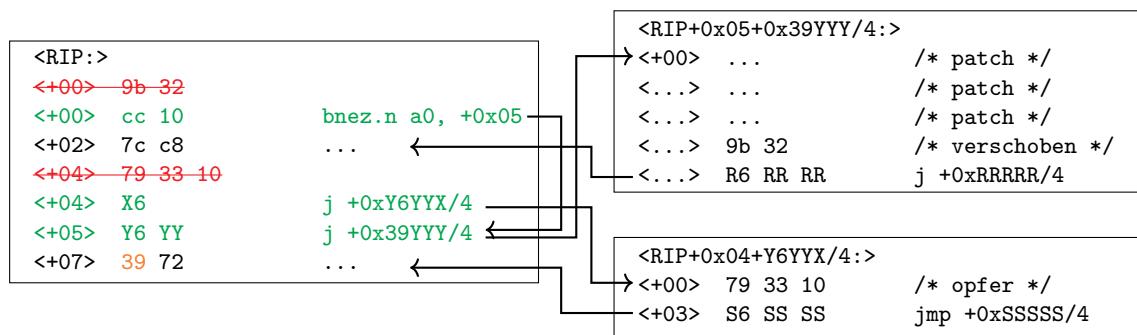

Eine spezielle Technik des statischen Rewritings sind die sogenannten Trampolin-Rewriter. Dabei werden neue Instruktionen in ungenutzten Speicherbereichen abgelegt und der Kontrollfluss durch Sprünge dorthin umgeleitet (siehe Abbildung 2.4). So bleiben die ursprünglichen Instruktionen unverändert, während zusätzliche Funktionalitäten außerhalb

Abbildung 2.4: Trampolin-Rewriter bieten eine Lösung für das *Code Location Problem*. Dabei wird die ursprüngliche Instruktion durch einen Sprungbefehl ersetzt und sowohl die Instruktion als auch der Patch werden in ungenutzten Speicher verschoben. Dadurch bleiben alle nachfolgenden Adressen unverändert. Quelle: [Pla+25]

des Originalcodes integriert werden. Dadurch lässt sich die Kontrollflussintegrität wahren und das *Code Location Problem* effektiv umgehen [DGR20].

Die hier vorgestellten Techniken des Binary Rewritings bilden eine wichtige Grundlage für verschiedene Test- und Sicherheitsverfahren auf Mikrocontroller-Ebene. Im nächsten Abschnitt wird das Fuzzing behandelt, eine weit verbreitete Methode zur automatisierten Erkennung von Softwarefehlern. Dabei werden durch gezielte Eingabegenerierung Schwachstellen in Firmware und Software aufgedeckt.

## 2.4 Fuzzing

In diesem Unterkapitel wird der Begriff des Fuzzings als Testmethode zur Erkennung von Softwarefehlern durch die systematische Generierung und Einspeisung ungewöhnlicher oder ungültiger Eingaben definiert. Es werden zentrale Grundlagen vorgestellt, darunter typische Einsatzszenarien, Verfahren zur Eingabegenerierung und Ansätze des feedbackgesteuerten Fuzzings. Darüber hinaus werden Kriterien wie Codeabdeckung, Effizienz sowie syntaktische und semantische Korrektheit der Eingaben behandelt, um die methodische Einordnung und Messbarkeit des Fuzzings zu verdeutlichen.

### 2.4.1 Definition von Fuzzing

Fuzzing (kurz für *fuzz testing*) ist eine automatisierte Testtechnik zur Identifikation von Fehlern und Sicherheitslücken in Software. Dabei wird die Software wiederholt mit zufälligen oder systematisch generierten Eingaben versorgt, während das Laufzeitverhalten

überwacht wird, um unerwartete Reaktionen wie Abstürze, unbehandelte Ausnahmen oder Speicherlecks zu erkennen und potenzielle Schwachstellen aufzudecken [SGA07; Mhi+25; Lia+18].

Die Idee des Fuzzing entstand 1988 durch Barton P. Miller von der University of Wisconsin–Madison. Während eines Gewitters führten Störungen auf einer langsamen Modem-Leitung dazu, dass durch „Rauschen“ getippte Zeichen zufällig Unix-Utilities abstürzen ließen. Dieses scheinbar banale Phänomen inspirierte Miller dazu, das Konzept systematisch zu untersuchen. Im Rahmen eines Kurses sollten Studierende Programme gezielt mit zufälligen Eingaben testen, wodurch Fuzzing entstand. Bereits in der initialen Studie konnten durch dieses Verfahren 25–33 % der getesteten Programme zum Absturz gebracht werden. Dies war besonders bemerkenswert, da es die Anfälligkeit weit verbreiteter und scheinbar stabiler Software durch einfache zufällige Eingaben aufzeigte [TDM08].

### 2.4.2 Ungültige Eingaben

Eingaben im Rahmen von Fuzzing lassen sich typischerweise in drei Kategorien einteilen:

- *Gültige Eingaben*: Diese entsprechen vollständig der Spezifikation und werden vom Programm ohne Fehlermeldungen verarbeitet.

- *Semi-valide Eingaben*: Sie sind ein Sonderfall der gültigen Eingaben und erfüllen gerade noch die Spezifikation, um vom Parser akzeptiert zu werden, enthalten jedoch gezielt Variationen oder Extremwerte, um seltene Fehlerzustände zu provozieren.

- *Ungültige Eingaben*: Diese verletzen die grundlegende Struktur der erwarteten Daten und werden in der Regel unmittelbar vom Programm verworfen. Sie treten insbesondere bei stark strukturierten Formaten wie XML oder bei Netzwerkprotokollen auf und liefern häufig keine verwertbaren Rückmeldungen für die Laufzeitanalyse.

Da eine vollständige Abdeckung aller möglichen Eingaben praktisch unmöglich ist, liegt der Schwerpunkt neben den gültigen Eingaben vorwiegend auf den semi-validen Randfällen. Diese Strategie erhöht die Wahrscheinlichkeit, seltene oder schwer reproduzierbare Fehlerzustände zu identifizieren [Bha22].

### 2.4.3 Fuzzing-Szenarien

Fuzzing-Methoden unterscheiden sich vor allem durch den Grad des Wissens über das zu testende System. Üblich ist die Einteilung in Whitebox-, Blackbox- und Greybox-Fuzzing.

- **Whitebox-Fuzzing**: Der Fuzzer hat vollständigen Zugriff auf den Quellcode und die interne Programmlogik. Mittels statischer und dynamischer Analyse werden gezielt Eingaben generiert, um schwer erreichbare Codepfade abzudecken. Oft wird dynamische symbolische Ausführung (engl. „concolic execution“) eingesetzt. Während der Programmausführung werden symbolische Bedingungen gesammelt und gezielt negiert. Mithilfe eines Constraint-Solvers werden anschließend neue Eingaben

berechnet, die unerforschte Pfade ansteuern. Damit können theoretisch Testfälle generiert werden, die alle möglichen Ausführungspfade abdecken. In der Praxis ist dies jedoch oft nicht vollständig umsetzbar, da reale Software sehr viele potenzielle Pfade enthält und die Lösung der symbolischen Bedingungen komplex sein kann. Dennoch ermöglicht Whitebox-Fuzzing eine systematische und effiziente Fehlerentdeckung [GLM08; Lia+18].

- **Blackbox-Fuzzing:** Das Testen erfolgt ohne Kenntnis des Quellcodes. Die Eingaben werden zufällig oder heuristisch erzeugt, häufig aus bestehenden Beispielen, die durch Mutationen wie Bitflips, Byte-Kopien oder Löschungen verändert werden. Moderne Ansätze nutzen zusätzlich Wissen über das Grammatik- oder EingabefORMAT, um teilweise gültige Eingaben zu erzeugen. Blackbox-Fuzzing ist einfach implementierbar und breit anwendbar, erreicht jedoch aufgrund fehlender Rückmeldungen zur Programmausführung meist nur eine geringe Codeabdeckung [Lia+18].

- **Greybox-Fuzzing:** Dieser Ansatz liegt zwischen White- und Blackbox-Fuzzing. Der Fuzzer erhält begrenzte Einblicke in das Programm, beispielsweise durch leichte Instrumentierung oder Feedback zur Codeabdeckung. Komplexe Techniken wie symbolische Ausführung werden nicht verwendet. Eingaben, die neue Pfade erreichen, werden gezielt wiederverwendet und als Basis für Mutationen genutzt. Dadurch steigt die Testeffektivität im Vergleich zu reinem Blackbox-Fuzzing [Lia+18; Zel+24].

In dieser Dissertation wird, soweit nicht anders angegeben, stets ein Greybox-Fuzzing-Szenario zugrunde gelegt.

### 2.4.4 Eingabegenerierung

Die Generierung von Testeingaben ist ein zentraler Bestandteil des Fuzzings. Eingaben können zufällig, durch Mutationen bestehender Beispiele oder systematisch auf Basis formaler Regeln erzeugt werden. Entsprechend werden Fuzzer häufig nach ihrer Methode der Eingabegenerierung unterschieden:

- **Dumb Fuzzer:** Diese Fuzzer erzeugen Eingaben vollständig zufällig, ohne Kenntnis des zugrunde liegenden Formats oder der erwarteten Datenstruktur. Sie arbeiten meist auf Byte- oder String-Ebene und führen einfache Manipulationen durch, wie das Einfügen, Löschen oder Verändern von Zeichen. Sie nutzen allenfalls grundlegende Heuristiken, erkennen aber keine komplexen Zusammenhänge. Aufgrund der vielen ungültigen Eingaben sind sie in komplexen Systemen nur begrenzt effektiv und eignen sich eher für einfache oder robuste Parser [LZZ18].

- **Mutationsbasierte Fuzzer:** Sie starten mit gültigen Eingaben (Seeds) und verändern diese durch zufällige oder heuristische Operationen wie Ersetzen, Einfügen oder Löschen von Bytes. Durch die Verwendung funktionierender Ausgangsdaten wird eine höhere Wahrscheinlichkeit erreicht, dass die Eingaben vom Programm verarbeitet werden. Diese Methode ist besonders effektiv, wenn hochwertige Seed-Dateien verfügbar sind [LZZ18].

Abbildung 2.5: Schematische Darstellung von feedbackgesteuertem Fuzzing

- **Generationsbasierte Fuzzer:** Hier werden Eingaben vollständig neu erzeugt, basierend auf einer formalen Beschreibung des Eingabeformats, wie Datenmodellen, Protokollspezifikationen, Zustandsautomaten oder Ablaufdiagrammen. Diese Methode erzeugt syntaktisch gültige und semantisch anspruchsvolle Testfälle, die sich besonders für strukturierte Eingaben wie Netzwerkprotokolle, APIs oder komplexe Dateiformate eignen [LZZ18].

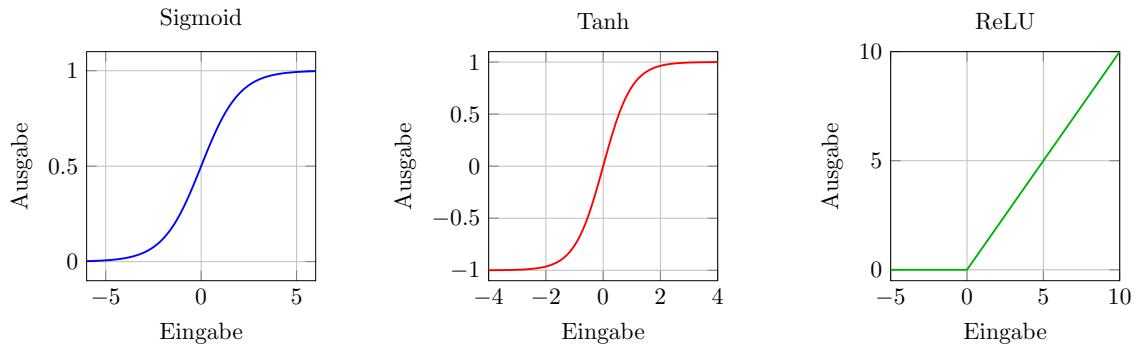

- **Grammatikbasierte Fuzzer:** Eine spezielle Untergruppe der generationsbasierten Fuzzer. Sie verwenden kontextfreie Grammatiken, um komplexe Eingaben zu erzeugen. Diese Technik eignet sich besonders für textbasierte Formate mit klar definierter Syntax, strukturierte Daten wie JSON oder XML mit eindeutiger Grammatik (siehe Abschnitt 2.5) [SS19].

#### 2.4.5 Feedbackgesteuertes Fuzzing

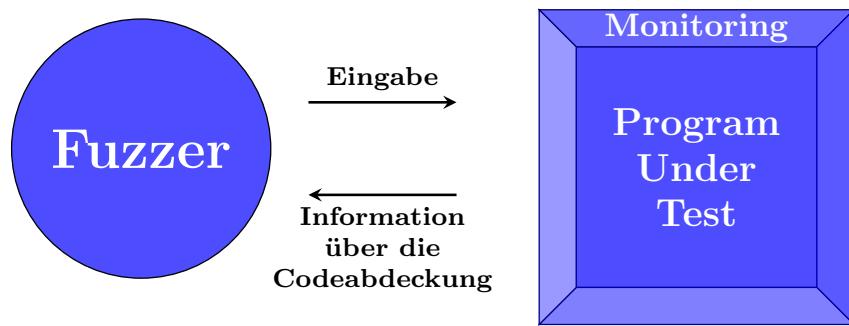

Die Effektivität eines Fuzzers lässt sich deutlich erhöhen, wenn Rückmeldungen aus der Programmausführung zur gezielten Steuerung der Eingabegenerierung genutzt werden. Beim feedbackgesteuerten Fuzzing (engl. *Feedback-driven Fuzzing*, auch *Coverage-guided Fuzzing* genannt) überwacht der Fuzzer während der Ausführung, welche Codebereiche durch eine bestimmte Eingabe erreicht werden. Mithilfe dieser Informationen werden anschließend neue Eingaben so verändert, dass bisher unerreichte oder selten ausgeführte Pfade gezielt abgedeckt werden. Eine schematische Darstellung ist in Abbildung 2.5 zu finden. Vor allem mutationsbasierte Fuzzer profitieren stark von diesem Ansatz, da das Feedback es ihnen ermöglicht, Eingaben adaptiv zu optimieren und die Codeabdeckung systematisch zu steigern [Zal19].

#### 2.4.6 Codeabdeckung und Messbarkeit von Fuzzing

Die einfachste Möglichkeit, die Wirksamkeit eines Fuzzers zu bewerten, wäre, die Anzahl der gefundenen Abstürze oder Schwachstellen innerhalb eines begrenzten Zeitraums

(z. B. 24 Stunden) zu messen. Allerdings ist oft unklar, ob das getestete Programm überhaupt Schwachstellen enthält und ob diese innerhalb des vorgegebenen Zeitraums gefunden werden können. Daher wird die Wirksamkeit von Fuzzing häufig anhand der Codeabdeckung (engl. *Code Coverage*) beurteilt. Diese gibt an, wie tief ein Fuzzer in die Programmlogik vordringt, ist aber kein direkter Indikator für die Anzahl gefundener Schwachstellen [Wan+20b].

Ein gängiges Maß für die Testabdeckung ist die sogenannte Zeilenabdeckung (engl. *Line Coverage*). Sie gibt an, welcher Anteil der Quellcodezeilen während eines Fuzzing-Laufs mindestens einmal ausgeführt wurde. Eine vollständige Zeilenabdeckung garantiert jedoch nicht, dass die zugrunde liegende Logik vollständig getestet wurde, denn unterschiedliche Eingaben innerhalb einer Zeile können zu abweichendem Verhalten führen. Eine hohe Zeilenabdeckung signalisiert hingegen, dass ein Großteil des Codes aktiviert und potenziell auf Fehler überprüft wurde. Beim feedbackgesteuerten, mutationsbasierten Fuzzing dient die Zeilenabdeckung als Leitwert für die Auswahl von Seeds. Eingaben, die eine hohe Zeilenabdeckung erzeugen, werden bevorzugt mutiert, um neue Testfälle zu erzeugen. Auf diese Weise lassen sich auch tief im Programm liegende Funktionen systematisch testen [WHJ15; BSM22].

Die Zweigabdeckung (engl. *Branch Coverage*) betrachtet zusätzlich alle logischen Verzweigungen, etwa beide Pfade eines `if`-Statements oder sämtliche `switch`-Fälle. Somit liefert sie ein detaillierteres Bild des Programmflusses und erleichtert die gezielte Optimierung von Testeingaben. Nicht abgedeckte Verzweigungen deuten auf unzureichende Eingaben hin [BSM22].

Da weder die Zeilen- noch die Zweigabdeckung direkt mit der Anzahl entdeckter Schwachstellen korreliert, werden zur objektiven Bewertung oft synthetische Bugs (engl. *Synthetic Bugs*) eingesetzt. Dabei werden bekannte Fehler gezielt in das PUT eingebaut, sodass überprüft werden kann, welche davon ein Fuzzer tatsächlich findet. Dieses Verfahren ermöglicht einen vergleichbaren und reproduzierbaren Test der Effektivität verschiedener Fuzzing-Strategien [Bun+21].

Der folgende Abschnitt befasst sich deshalb mit dem Thema „Effizientes Fuzzing“ und beleuchtet diese Aspekte näher. Dabei werden auch wichtige Kennzahlen zur Bewertung vorgestellt.

### 2.4.7 Effizientes Fuzzing

Im Kontext des Fuzzings bezeichnet Effizienz das Verhältnis zwischen eingesetztem Ressourcenaufwand, beispielsweise Zeit, Rechenleistung oder Energie, und dem erzielten Testfortschritt. Im Unterschied dazu bezeichnet Effektivität die Fähigkeit, tatsächlich sicherheitsrelevante Schwachstellen oder Bugs aufzudecken [GGG22]. Ein Fuzzer kann also sehr effizient arbeiten (z. B. durch hohe Eingabeverarbeitungsraten), ohne notwendigerweise effektiv zu sein, wenn er dabei keine relevanten Fehler findet.

Welche Kennzahl zur Bewertung der Effizienz herangezogen wird, hängt davon ab, welcher Aspekt des Testfortschritts im jeweiligen Szenario erreichbar und sinnvoll messbar ist:

- **Fehlerentdeckungsrate:** Ist der Quellcode zugänglich, lassen sich gezielt synthetische Bugs einbauen und deren Anzahl exakt bestimmen. In diesem Fall kann die Effizienz unmittelbar als Geschwindigkeit der Fehlerentdeckung definiert werden, da gemessen werden kann, wie viele dieser bekannten Schwachstellen pro Zeiteinheit aufgedeckt werden. Je schneller diese Bugs gefunden werden, desto direkter werden die eingesetzten Ressourcen in sicherheitsrelevanten Fortschritt umgesetzt [GGG22].

- **Codeabdeckung:** Ist der Code nicht veränderbar oder die Anzahl der Bugs unbekannt, bleibt die Codeabdeckung die praktikabelste Messgröße. Vor allem Greybox-Fuzzer wie AFL instrumentieren den Binärkode so, dass die Abdeckung die tatsächlich durchlaufenden Pfade widerspiegelt. Auch wenn dies durch Compiler-Optimierungen nicht exakt den Quellcodezeilen entspricht, erlaubt es dennoch einen direkten Vergleich verschiedener Ansätze hinsichtlich der erreichten Programmfpad-Abdeckung. Eine hohe Abdeckung weist darauf hin, dass mit den gleichen Ressourcen ein größerer Programmteil getestet wurde, was aus Effizienzsicht vorteilhaft ist [LZZ18; Zal19].

- **Verarbeitungsrate:** Selbst ohne vollständigen Fuzzer kann die Effizienz einzelner Komponenten anhand ihrer Eingabeverarbeitungsrate bewertet werden. Besonders auf ressourcenbeschränkten IoT-Geräten ist die Zahl der pro Sekunde verarbeiteten Anfragen begrenzt, während virtuelle Testumgebungen höhere Raten erlauben. Je mehr Eingaben in derselben Zeit verarbeitet werden, desto effizienter werden die verfügbaren Ressourcen genutzt [Bör+20].

- **Qualität der Eingaben:** Nicht nur die Menge, sondern auch die Vielfalt und Relevanz der generierten Eingaben beeinflussen die Effizienz. Ungültige Eingaben aktivieren oft nur triviale Programmteile, wodurch die Testtiefe sinkt. Werden hingegen gezielt Eingaben generiert, die möglichst viele verschiedene Codepfade auslösen, steigt die Wahrscheinlichkeit, kritische Teile des Programms mit begrenztem Ressourceneinsatz zu testen [Mhi+25].

Zusammenfassend lässt sich die Effizienz beim Fuzzing also als das Verhältnis von eingesetzten Ressourcen zu erzieltem Testfortschritt verstehen. Je nach Kontext kann der Fortschritt über Fehlerfunde, Codeabdeckung, Eingabedurchsatz oder Eingabequalität gemessen werden. Diese unterschiedlichen Perspektiven sind komplementär und verdeutlichen, dass Effizienz stets relativ zu den Testzielen interpretiert werden muss.

Um den Erfolg eines Fuzzers jedoch noch gezielter zu verbessern, ist es wichtig, neben der Menge auch die Qualität der generierten Eingaben zu betrachten. Dabei spielen insbesondere die syntaktische und semantische Korrektheit der Testeingaben eine entscheidende Rolle. Auf diesen Aspekt wird im Folgenden näher eingegangen.

#### 2.4.8 Syntaktische und semantische Korrektheit

Eingaben, Datenpakete oder Dokumente können hinsichtlich ihrer *syntaktischen* und *semantischen* Korrektheit unterschieden werden [FS00; Ais25]:

- **Syntaktische Korrektheit:** Die Eingabe erfüllt die formalen Strukturregeln eines Datenformats oder Protokolls. Bei XML bedeutet dies korrekt geschlossene Tags, gültige Attribute und konsistente Verschachtelungen. Bei Netzwerkpaketen müssen alle erforderlichen Headerfelder vorhanden sein, die Feldlängen müssen stimmen und die Checksummen müssen korrekt sein. Syntaktisch korrekte Eingaben werden vom Parser akzeptiert und können vom System verarbeitet werden.

- **Semantische Korrektheit:** Die Eingabe ist inhaltlich konsistent und entspricht den logischen Erwartungen des Systems. Ein XML-Dokument ist semantisch korrekt, wenn die Feldinhalte den erwarteten Datentypen und zulässigen Wertebereichen entsprechen. Ein Netzwerkpaket ist semantisch korrekt, wenn Sequenznummern, Befehle oder Parameter konsistent mit dem Protokoll sind und sinnvoll interpretiert werden können.

Für das Fuzzing bildet die syntaktische Korrektheit die notwendige Grundlage, da nur korrekt geparse Eingaben verarbeitet werden können. Darüber hinaus steigert semantische Korrektheit die Wahrscheinlichkeit, seltene Fehlerzustände und Sicherheitslücken zu identifizieren, insbesondere bei stark strukturierten Formaten wie XML und komplexen Netzwerkprotokollen [Bra+08; Vis+11].

Um diese Aspekte der Korrektheit bei der Eingabegenerierung gezielt zu berücksichtigen, wird im folgenden Abschnitt das Konzept des grammatischen Fuzzings erläutert. Es nutzt formale Grammatiken, um strukturierte und gültige Testfälle zu erzeugen.

## 2.5 Grammatiken für Fuzzing

Grammatikbasiertes Fuzzing ist eine spezialisierte Form des generationsbasierten Fuzzings. Es nutzt formale Grammatiken zur präzisen Beschreibung syntaktischer Regeln und ermöglicht so die Erzeugung strukturell gültiger Eingaben. Dies ist besonders bei komplexen oder stark regulierten Formaten von Vorteil [GLM08; Zel+24].

### 2.5.1 Aufbau der Grammatik

Eine Grammatik beschreibt eine formale Struktur, die definiert, wie gültige Zeichenketten einer Sprache gebildet werden können. Sie besteht im Wesentlichen aus einer endlichen Menge von Terminalsymbolen, die die konkreten Zeichen der Sprache darstellen, einer Menge von Variablen (auch Nicht-Terminalsymbole genannt), die als Platzhalter für syntaktische Kategorien dienen, sowie einer Menge von Produktionsregeln, die angeben, wie Variablen durch andere Variablen oder Terminals ersetzt werden können. Eine dieser Variablen ist als *Startsymbol* ausgezeichnet und dient als Ausgangspunkt für die Erzeugung von Zeichenketten [HMU11].

### 2.5.2 Formale Beschreibung von Grammatiken

Formal wird eine Grammatik  $G$  als ein Tupel  $G = (V, T, P, S)$  definiert, bestehend aus:

- $V$ : der endlichen Menge der *Variablen* (Nicht-Terminalsymbole), die Platzhalter für syntaktische Strukturen darstellen,

- $T$ : der endlichen Menge der *Terminalsymbole*, die die konkreten Zeichen der Sprache bilden,

- $P$ : der endlichen Menge der *Produktionsregeln*, die definieren, wie Variablen durch Terminals oder andere Variablen ersetzt werden,

- $S \in V$ : dem *Startsymbol*, von dem aus die Erzeugung gültiger Zeichenketten beginnt.

Eine Produktionsregel hat die Form

$$A \rightarrow \alpha$$

wobei  $A \in V$  eine Variable und  $\alpha \in (V \cup T)^*$  eine Zeichenkette aus Terminalen und/oder Variablen ist. Durch wiederholte Anwendung dieser Regeln lassen sich syntaktisch gültige Zeichenketten konstruieren [HMU11].

### 2.5.3 Kontextfreie Grammatiken

Eine *kontextfreie Grammatik* ist eine spezielle Klasse formaler Grammatiken, bei der jede Produktionsregel genau eine Variable auf der linken Seite besitzt:

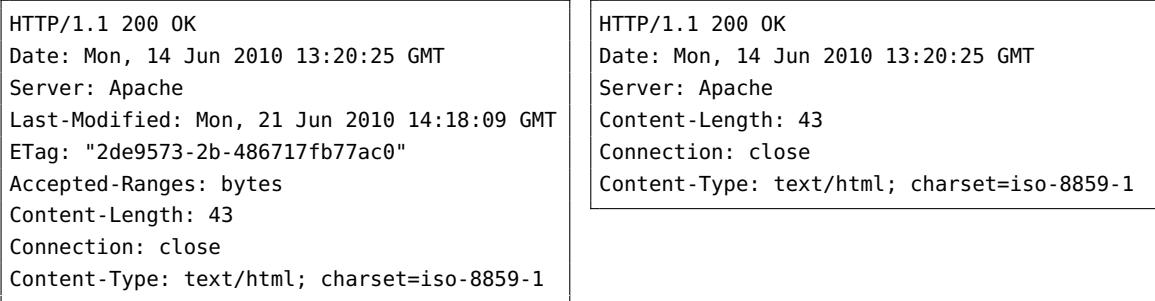

$$A \rightarrow \alpha \quad \text{mit} \quad A \in V, \alpha \in (V \cup T)^*$$