# **Efficient and Correct Persistent Memory File Systems**

Zur Erlangung des akademischen Grades eines

Doktors der Ingenieurwissenschaften

von der KIT-Fakultät für Informatik

des Karlsruher Instituts für Technologie (KIT)

genehmigte

Dissertation

von

Lukas Werling

---

Tag der mündlichen Prüfung: 12.12.2025

Erster Referent: Prof. Dr. Frank Bellosa

Zweiter Referent: Prof. Dr. Christian Dietrich

This document is licensed under a Creative Commons

Attribution-ShareAlike 4.0 International License (CC BY-SA 4.0):

<https://creativecommons.org/licenses/by-sa/4.0/deed.en>

In memory of my grandma

Emma Westermann

1929 – 2026

# Abstract

Persistent memory (PM) is a novel storage technology that enables byte-granular direct access from the CPU with low latency. Compared to traditional asynchronous block storage, this access paradigm allows file systems to offer stronger persistence guarantees at lower latency. However, it also introduces new challenges for performance, efficiency, and correctness. PM's small atomic write size requires careful use of PM primitives to prevent data loss in the event of a crash. Overloading PM with parallel accesses results in expensive CPU stalls.

This thesis investigates the efficiency and correctness of PM file systems. First, we introduce efficiency metrics that quantify CPU time and energy cost per unit of storage access. We show that many existing PM file systems perform poorly under parallel load. To address PM overload, we design mitigation mechanisms that integrate with existing file systems and a monitoring technique to attribute direct-access PM traffic to processes.

Second, to improve correctness, we present **Suvi**, an approach to black-box crash consistency testing for PM file systems. **Suvi** traces a file system's PM and NVMe SSD accesses in a virtual machine and replays the trace with an accurate simulation of x86 store-order semantics. **Suvi** generates crash images using two heuristics to avoid combinatorial explosion, and then automatically analyzes the crash images to detect atomicity bugs.

Together, these contributions provide measurement tools, mitigation strategies, and testing infrastructure to make PM file systems more efficient and more reliable.

# Acknowledgements

I would like to express my gratitude to Prof. Dr. Frank Bellosa for his continuous support and helpful advice. He granted me the freedom to pursue my ideas and provided valuable networking opportunities at conferences.

I am grateful to Prof. Dr. Christian Dietrich for kindly agreeing to act as the secondary reviewer and for his constructive comments whenever I presented my work at conferences and workshops.

Many thanks to my colleagues Daniel Habicht, Peter Maucher, and Thorsten Gröninger for their thoughtful feedback on both the thesis and its presentation. Their suggestions helped me improve the clarity and fix errors in technical descriptions. I also thank Johannes Bechberger for his careful proofreading.

Finally, I owe special thanks to Christian Schwarz. His master's thesis provided the initial motivation to pursue PM file system efficiency and correctness. Christian also provided regular insight into storage challenges from an industry perspective.

# Contents

|                                                                |           |

|----------------------------------------------------------------|-----------|

| <b>Abstract .....</b>                                          | <b>5</b>  |

| <b>Acknowledgements .....</b>                                  | <b>7</b>  |

| <b>1 Introduction .....</b>                                    | <b>13</b> |

| 1.1 Motivation for Persistent Memory .....                     | 13        |

| 1.2 Challenges for PM File Systems .....                       | 14        |

| 1.3 Measuring and Improving PM Efficiency .....                | 15        |

| 1.4 PM File System Crash Consistency .....                     | 16        |

| 1.5 Contributions .....                                        | 16        |

| 1.6 Student Theses and Publications .....                      | 17        |

| 1.7 Structure .....                                            | 19        |

| <b>2 Background – Persistent Memory and File Systems .....</b> | <b>21</b> |

| 2.1 Optane Persistent Memory .....                             | 21        |

| 2.1.1 Regions .....                                            | 22        |

| 2.1.2 Namespaces .....                                         | 23        |

| 2.1.3 Performance Counters .....                               | 23        |

| 2.2 Linux File System Support for PM .....                     | 25        |

| 2.2.1 Accessing PM from the Kernel .....                       | 25        |

| 2.2.2 Block Translation Table (BTT) .....                      | 25        |

| 2.2.3 Ext4 and XFS without BTT .....                           | 26        |

| 2.2.4 DAX Support .....                                        | 27        |

| 2.3 PM File Systems .....                                      | 27        |

| 2.3.1 PMFS, WineFS, and OdinFS .....                           | 28        |

| 2.3.2 Aerie .....                                              | 29        |

| 2.3.3 NOVA, NOVA-Fortis, and Ziggurat .....                    | 30        |

| 2.3.4 Strata and Assise .....                                  | 31        |

| 2.3.5 SPMFS .....                                              | 31        |

| 2.3.6 Trio .....                                               | 32        |

| 2.3.7 P2CACHE .....                                            | 33        |

| 2.3.8 SlotFS .....                                             | 33        |

| 2.4 Crash Consistency .....                                    | 34        |

| 2.4.1 Crash Consistency for Persistent Memory .....            | 35        |

| 2.4.2 Crash Consistency for NVMe .....                         | 37        |

| <b>3 Motivation – Designing Data Structures for PM .....</b>   | <b>41</b> |

| 3.1 PM Ring Buffer Overview .....                              | 41        |

|          |                                                 |           |

|----------|-------------------------------------------------|-----------|

| 3.1.1    | PM Organization and Runtime Data .....          | 42        |

| 3.1.2    | Recovery .....                                  | 43        |

| 3.1.3    | Write Process .....                             | 43        |

| 3.2      | Implementation and Evaluation Setup .....       | 46        |

| 3.3      | Memory Access Instructions .....                | 47        |

| 3.4      | Parallel Accesses .....                         | 49        |

| 3.4.1    | Non-Interleaved Optane PM .....                 | 49        |

| 3.5      | Alignment and Access Size .....                 | 50        |

| 3.6      | NUMA .....                                      | 51        |

| 3.7      | Discussion .....                                | 52        |

| 3.8      | PM Ring Buffer for File Systems .....           | 53        |

| 3.8.1    | ZIL-PMEM: PM Write Cache for ZFS .....          | 53        |

| 3.8.2    | DPWC: Write Cache for Block Devices .....       | 53        |

| <b>4</b> | <b>PM File System Efficiency .....</b>          | <b>55</b> |

| 4.1      | Metrics for File System Efficiency .....        | 56        |

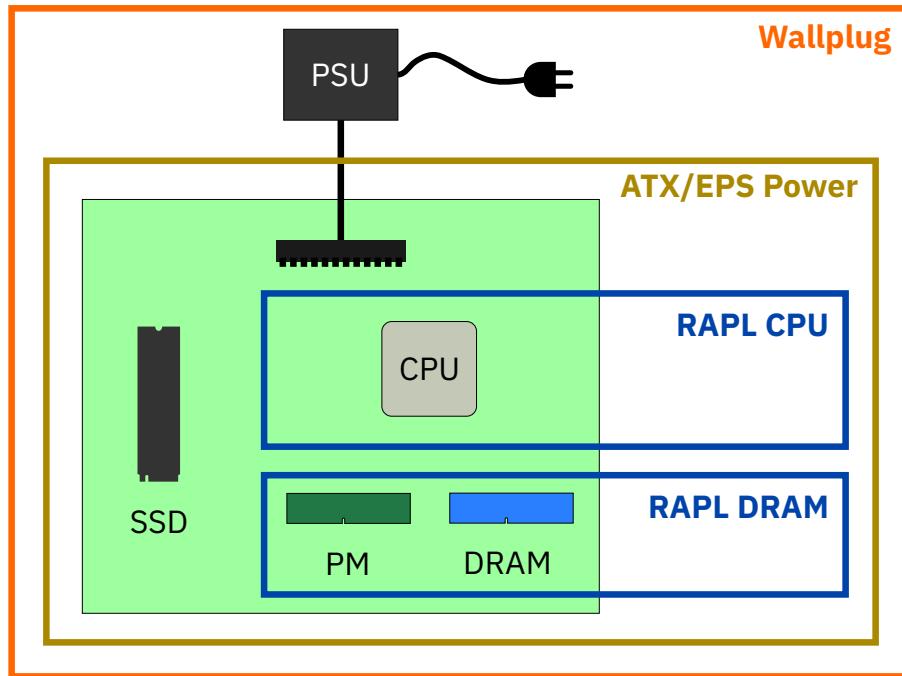

| 4.1.1    | Energy Efficiency .....                         | 57        |

| 4.1.2    | CPU Efficiency .....                            | 58        |

| 4.2      | Analyzing File System Efficiency .....          | 59        |

| 4.2.1    | Measurement Setup .....                         | 59        |

| 4.2.2    | File System Selection .....                     | 61        |

| 4.2.3    | FIO Benchmark Setup .....                       | 62        |

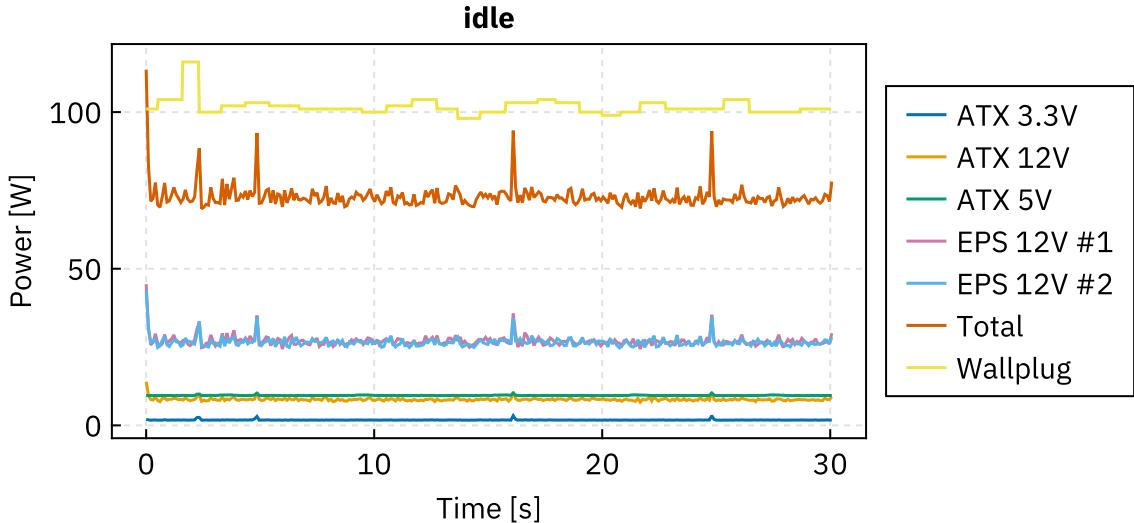

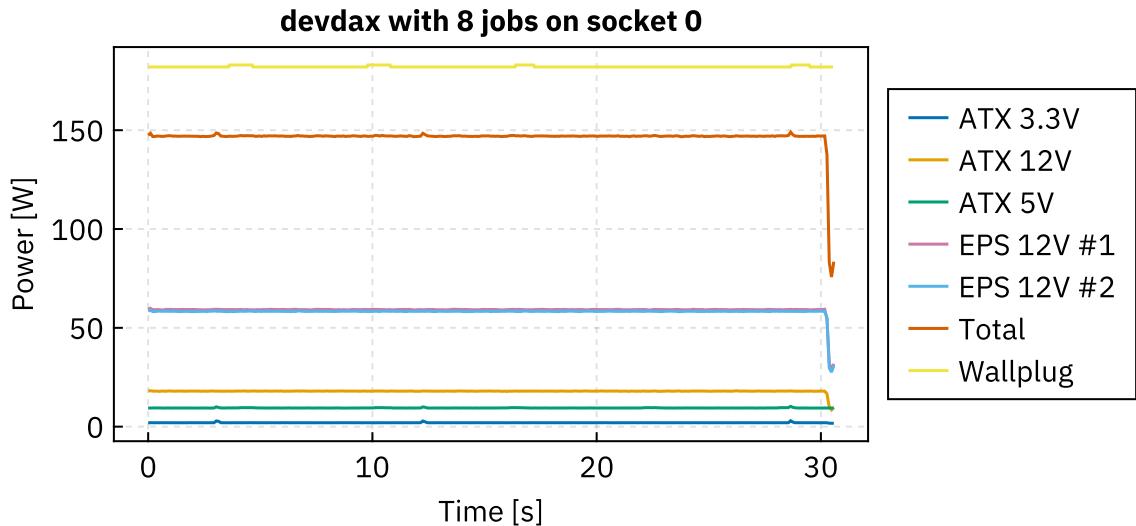

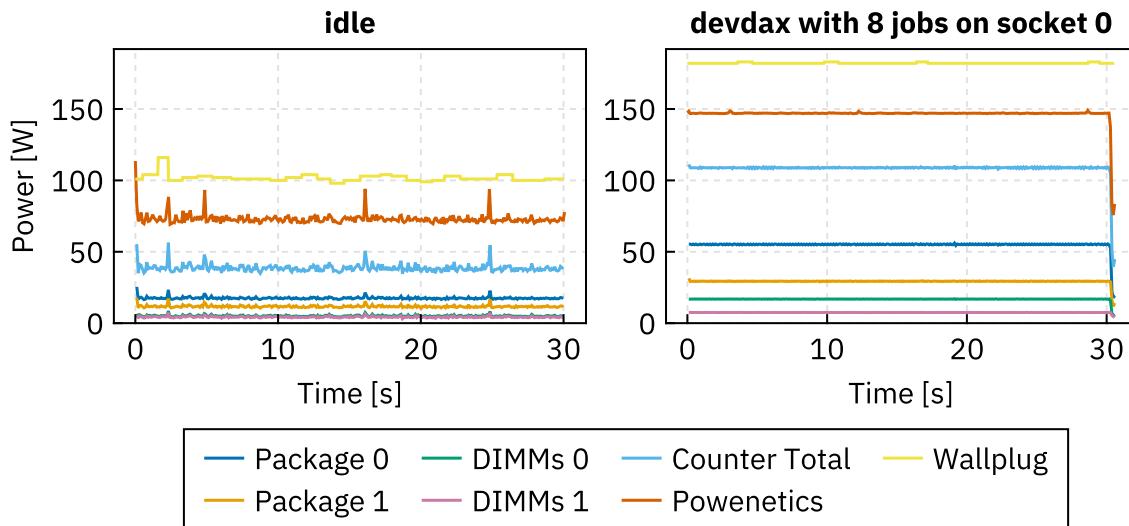

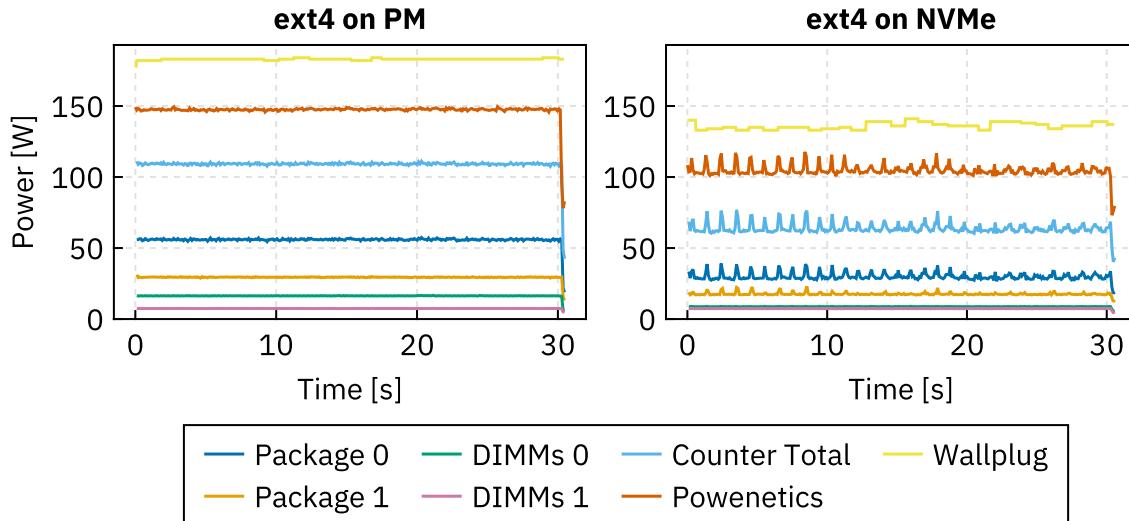

| 4.2.4    | Power Measurements .....                        | 63        |

| 4.3      | Evaluation .....                                | 66        |

| 4.3.1    | ext4 and NOVA .....                             | 66        |

| 4.3.2    | OdinFS, ZIL-PMEM, and DPWC .....                | 69        |

| 4.4      | Discussion .....                                | 72        |

| <b>5</b> | <b>PM File System Overload Mitigation .....</b> | <b>73</b> |

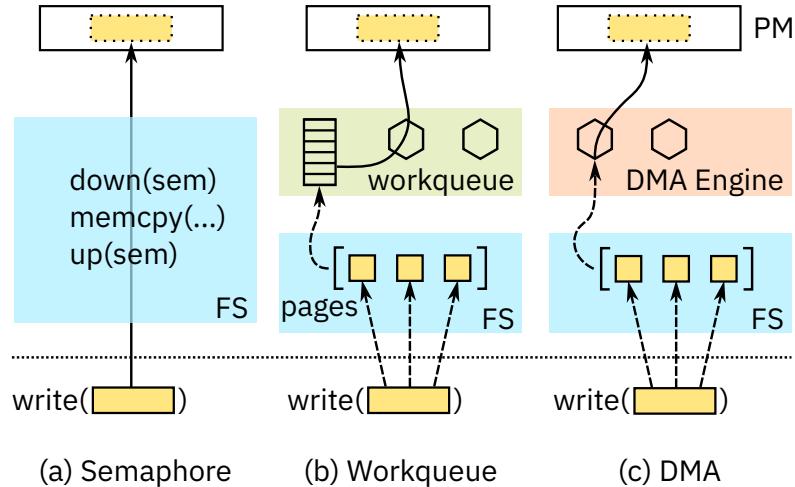

| 5.1      | Design and Implementation .....                 | 73        |

| 5.1.1    | Semaphore .....                                 | 74        |

| 5.1.2    | Workqueue .....                                 | 75        |

| 5.1.3    | DMA .....                                       | 75        |

| 5.2      | File System Integration .....                   | 76        |

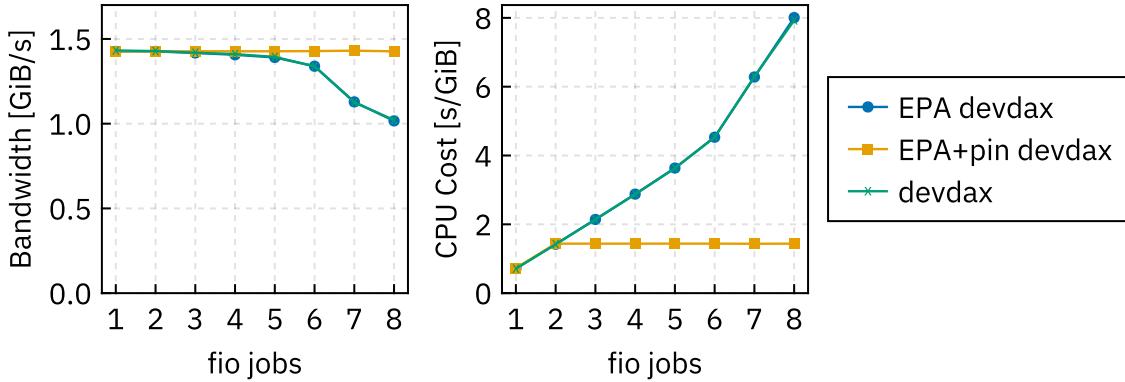

| 5.3      | Evaluation .....                                | 76        |

| 5.3.1    | Semaphore .....                                 | 76        |

| 5.3.2    | Workqueue .....                                 | 77        |

| 5.3.3    | DMA .....                                       | 80        |

| 5.4      | Discussion .....                                | 80        |

| <b>6</b> | <b>Userspace PM Access Accounting .....</b>     | <b>81</b> |

| 6.1      | Requirements .....                              | 82        |

| 6.2      | Accounting with Performance Counters .....      | 82        |

| 6.2.1    | Read Accesses .....                             | 82        |

| 6.2.2    | Write Accesses .....                            | 83        |

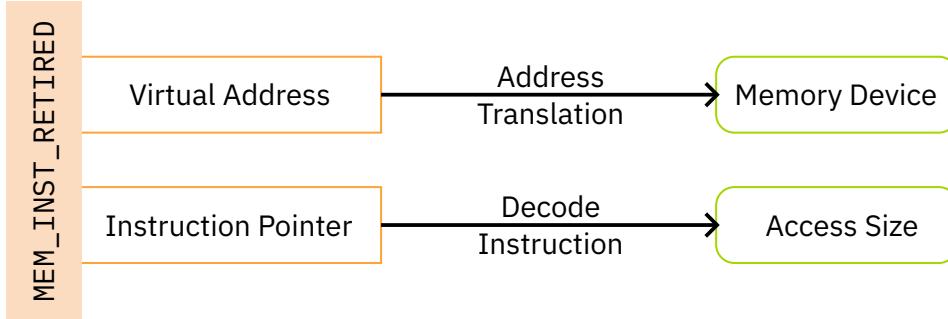

| 6.3      | Approach: Sampling Memory Instructions .....    | 83        |

| 6.3.1    | Processor Event Based Sampling (PEBS) .....     | 84        |

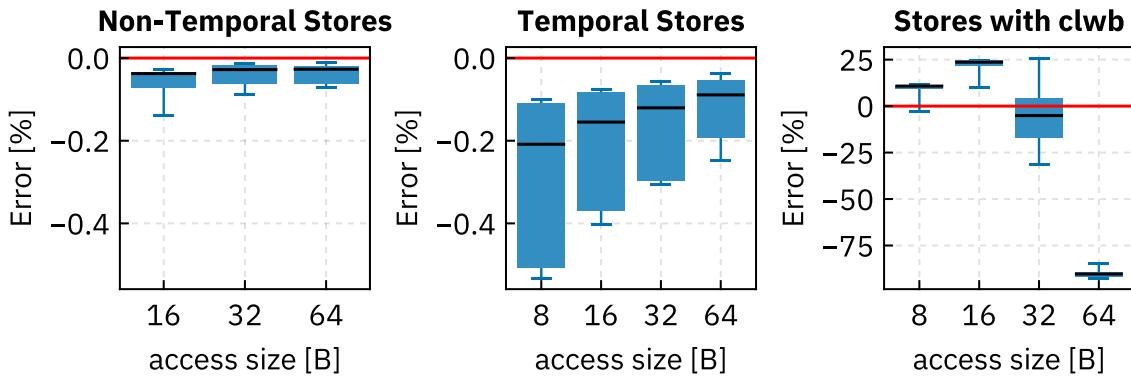

| 6.3.2    | Bandwidth Estimation .....                      | 84        |

|          |                                                                  |            |

|----------|------------------------------------------------------------------|------------|

| 6.3.3    | Limitations .....                                                | 85         |

| 6.4      | Implementation .....                                             | 86         |

| 6.5      | Scheduling .....                                                 | 87         |

| 6.6      | Evaluation .....                                                 | 88         |

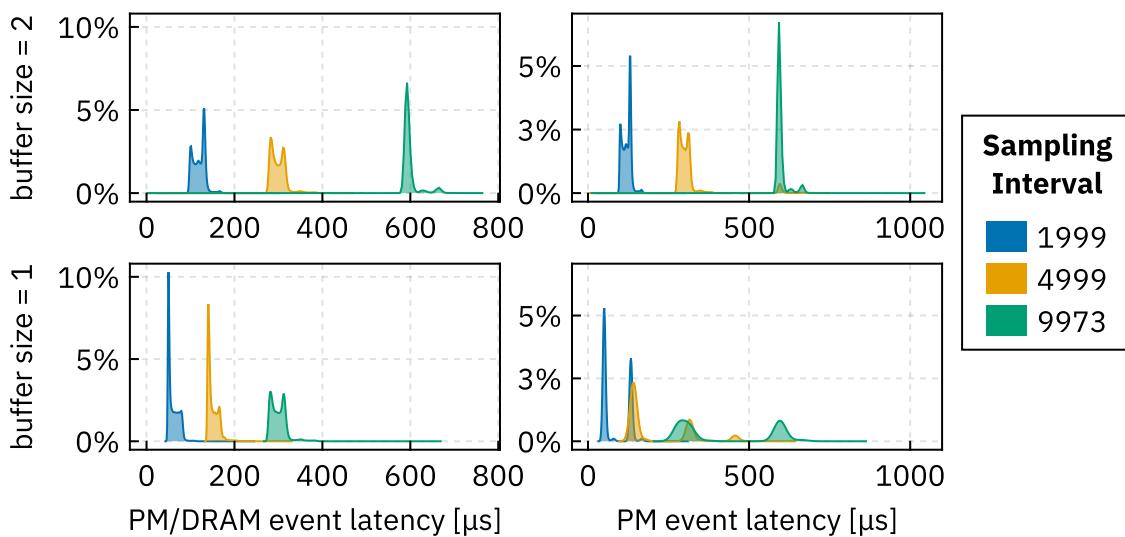

| 6.6.1    | Accuracy .....                                                   | 88         |

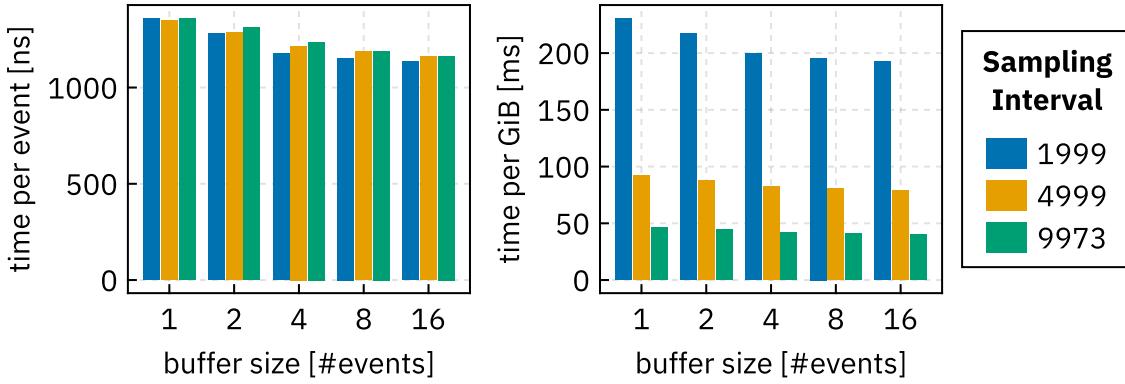

| 6.6.2    | Overhead and Latency .....                                       | 89         |

| 6.6.3    | Scheduling .....                                                 | 91         |

| 6.7      | Related Work .....                                               | 92         |

| 6.8      | Discussion .....                                                 | 92         |

| <b>7</b> | <b>Crash Consistency Testing .....</b>                           | <b>95</b>  |

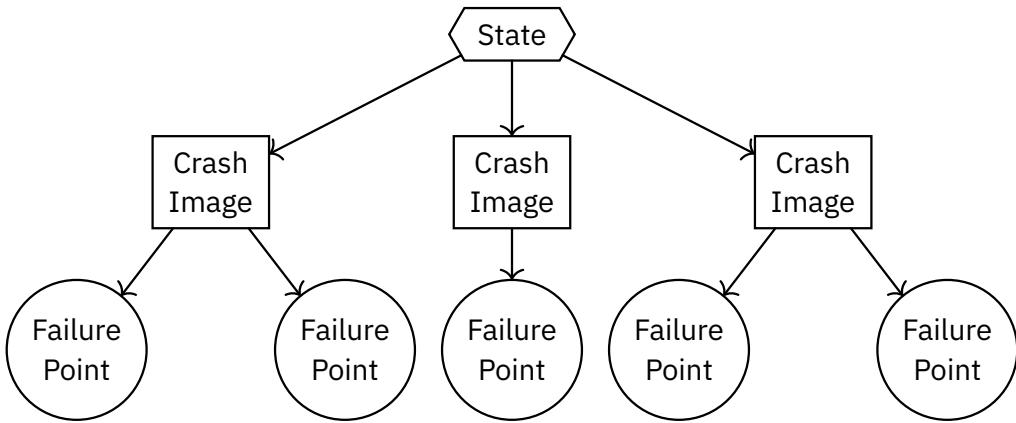

| 7.1      | Failure Points and Crash Images .....                            | 95         |

| 7.2      | Types of Crash Consistency Bugs .....                            | 96         |

| 7.2.1    | Logic Bugs .....                                                 | 96         |

| 7.2.2    | Missing Flush .....                                              | 97         |

| 7.2.3    | Ordering Bug .....                                               | 97         |

| 7.2.4    | Performance Bugs .....                                           | 98         |

| 7.3      | Crash Consistency Testing Pipeline .....                         | 98         |

| 7.4      | Tracing Approaches .....                                         | 98         |

| 7.4.1    | Binary Translation .....                                         | 99         |

| 7.4.2    | Compiler Instrumentation .....                                   | 99         |

| 7.4.3    | Manual Annotation .....                                          | 100        |

| 7.4.4    | Function Tracing .....                                           | 100        |

| 7.5      | Crash Consistency Testing Tools .....                            | 100        |

| 7.5.1    | Yat .....                                                        | 101        |

| 7.5.2    | PMTest .....                                                     | 102        |

| 7.5.3    | XFDetector .....                                                 | 102        |

| 7.5.4    | Witcher .....                                                    | 103        |

| 7.5.5    | Vinter .....                                                     | 104        |

| 7.5.6    | Chipmunk .....                                                   | 104        |

| 7.5.7    | Mumak .....                                                      | 105        |

| <b>8</b> | <b>Suvi: Crash Consistency Testing for PM File Systems .....</b> | <b>107</b> |

| 8.1      | Tracer .....                                                     | 108        |

| 8.1.1    | PM Tracing .....                                                 | 109        |

| 8.1.2    | NVMe Tracing .....                                               | 110        |

| 8.1.3    | Hypercalls .....                                                 | 112        |

| 8.1.4    | Discussion .....                                                 | 112        |

| 8.2      | Crash Image Generator .....                                      | 113        |

| 8.2.1    | Model Goals .....                                                | 113        |

| 8.2.2    | Crash Image Metadata .....                                       | 114        |

| 8.3      | PM Crash Image Model .....                                       | 115        |

| 8.3.1    | Trace Replay .....                                               | 115        |

| 8.3.2    | Failure Points .....                                             | 115        |

| 8.3.3    | Global Store Ordering .....                                      | 116        |

| 8.3.4    | Mixed Non-Temporal and Cached Stores .....                       | 116        |

| 8.3.5    | Crash Images with Volatile Caches .....                          | 117        |

| 8.3.6    | Crash Images with Persistent Caches (eADR) .....                 | 119        |

|                   |                                                                     |            |

|-------------------|---------------------------------------------------------------------|------------|

| 8.3.7             | Partial Application of Non-Temporal Stores .....                    | 121        |

| 8.4               | PM Crash Image Heuristics .....                                     | 121        |

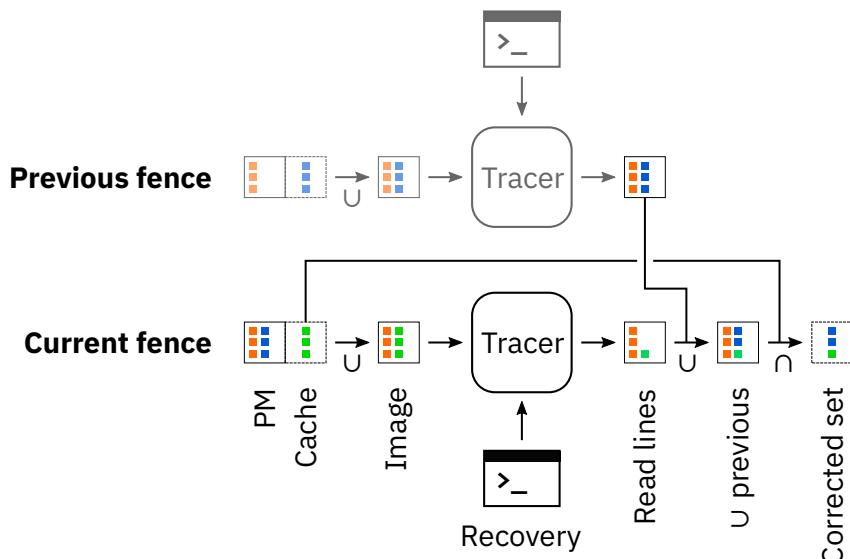

| 8.4.1             | <b>Suvi-Reads</b> : Efficient Exploration of Crash States .....     | 121        |

| 8.4.2             | <b>Suvi-NT</b> : Detecting NT-Dependent Semantic States .....       | 125        |

| 8.4.3             | <b>Suvi-Fast</b> : Fast Crash Image Generation for Logic Bugs ..... | 127        |

| 8.5               | Cross-Media Crash Images .....                                      | 128        |

| 8.5.1             | NVMe Crash Images .....                                             | 128        |

| 8.5.2             | Combined Crash Images .....                                         | 130        |

| 8.5.3             | Discussion .....                                                    | 131        |

| 8.6               | Tester .....                                                        | 131        |

| 8.6.1             | State Extraction .....                                              | 131        |

| 8.6.2             | State Analysis .....                                                | 135        |

| 8.7               | Trace Analysis .....                                                | 137        |

| 8.7.1             | Trace Debugging .....                                               | 137        |

| 8.7.2             | Trace Heuristics .....                                              | 139        |

| <b>9</b>          | <b>Suvi: Implementation</b> .....                                   | <b>141</b> |

| 9.1               | Tracer .....                                                        | 141        |

| 9.1.1             | PANDA .....                                                         | 141        |

| 9.1.2             | QEMU .....                                                          | 142        |

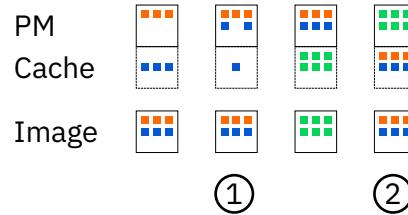

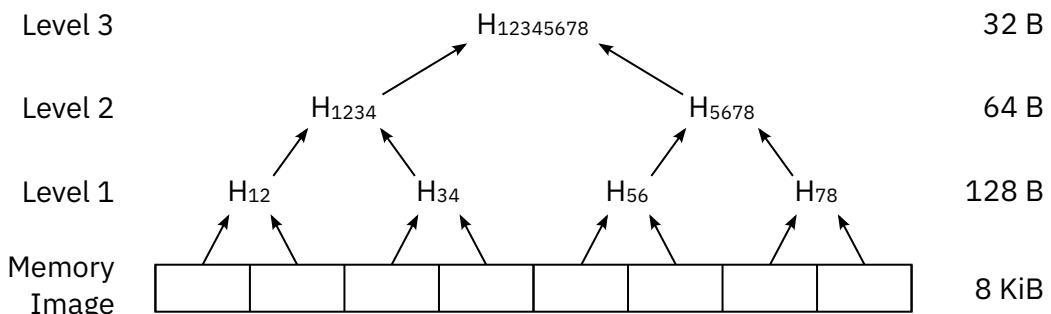

| 9.2               | Memory Images .....                                                 | 142        |

| 9.2.1             | File System Copy-on-Write .....                                     | 143        |

| 9.2.2             | Hash Memoization .....                                              | 143        |

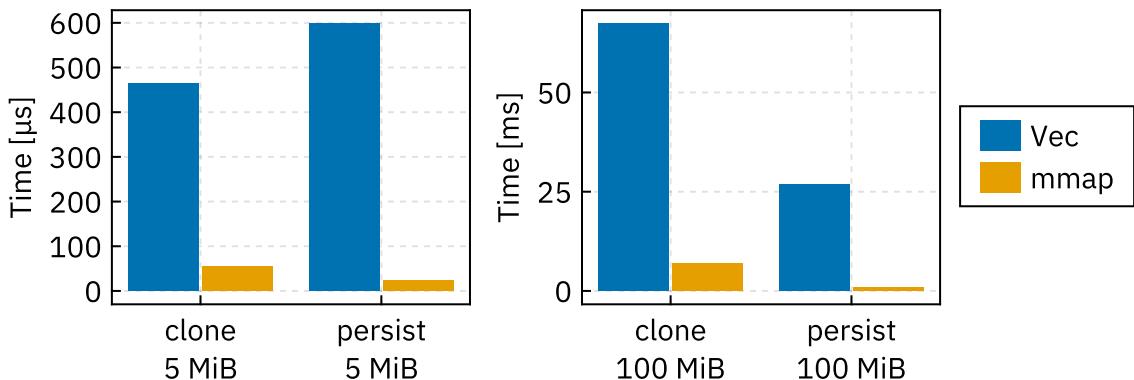

| 9.2.3             | Evaluation .....                                                    | 144        |

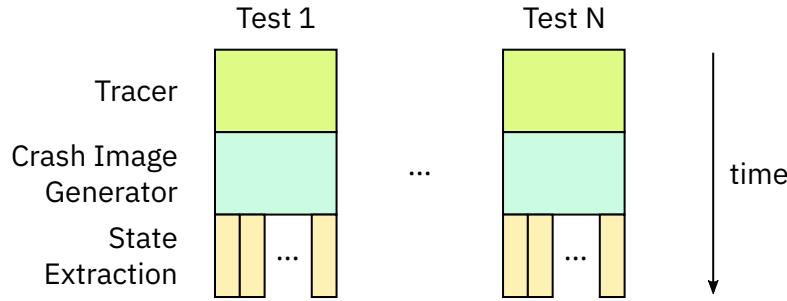

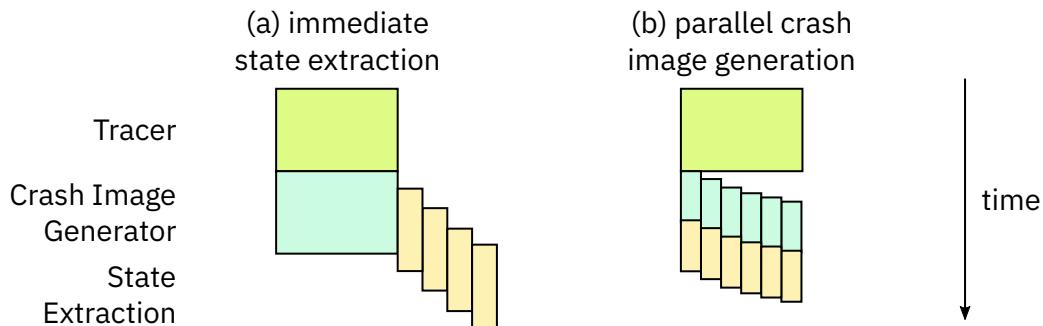

| 9.3               | Parallelization .....                                               | 145        |

| 9.3.1             | Discussion .....                                                    | 146        |

| <b>10</b>         | <b>File System Testing with Suvi</b> .....                          | <b>149</b> |

| 10.1              | Virtual Machine Setup .....                                         | 149        |

| 10.2              | Test Cases .....                                                    | 150        |

| 10.2.1            | 10.2.1 Vinter Test Cases .....                                      | 150        |

| 10.2.2            | 10.2.2 Automatic Test Case Generation .....                         | 151        |

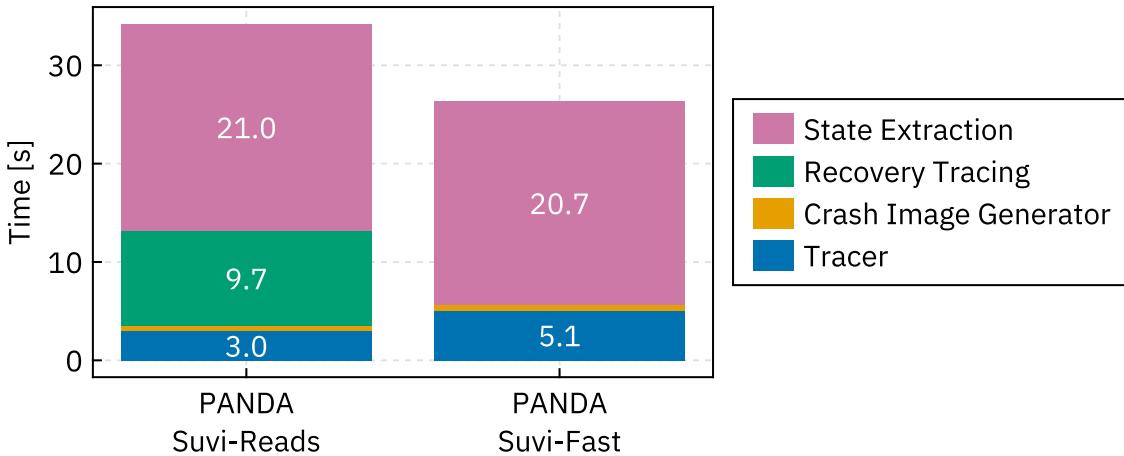

| 10.3              | Performance .....                                                   | 151        |

| 10.3.1            | 10.3.1 Heuristics .....                                             | 151        |

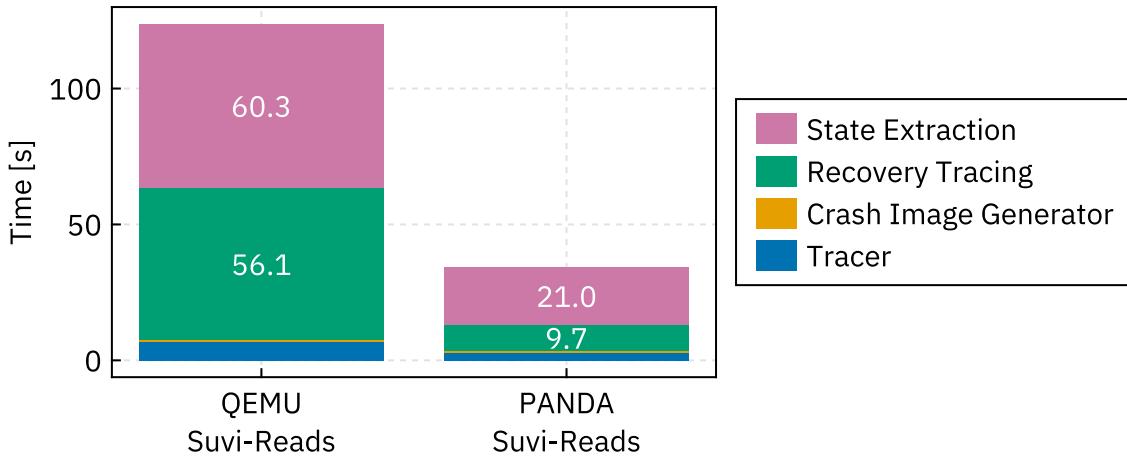

| 10.3.2            | 10.3.2 Tracer Implementations .....                                 | 152        |

| 10.3.3            | 10.3.3 Parallelization .....                                        | 153        |

| 10.4              | Results .....                                                       | 153        |

| 10.4.1            | 10.4.1 NOVA and NOVA-Fortis .....                                   | 153        |

| 10.4.2            | 10.4.2 PMFS and WineFS .....                                        | 155        |

| 10.4.3            | 10.4.3 ZIL-PMEM .....                                               | 155        |

| 10.5              | Persistent Caches .....                                             | 155        |

| 10.6              | Discussion .....                                                    | 156        |

| <b>11</b>         | <b>Conclusion</b> .....                                             | <b>159</b> |

| 11.1              | Outlook .....                                                       | 160        |

| <b>References</b> | .....                                                               | <b>163</b> |

# Chapter 1

## Introduction

### 1.1 Motivation for Persistent Memory

Modern systems have an increasing need for high-performance storage. Applications such as key-value stores [101], graph processing [64], and search indices [49, 51] require storage systems that can retrieve and modify data with minimal latency.

Traditional solid-state drives (SSDs) based on NVMe cannot properly fulfill this role. As both the SSDs and interconnects such as PCIe are getting faster, the relative overhead from storage accesses with NVMe increases. Approaches for kernel bypass can decrease this overhead [62, 83], but require exclusive device access for a single application.

Persistent memory (PM) offers a better solution. PM is byte-addressable and accessed directly from the CPU like main memory, but retains its contents while the system is powered off. PM therefore supports access with low latency, even for small access sizes. With regular paging, the operating system can offer direct PM access to userspace applications. In contrast to kernel bypass with NVMe, the operating system retains control over access permissions, allowing sharing of PM between multiple applications.

Intel Optane PM was the first widely-available commercial implementation of PM. Like DRAM, Optane modules come in the DIMM form factor and attach directly to the CPU's memory controller. We base most of the analysis in this thesis on Intel Optane PM.

More recently, support for Compute Express Link (CXL) appeared in CPUs from multiple vendors, including Intel and AMD. With CXL, devices attached via a PCIe link can offer byte-addressable PM. We expect that most of the techniques we introduce for Optane PM in this thesis also apply to CXL-attached PM.

File systems provide structured and controlled access to storage devices. By targeting a common file system API, applications can store data without knowledge of the underlying storage technology. The file system controls access permissions and allows safe shared access to different applications. Although PM can be used without a file system, file systems remain valuable for these reasons.

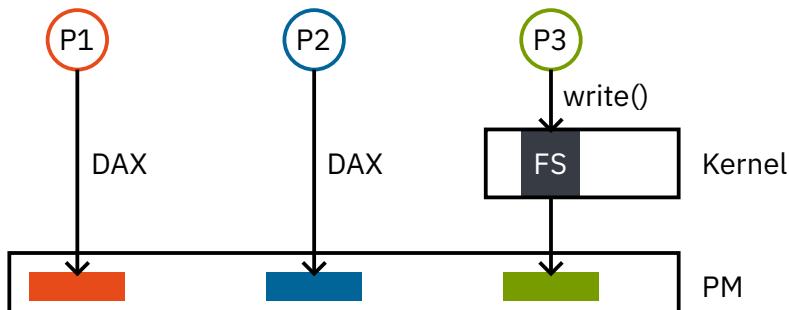

Most PM file systems offer *direct access* (DAX) to applications, a feature not found in regular file systems. With DAX, the file system provides memory mappings to a file's PM pages. After establishing such a mapping, an application can read and write to PM without further involvement of the operating system, bypassing the kernel.

## 1.2 Challenges for PM File Systems

PM can offer its low latency thanks to its integration into the CPU's memory hierarchy, allowing synchronous and direct access at byte granularity. In comparison, traditional storage devices are accessed over an asynchronous protocol. The operating system submits requests for data blocks, which the storage device fulfills by copying the data to system memory and then signaling request completion. From blocks to bytes is a change of paradigm that introduces novel challenges in the design and implementation of file systems for performance, efficiency, and correctness.

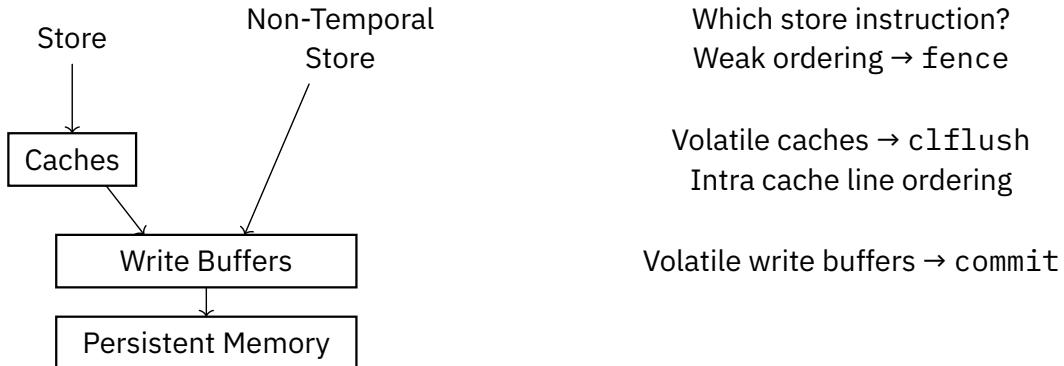

A correct file system implementation should be *crash-consistent*. In the event of a crash, the file system's data structures should remain consistent to avoid corrupted or lost files. Traditional storage devices support crash-consistent file system design by offering atomic block updates of typically 512 or 4096 bytes. In the event of a crash during a write operation, such a block is either written completely or not at all. With PM, the CPU's memory write path offers a much smaller atomic write size of only 8 bytes. Additionally, PM file systems and applications need to manage volatile state in the write path (e.g., caches and write buffers) by introducing special instructions called *PM primitives*. Correct use of these PM primitives is challenging since they do not have a visible effect on the application data during runtime but are critical for consistency after a crash.

Synchronous access to PM from the CPU is essential for low latency but becomes expensive once the PM is under load and cannot answer requests immediately. On traditional storage devices with asynchronous access, the operating system can schedule other processes during the wait time or put the CPU in a low-power sleep state. This is not possible with PM, as individual PM accesses are not visible to the operating system. Instead, the CPU pipeline stalls during the wait time, wasting CPU time and energy.

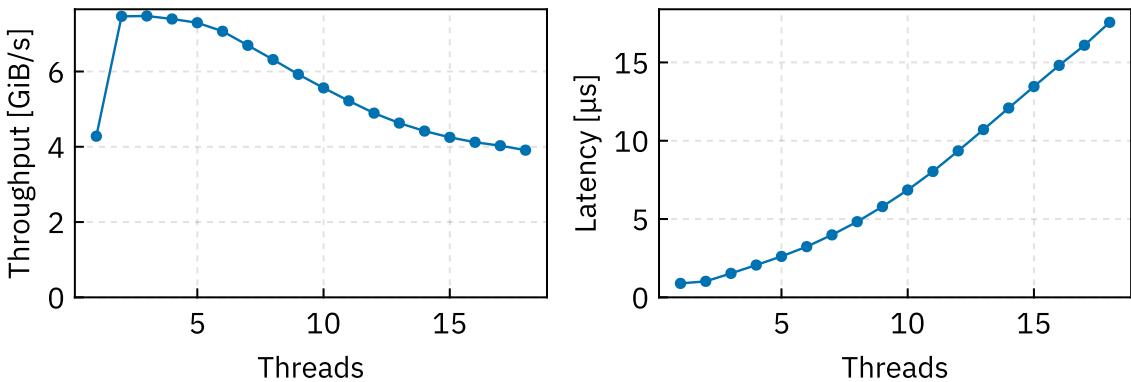

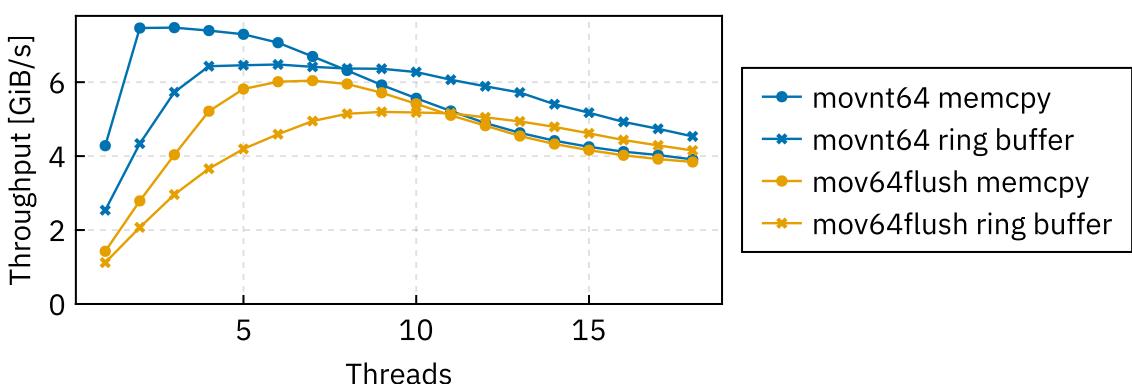

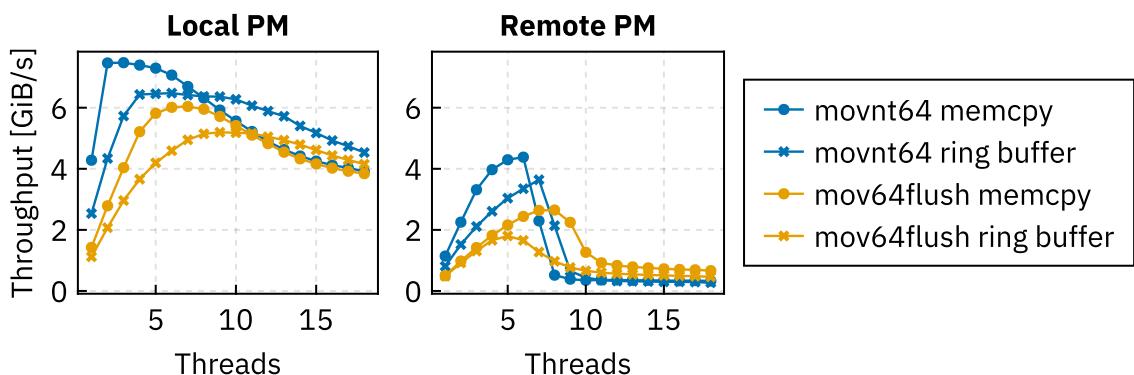

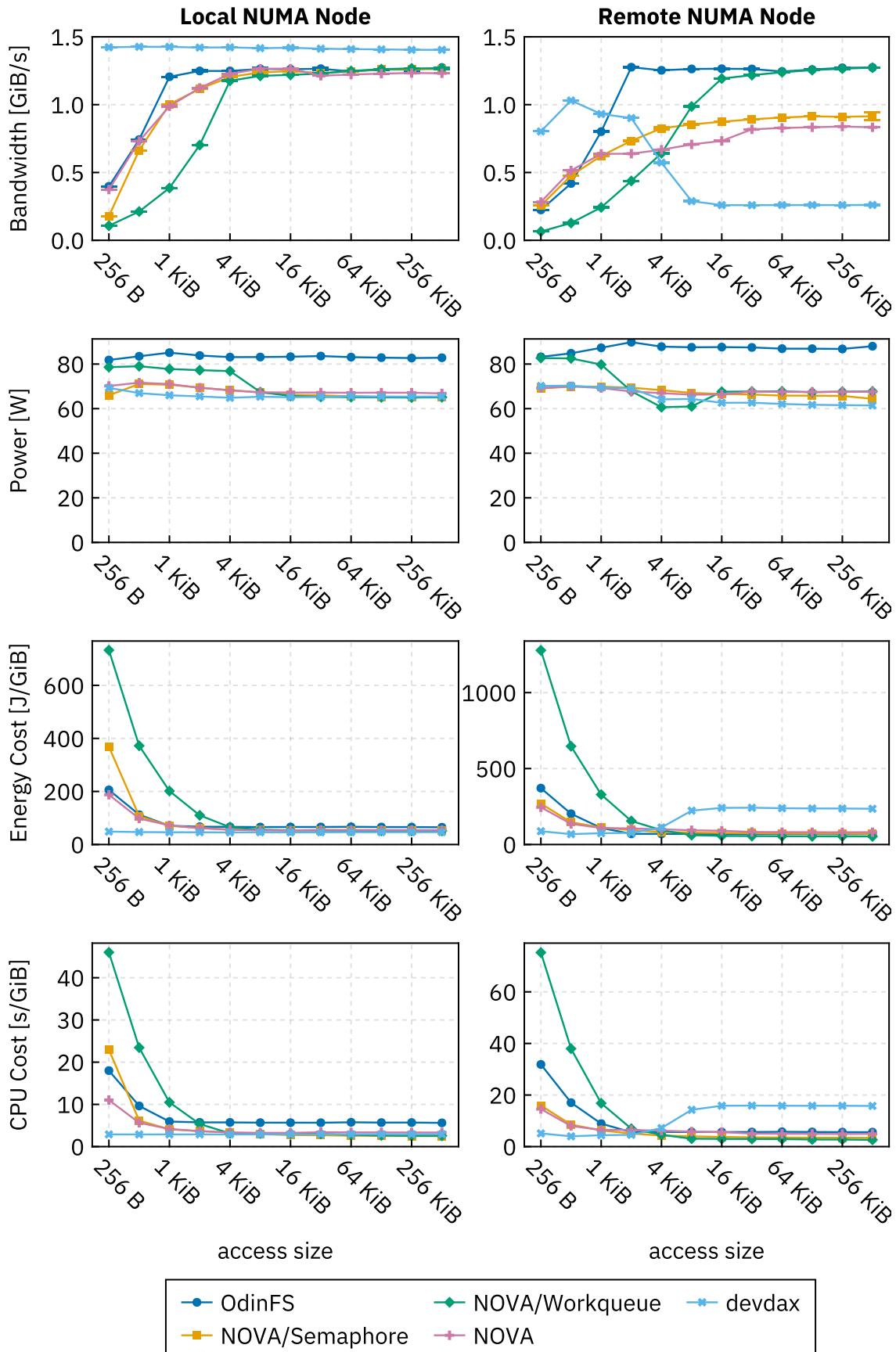

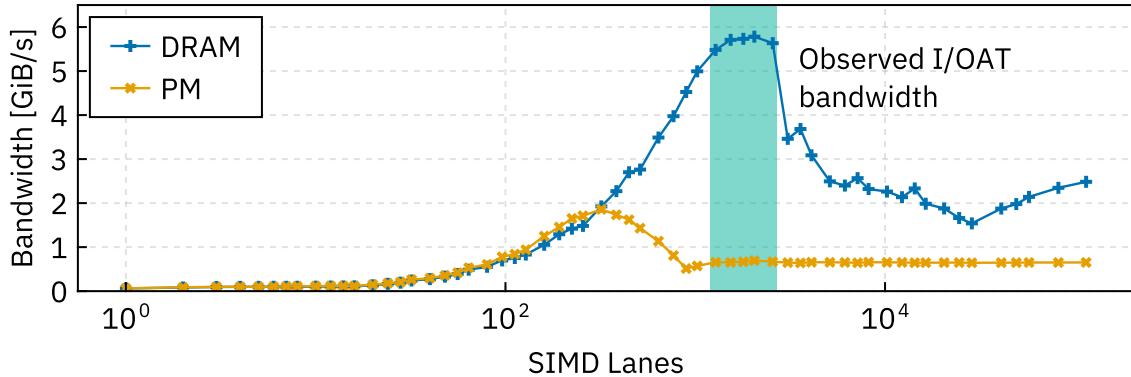

This problem is amplified with Optane PM due to its sensitivity to parallel accesses. Because of internal caching structures, its total throughput declines under parallel load, as shown in Figure 1.1. Individual threads then experience a significant

Figure 1.1: Throughput and latency of 4 KiB writes to Optane PM.

increase in access latency and, therefore, CPU stall cycles. To mitigate this problem, PM file systems and applications must limit parallel accesses to PM.

A secondary challenge follows from this requirement. After obtaining a direct PM mapping, applications can access PM without further involvement of the file system. This results in a situation in which neither the file system nor the application can manage parallel PM accesses. The file system does not have knowledge of application activity, and an application cannot know about the activity of other applications.

## 1.3 Measuring and Improving PM Efficiency

Since file systems act as an abstraction layer between applications and storage, they are responsible for ensuring that the storage is accessed as efficiently as possible for any given workload. For example, file systems for hard disks commonly reduce seeks by arranging related data blocks sequentially. Additionally, operating systems include I/O schedulers that can rearrange asynchronous requests to traditional storage devices. Similar I/O scheduling is not feasible for synchronously accessed PM.

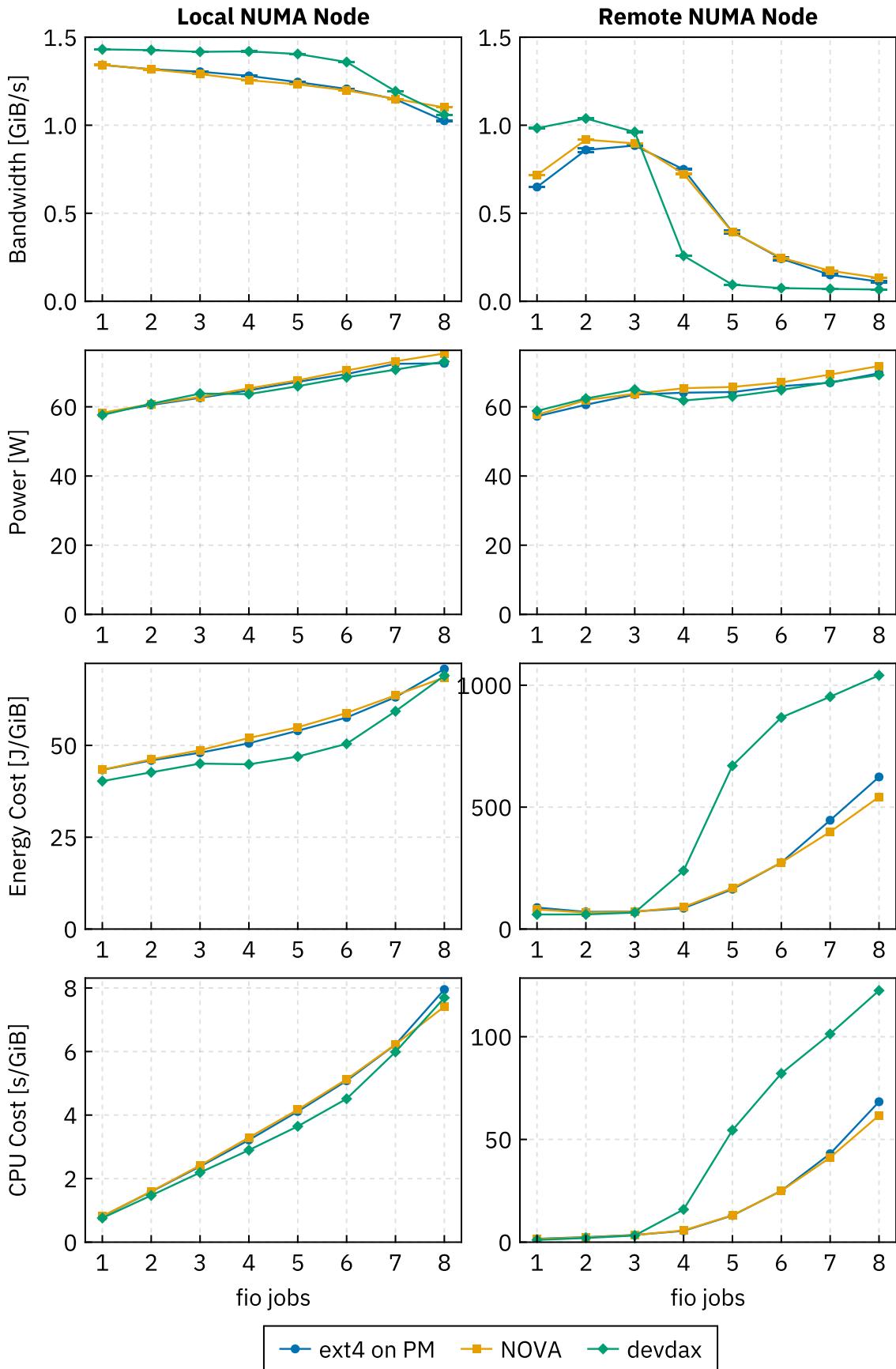

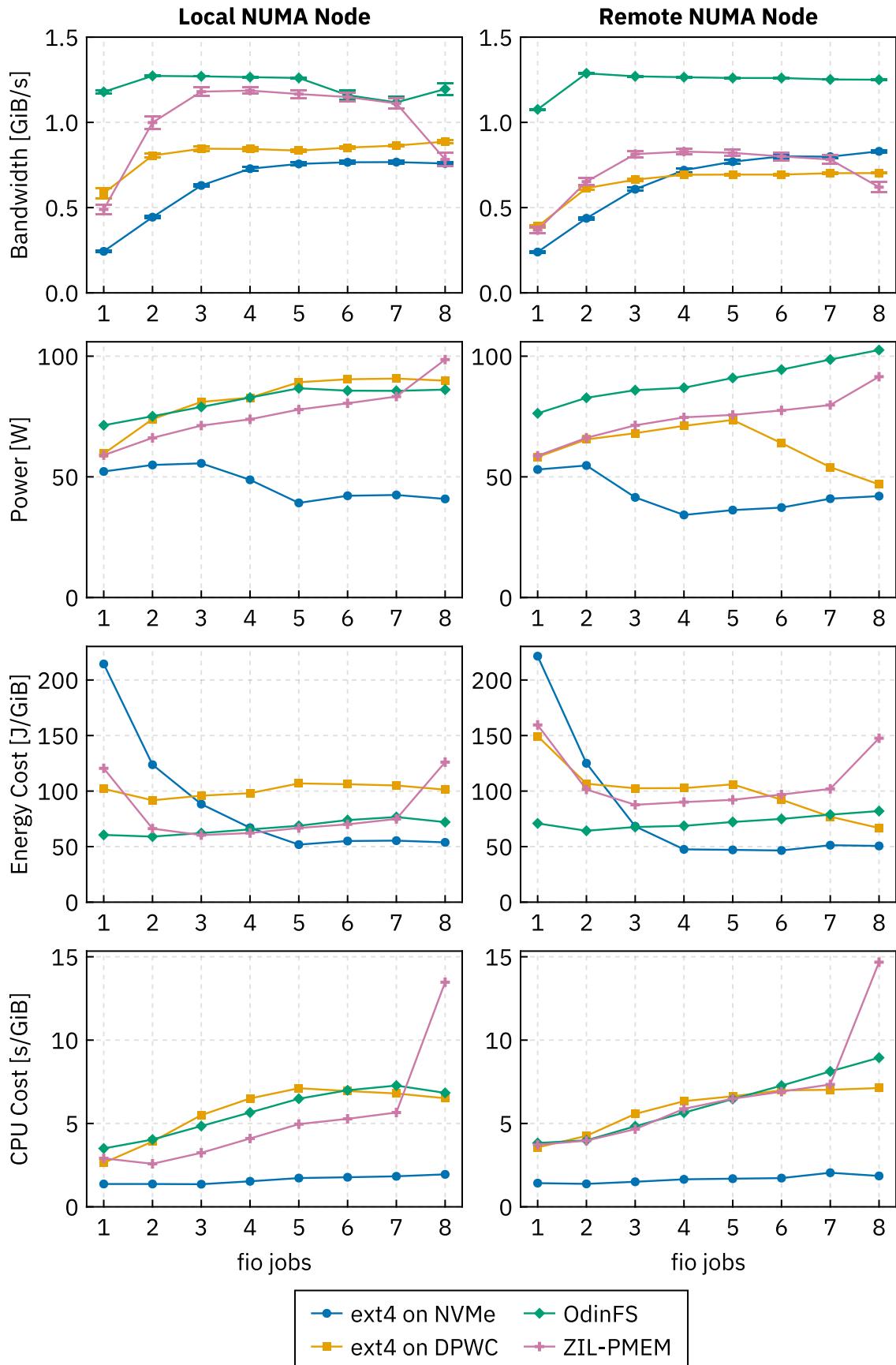

In this thesis, we introduce approaches for measuring and improving the efficiency of PM file systems. Our efficiency metrics assign a specific cost (CPU time or energy) to accessing a certain amount of storage. We design the metrics so that they are independent of storage device throughput and CPU clock speed. We evaluate multiple file systems and find that most PM file systems do not access PM efficiently under a parallel write load.

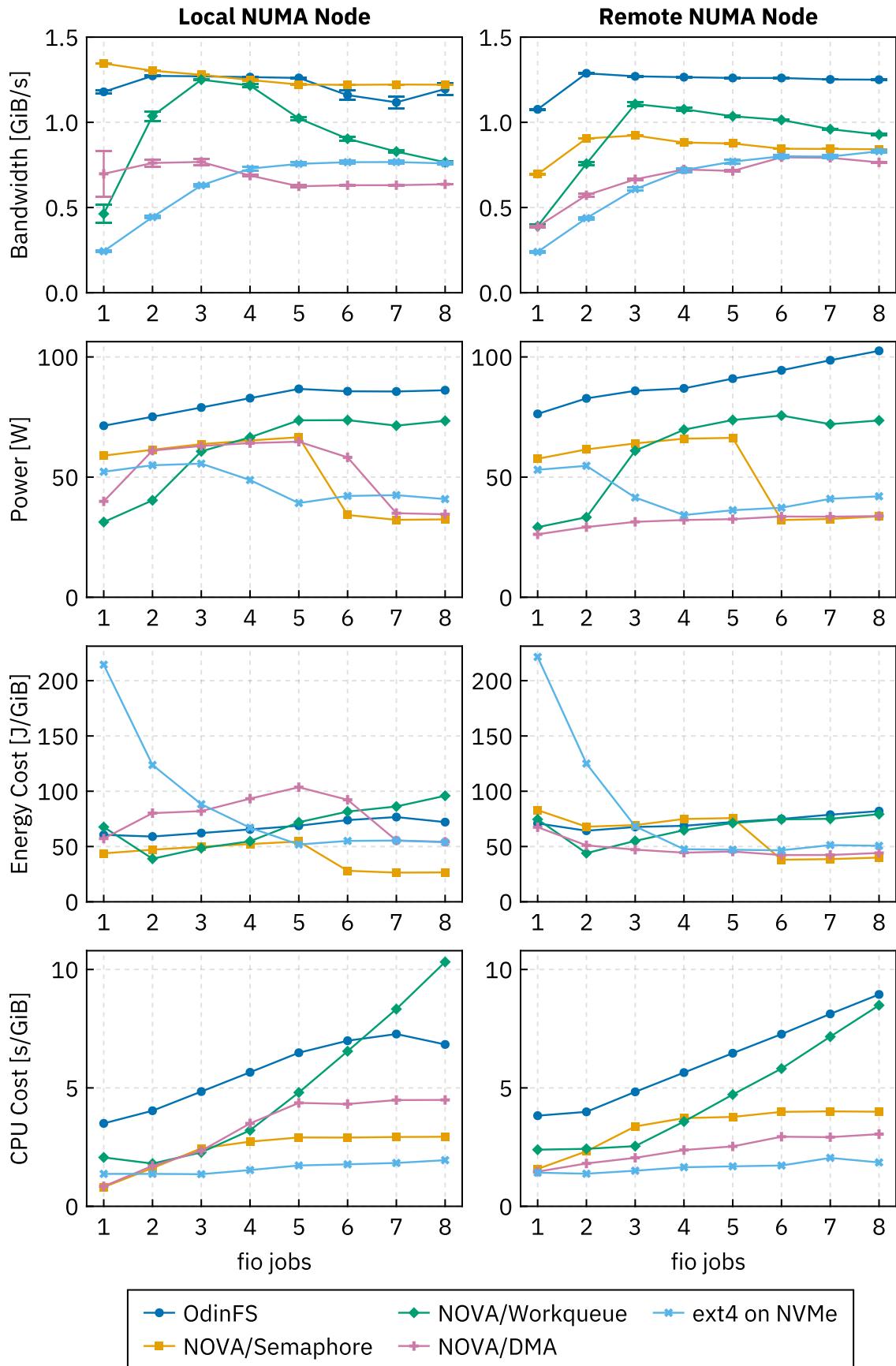

We propose three mechanisms for improving the efficiency of PM file systems under parallel load. We design these mechanisms to be easily integrable into existing PM file systems. They include two software-based approaches for limiting parallel accesses and another approach based on hardware offloading. We show that these mechanisms are effective for improving PM file system efficiency. In combination with our efficiency metric, we expect future file system designs to incorporate efficient PM access into their designs.

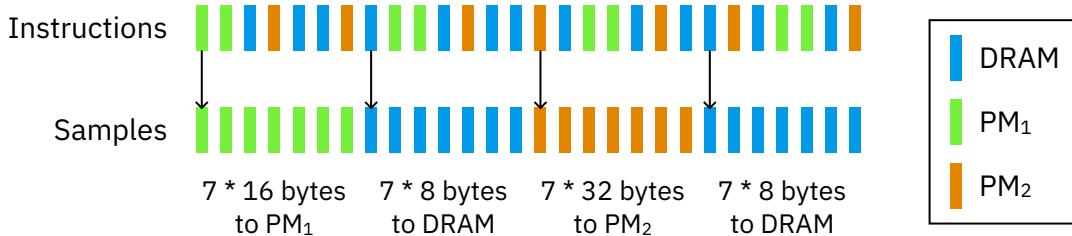

Our efficiency metric and the mechanisms can only cover PM accesses over the file system API. Applications that access PM over DAX mappings cannot be covered. As discussed above, such applications should still avoid overloading PM with excessive parallel accesses. Effective limits require a global view of the volume of PM accesses from all concurrently running applications. Existing hardware and operating system mechanisms cannot provide this information with association to both applications and PM devices. We introduce a monitoring approach based on memory access instruction sampling that provides the required association. We show that our monitoring estimates PM write bandwidth accurately and with low latency.

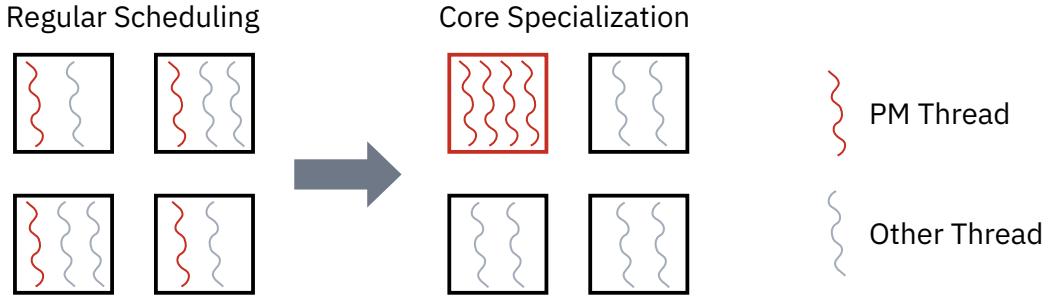

We make the monitoring data available to applications via shared memory, allowing them to react immediately to overload situations. Using this monitoring data, we implement a policy based on *core specialization* that can limit the number of CPU cores stalling on PM accesses.

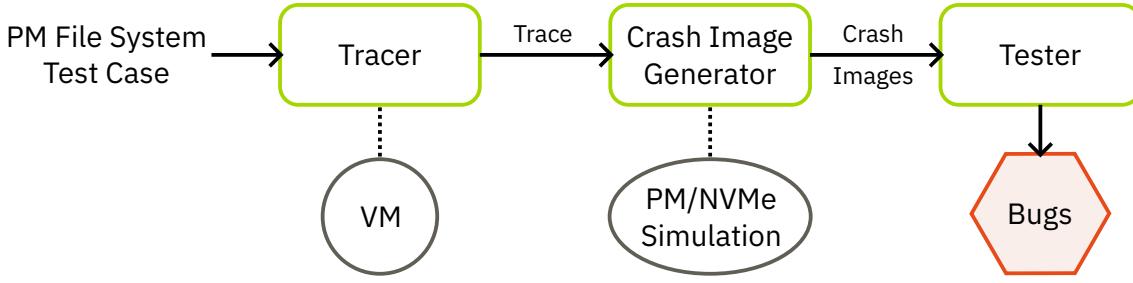

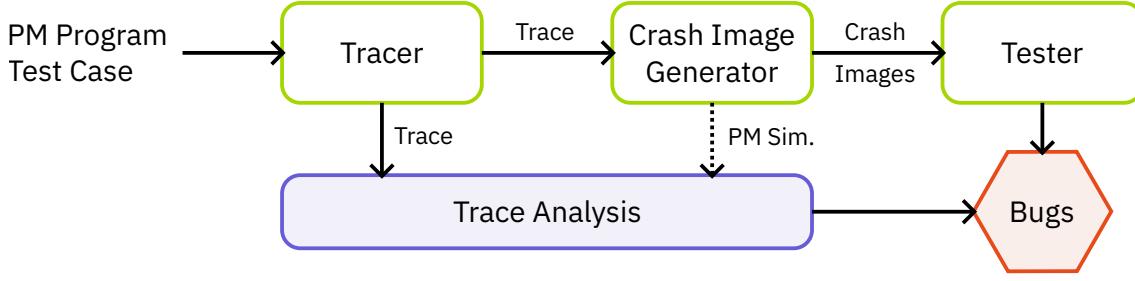

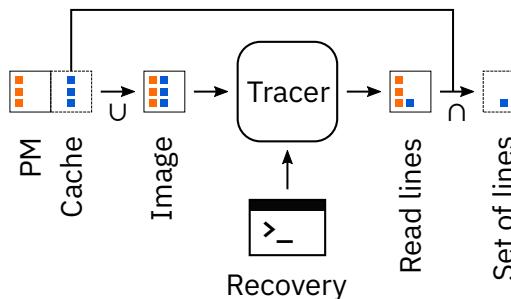

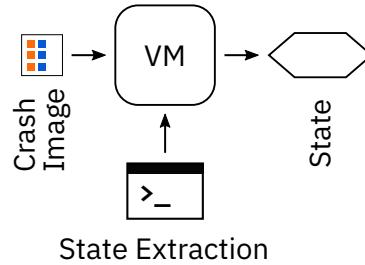

Figure 1.2: Suvi's crash consistency testing pipeline.

## 1.4 PM File System Crash Consistency

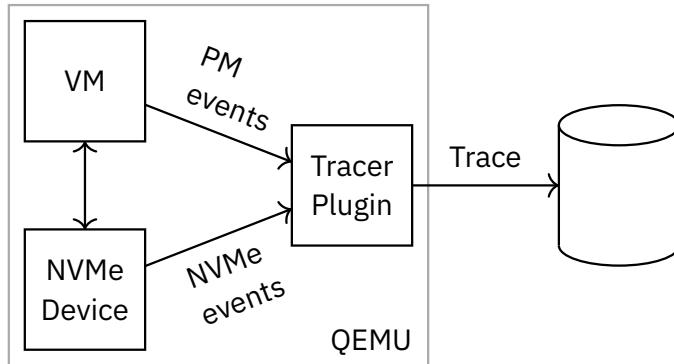

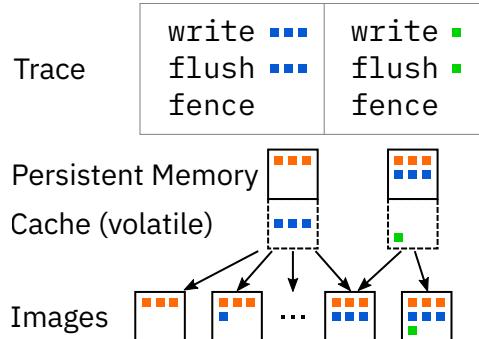

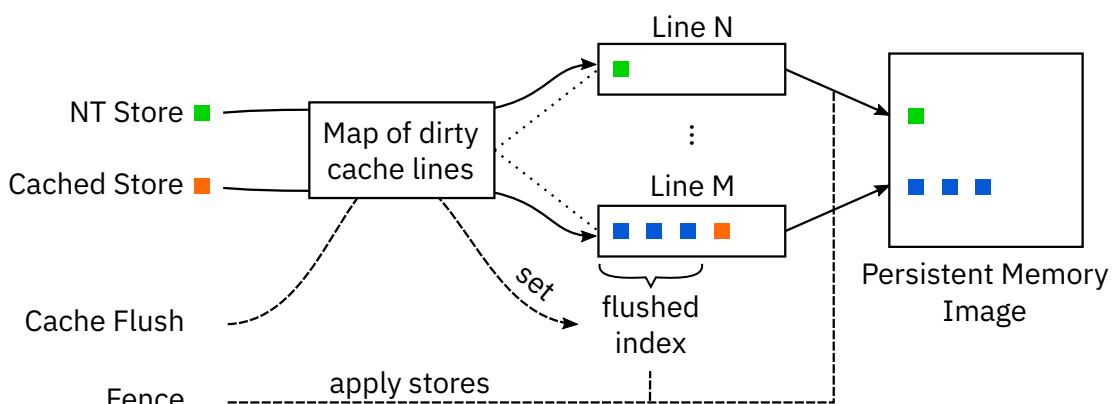

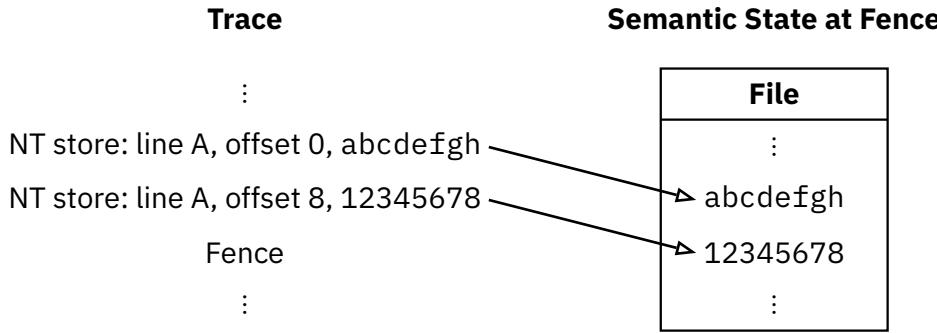

The correct use of PM primitives is critical for PM file systems to ensure data consistency after a crash. In this thesis, we introduce **Suvi**, an approach for black-box crash consistency testing of PM file systems. As a black-box approach, **Suvi** places minimal requirements on the tested software and can analyze any PM file system running in a virtual machine. Rather than employing heuristics for bug detection, **Suvi** uses a record-and-replay approach that finds concrete witnesses for crash consistency bugs.

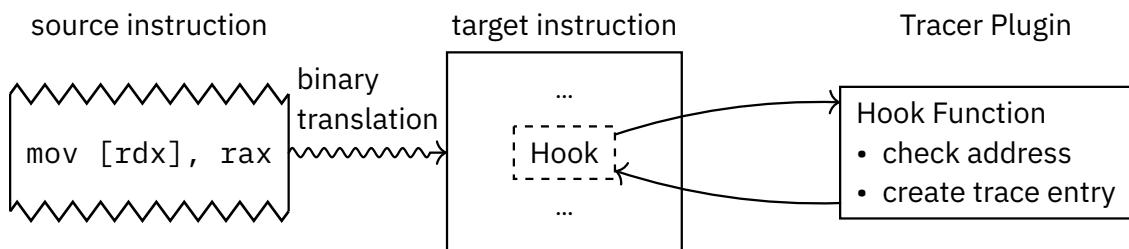

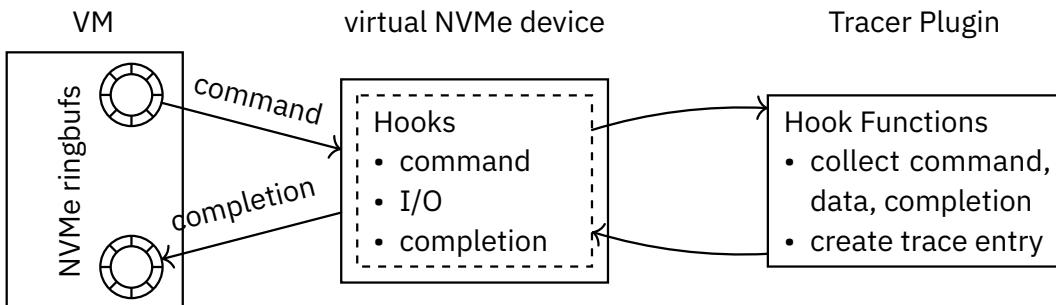

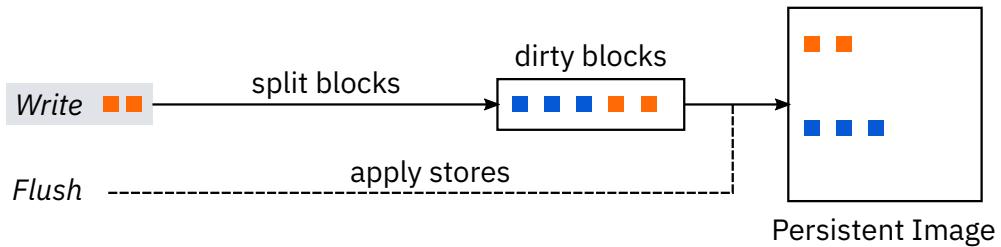

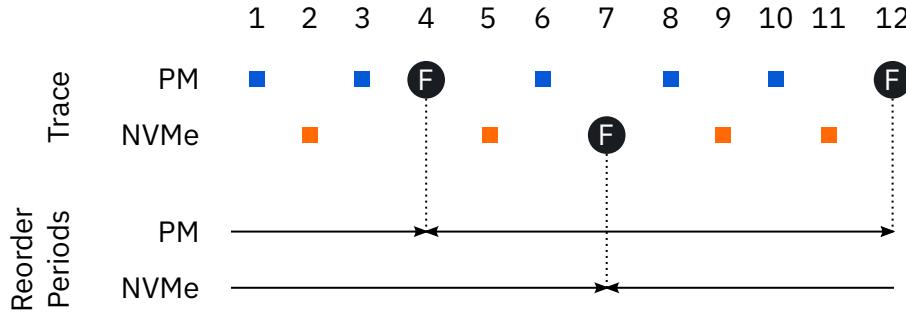

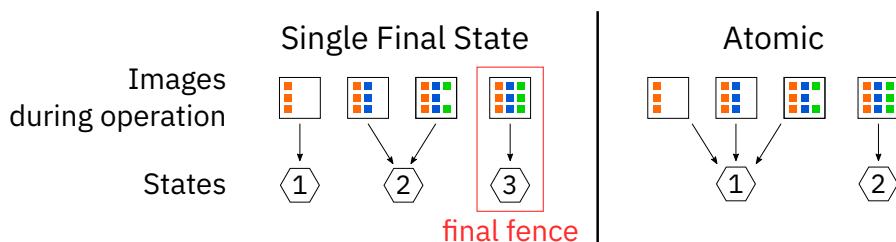

**Suvi** implements a crash consistency testing pipeline, shown in Figure 1.2, that traces PM accesses of a test case in a virtual machine. From the trace, it generates *crash images* that represent possible PM contents in the event of a crash. Finally, **Suvi** can automatically determine the crash atomicity of file system operations by analyzing the semantic state contained in the crash images.

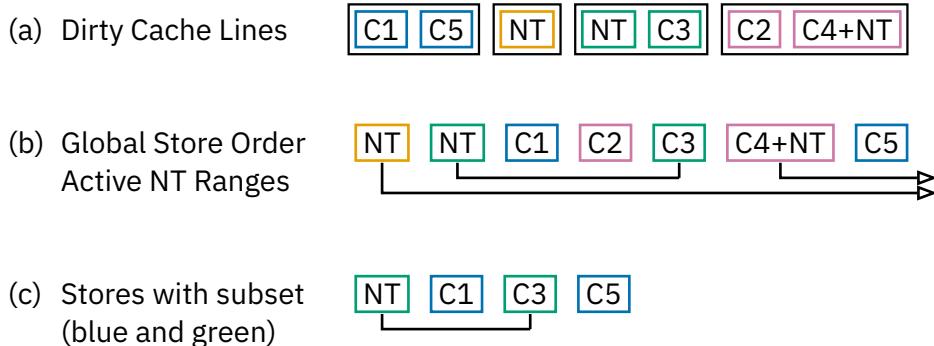

**Suvi** innovates on previous approaches to crash consistency testing in multiple ways. It offers full-system tracing of PM and NVMe accesses using virtual machines with binary translation, allowing analysis of cross-media file systems that use these storage technologies. It includes an advanced PM simulation that models the ordering of x86 store instructions more precisely than other crash consistency testing approaches and supports both volatile and persistent caches. Two heuristics ensure efficient generation of crash images by avoiding a combinatorial explosion when there is a large number of PM stores. By using file system copy-on-write and a memoized hashing scheme, **Suvi** makes the analysis of large PM images feasible. Finally, **Suvi**'s analysis tools allow the automatic detection of crash consistency bugs and help developers identify the causes of such bugs.

## 1.5 Contributions

Our work presented in this thesis makes the following contributions:

- We introduce novel metrics for file system efficiency. The metrics measure the efficient use of CPU time and energy. We design them to be independent of both storage device throughput and CPU clock speed.

- We evaluate multiple file systems (PM and NVMe) with our metrics. Our results show that most PM file systems were not designed with efficiency in mind.

- We propose and evaluate measures to improve the efficiency of PM file systems by mitigating PM overload.

- We propose an approach for accounting userspace PM accesses that can associate throughput with both processes and PM devices. We evaluate the accuracy and overhead of our approach. Using the accounting data, we propose PM overload mitigation based on *core specialization*.

- We introduce **Suvi**, a comprehensive approach for black-box crash consistency testing of file systems based on virtual machines. In particular, **Suvi** encompasses:

- Support for analyzing cross-media file systems using PM and NVMe.

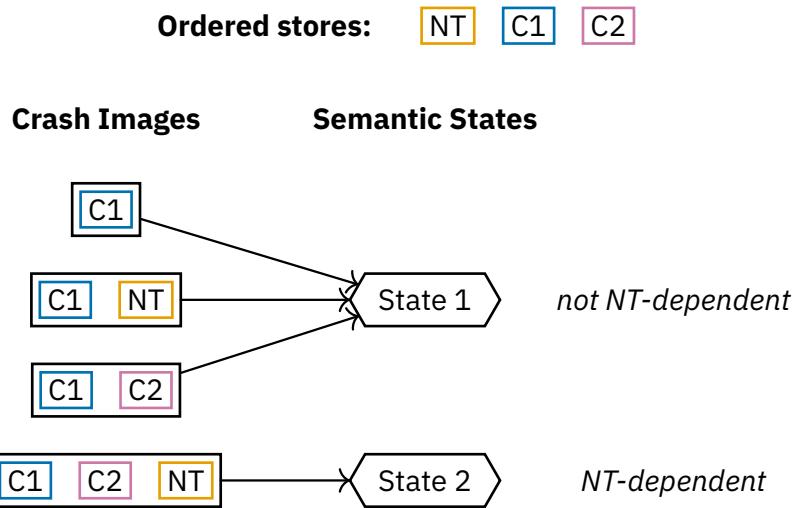

- An improved simulation of x86 PM crash consistency semantics. Compared to previous work, it models the interaction of x86 global store order with weakly ordered non-temporal stores more accurately.

- Simulation of both volatile and persistent caches.

- Two primary strategies for efficiently generating crash images: an improved heuristic based on post-failure read accesses and a strategy for fast analysis of logic bugs.

- A secondary heuristic for exploring crash states with weakly ordered non-temporal stores.

- Novel handling of PM images through file system copy-on-write and memoized hashing, optimized for small modifications to large images.

- Automated analysis of test results for atomicity, including tools for pinpointing the root cause of bugs.

## 1.6 Student Theses and Publications

Parts of this thesis are based on previously published information. We supervised a number of student theses that contributed to this thesis:

- In his master's thesis *Low-Latency Synchronous IO For OpenZFS Using Persistent Memory*[111], Christian Schwarz introduced ZIL-PMEM, a component for ZFS that logs synchronous writes on PM. The design and implementation of ZIL-PMEM motivate large parts of this thesis. We discuss ZIL-PMEM in Chapter 3, where we use a reimplementation of its low-level PM data structure to analyze Optane PM performance. Research in crash consistency testing that resulted in Vinter and **Suvi** was motivated by a desire to verify correctness of the implementation of ZIL-PMEM.

- With his master's thesis *Automatic Non-Volatile Memory Crash Consistency Testing for Full Systems* [69], Samuel Kalbfleisch provided the basis for Vinter [68]. We build **Suvi**, as presented in this thesis, on a reimplementation of his Python prototype in the Rust programming language.

- In his bachelor's thesis *Reducing Synchronous Write Latency With a PMEM Write Cache in the Device Mapper Layer* [32], Ilia Bozhinov adapts the PM data structure from ZIL-PMEM for use as a generic block device write cache. We analyze his implementation in Chapter 4.

- Daniel Ritz designed and implemented a crash consistency tester for NVMe in his bachelor's thesis *Crash Consistency Testing for Block Based File Systems on NVMe*

*Drives* [105]. Parts of his approach, especially for tracing NVMe commands, are part of **Suvi**'s support for NVMe.

- In his master's thesis *GPU4FS: A Graphics Processor-Accelerated File System* [91], Peter Maucher explored implementing a complete file system on a GPU. His analysis of PM accesses from a GPU informed our discussion of memcpy offloading in Chapter 5.

- Thomas Schmidt explored performance counters for accounting PM usage in his master's thesis *Achieving Optimal Throughput for Persistent Memory with Per-Process Accounting* [110]. His thesis included a userspace implementation of our idea for PEBS-based sampling, which failed to show useful results. For this reason, we created an independent kernelspace implementation for Chapter 6.

- In his bachelor's thesis *Crash Consistency Testing for Cross-Media File Systems using Persistent Memory and NVMe* [123], Lucas Wäldele united Vinter and Daniel Ritz's NVMe crash consistency tester. The major effort of this thesis was the implementation of PM tracing on top of modern QEMU since Vinter's PANDA-based tracer does not support NVMe. **Suvi**'s cross-media tracer evolved from his work.

- For his bachelor's thesis *Analyzing Persistent Memory Crash Consistency of WineFS with Vinter* [119], Paul Wedeck designed and implemented multiple small improvements to Vinter that we integrated into **Suvi**. Most prominently, these include support for parallel analysis of multiple tests and parallel state extraction.

- Thomas-Christian Oder integrated Mumak's [46] strategy for crash image generation into Vinter in his bachelor's thesis *Fast Persistent Memory Crash Consistency Analysis based on Virtual Machines* [99]. We adopt this strategy in **Suvi** as described in Chapter 8.

We previously presented parts of this thesis in the publications listed below. At USENIX ATC'22 [68] we introduced Vinter, an approach to PM crash consistency testing that provides the basis for **Suvi**. We later presented extensions to Vinter at FGBS'24 [121] that became part of **Suvi**, including cross-device analysis and faster crash image generation. At DIMES'23 [120], we presented our file system efficiency metric and mechanisms for improving the efficiency of PM file systems.

The remaining two publications are partially informed by the contributions of this thesis. With GPU4FS (FGBS'24 [90]), we take the idea of hardware offloading of PM accesses for efficiency further by moving the entire file system to the GPU. In our work on operating system support for CXL-based hybrid SSDs (DIMES'24 [50]), we evaluate efficiency using metrics from this thesis.

- Samuel Kalbfleisch, **Lukas Werling**, and Frank Bellosa. 2022. Vinter: Automatic Non-Volatile Memory Crash Consistency Testing for Full Systems. In *2022 USENIX Annual Technical Conference (USENIX ATC 22)*, 2022. 933–950. Retrieved from <https://www.usenix.org/conference/atc22/presentation/werling>

- **Lukas Werling**, Yussuf Khalil, Peter Maucher, Thorsten Gröninger, and Frank Bellosa. 2023. Analyzing and Improving CPU and Energy Efficiency of PM File Systems. In *Proceedings of the 1st Workshop on Disruptive Memory Systems*, October 2023. ACM, Koblenz Germany, 31–37. <https://doi.org/10.1145/3609308.3625265>

- **Lukas Werling**, Thomas-Christian Oder, Lucas Wäldele, Daniel Ritz, and Frank Bellosa. 2024. Improvements in Crash Consistency Testing for Persistent Memory File Systems. In *Tagungsband des FG-BS Frühjahrstreffens 2024*, 2024. Gesellschaft für Informatik e.V., Bochum, Germany. <https://doi.org/10.18420/FGBS2024F-01>

- Peter Maucher, Lennard Kittner, Nico Rath, Gregor Lucka, **Lukas Werling**, Yussuf Khalil, Thorsten Gröninger, and Frank Bellosa. 2024. Full-Scale File System Acceleration on GPU. In *Tagungsband des FG-BS Frühjahrstreffens 2024*, 2024. <https://doi.org/10.18420/FGBS2024F-03>

- Daniel Habicht, Yussuf Khalil, **Lukas Werling**, Thorsten Gröninger, and Frank Bellosa. 2024. Fundamental OS Design Considerations for CXL-based Hybrid SSDs. In *Proceedings of the 2nd Workshop on Disruptive Memory Systems (DIMES '24)*, November 2024. Association for Computing Machinery, New York, NY, USA, 51–59. <https://doi.org/10.1145/3698783.3699380>

## 1.7 Structure

The remainder of this work is structured into the following chapters:

### **Chapter 2** Background – Persistent Memory and File Systems (p. 21)

We first take a look at Intel Optane PM and how the Linux kernel supports PM, especially for use in file systems. We then give an overview of PM file systems that we evaluate for efficiency or crash consistency in later chapters.

### **Chapter 3** Motivation – Designing Data Structures for PM (p. 41)

We motivate our work in performance and crash consistency with a PM data structure for a file system.

### **Chapter 4** PM File System Efficiency (p. 55)

This chapter introduces our metrics for file system efficiency. We evaluate the metrics on multiple file systems and show that most PM file systems are not efficient under parallel accesses.

### **Chapter 5** PM File System Overload Mitigation (p. 73)

We then describe approaches for improving PM file system efficiency. We apply the approaches to a PM file system and compare their performance and efficiency.

### **Chapter 6** Userspace PM Access Accounting (p. 81)

The previous two chapters handled efficiency of PM access from the file system, which leaves out applications that map PM for direct access. In this chapter, we introduce an approach for accounting PM access from userspace applications with association of individual processes and PM devices.

### **Chapter 7** Crash Consistency Testing (p. 95)

We introduce fundamentals on crash consistency, discuss typical testing approaches, and review previous work.

**Chapter 8** Suvi: Crash Consistency Testing for PM File Systems (p. 107)

We then present **Suvi**, our approach to crash consistency testing for file systems.

**Chapter 9** Suvi: Implementation (p. 141)

We discuss details from **Suvi**'s implementation that are necessary for **Suvi**'s performance, including the tracer component, management of memory images, and parallelization.

**Chapter 10** File System Testing with Suvi (p. 149)

We show how **Suvi** can test file systems in practice. We describe test selection, evaluate performance, and discuss analysis results.

**Chapter 11** Conclusion (p. 159)

Finally, we conclude our work and discuss directions for future research.

# Chapter 2

## Background – Persistent Memory and File Systems

The goal of this thesis is to improve the efficiency and correctness of PM file systems. In this chapter, we introduce the storage stack on which this thesis builds. This includes Optane PM modules, PM support in the Linux kernel, several research PM file systems, and the crash consistency semantics of PM on x86 CPUs and for NVMe SSDs.

### 2.1 Optane Persistent Memory

Intel Optane Persistent Memory are persistent memory modules in the DIMM form factor.

Intel released three generations of Optane memory, shown in Table 2.1. Each generation was released together with a CPU from Intel’s Scalable product line. Optane DIMMs of each generation were available in three sizes (128 GiB, 256 GiB, 512 GiB). Optane 100 and 200 both use the DDR-T interface which has the same physical form factor as DDR4. Optane 300 uses DDR-T2 with the physical form factor of DDR5 DIMMs. First-generation Optane PM was introduced in 2019. Intel discontinued Optane before the release of the third generation in 2022 [89].

In this thesis, we evaluate with 128 GiB Optane 100 DIMMs on Cascade Lake systems (see Section 3.2 and Section 4.2.1 for detailed system overviews). We discuss Optane performance in Chapter 3.

Optane PM has two layers of configuration. The `ipmctl` [2] tool configures *regions* across one or more Optane modules. This tool is specific to Optane PM. On top of regions, the Linux kernel manages PM *namespaces*, which are configured with

| Generation | Year | Capacity [GiB] | CPU Generation     |

|------------|------|----------------|--------------------|

| 100 [8]    | 2019 | 128, 256, 512  | Cascade Lake SP    |

| 200 [9]    | 2020 | 128, 256, 512  | Ice Lake SP        |

| 300 [10]   | 2023 | 128, 256, 512  | Sapphire Rapids SP |

Table 2.1: Overview of Optane PM generations.

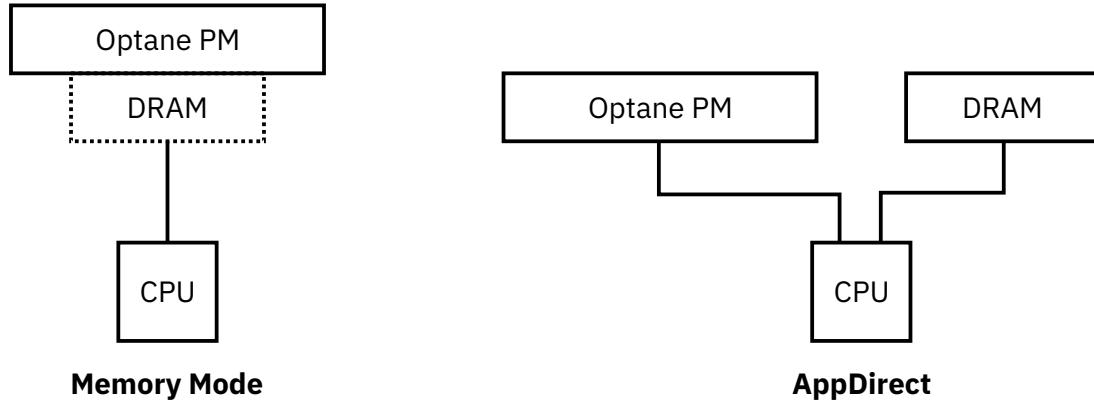

Figure 2.1: Logical view of Optane PM configured in Memory Mode and AppDirect mode.

ndctl [3]. Similar to partitions on block devices, namespaces allow separate management and configuration of parts of a PM region. Since namespaces are a concept by the Linux kernel, their use extends to other PM technologies. We discuss regions and namespace in more detail in the following sections.

### 2.1.1 Regions

A region spans one or more Optane modules connected to one CPU. Regions over multiple Optane modules are *interleaved*. The memory controller distributes accesses to an interleaved region over all modules. The interleaving size is 4 KiB [127]. Accesses over a sufficiently large memory area (e.g., 16 KiB with four interleaved modules) can therefore use the combined throughput of all modules.

There are two modes for regions: Memory Mode and AppDirect mode, pictured in Figure 2.1. In Memory Mode, the configured Optane capacity appears to the system as regular, volatile main memory. The memory controller transparently uses its connected DRAM as a cache to hide high access latencies to Optane. In this mode, Optane is only used for its larger capacity compared to DRAM, not for its persistence. In this thesis, we focus on Optane as persistent memory and do not further discuss Memory Mode.

In AppDirect mode, the Optane region appears separately to the system. The system firmware communicates the PM areas with the e820 memory map [44]. In the memory map, persistent memory areas are marked as type 7. Linux does not use these areas as main memory. Instead, they are handled by the NVDIMM subsystem [11], which manages namespaces as described in the following section.

On Linux, the e820 memory map can be overwritten in the kernel command line with the `memmap` parameter [71]. For example, passing a parameter `memmap=16G!2G` marks 16 GiB of memory starting at offset 2 GiB (physical address  $2^{31}$ ) as persistent memory. This is useful for simulating PM on systems lacking real Optane memory. We use this parameter for file system tests in **Suvi** (Chapter 8).

#### Configuration

Optane regions are configured by the system firmware as part of the boot process. With commands as given below, `ipmctl` can create provisioning goals, which are applied by the firmware after a reboot [2].

| SocketID | ISetID             | Type      | Capacity | Free  | HealthState |

|----------|--------------------|-----------|----------|-------|-------------|

| 0x0000   | 0x6e6dc3d053748888 | AppDirect | 504 GiB  | 0 GiB | Healthy     |

| 0x0001   | 0x70efc3d0f3678888 | AppDirect | 504 GiB  | 0 GiB | Healthy     |

Listing 2.1: Shortened output from `ipmctl show -region` with two interleaved regions with four Optane modules.

```

# Configure all PM in AppDirect mode with interleaving.

ipmctl create -goal PersistentMemoryType=AppDirect

# Configure all PM in AppDirect mode with separate regions per module.

ipmctl create -goal PersistentMemoryType=AppDirectNotInterleaved

```

`ipmctl` also includes commands for reading the state of individual modules and the currently active regions. Listing 2.1 shows example output for reading the currently configured regions.

## 2.1.2 Namespaces

PM namespaces are managed by the Linux kernel and are configured with the `ndctl` tool [3]. A namespace has a size and one of the following modes:

- raw** The namespace appears as a block device with no extra kernel support for atomicity or direct access. This mode is not commonly used.

- sector** The namespace appears as a block device, with the kernel providing atomic block (or sector) writes. We describe the underlying mechanism in Section 2.2.2.

- fsdax** The namespace appears as a block device, with kernel support for direct access (DAX). This mode is required for kernel PM file systems.

- devdax** The namespace appears as a special character device that allows mapping the underlying PM into userspace processes. This mode is usually used for userspace PM file systems. For higher-level userspace PM software, it is usually preferable to obtain a DAX mapping from a PM file system, which simplifies access permissions.

For fsdax and devdax namespaces, the kernel needs to allocate memory management metadata for each 4 KiB physical page frame (`struct page` with a size of 64 bytes [122]). A 128 GiB Optane module therefore requires 2 GiB of space for page metadata. The kernel can either allocate this metadata on PM (reducing the size of the namespace), or on regular main memory.

The Linux kernel can also use a devdax namespace as regular main memory. This can be configured with the `daxctl` tool [3]. In contrast to Optane’s Memory Mode, PM configured this way appears separately from the system’s DRAM as its own NUMA node.

## 2.1.3 Performance Counters

Performance counters are mechanisms that provide insight into how hardware components operate by counting specific events. There are two primary ways to obtain data on Optane operation: counters on the Optane modules and CPU performance counters with Optane events.

### Optane Module Counters

Optane modules provide counters for four events [2].

---

```

---DimmID=0x0001---

MediaReads=0x00000000000000000000000000000006ae129ca2c

MediaWrites=0x00000000000000000000000000000005404670098

ReadRequests=0x0000000000000000000000000000000b33bafaea

WriteRequests=0x000000000000000000000000000000044d83a57c5

TotalMediaReads=0x0000000000000000000000000000000ac3809dcff0

TotalMediaWrites=0x00000000000000000000000000000008b300ca5010

TotalReadRequests=0x000000000000000000000000000000011b2ece5a75

TotalWriteRequests=0x000000000000000000000000000000055a55b71f0b

```

Listing 2.2: Example output from `ipmctl show -performance`, showing on-DIMM performance counters.

**MediaReads/MediaWrites** count the number of 64 byte reads or writes to the media on the module.

**ReadRequests/WriteRequests** count the number of DDR-T read or write transactions (64 bytes).

All events are counted per DIMM since last boot and as lifetime total. These counters can be read with `ipmctl`. Listing 2.2 shows an example output. We analyze output from these counters in Chapter 3.

### CPU Counters for PM

Intel Cascade Lake CPUs (the CPUs we use in this thesis) provide three types of counters that can count events associated with Optane [63, search for “PMM”]. On-core events are counted within a core as part of instruction execution. There are only two on-core PM events that count L3 cache misses from load instructions, which are either fetched from local PM (`MEM_LOAD_RETIRE.LOCAL_PMM`) or from remote PM (`MEM_LOAD_L3_MISS_RETIRE.REMOTE_PMM`).

There are no on-core events for stores to PM. Since x86 CPUs have write-back caches, the CPU core writes only to its L1 cache when executing a store instruction. When a cache line is evicted from the L3 cache and the store reaches PM, there is no direct association with the original store instructions anymore. Similarly, non-temporal stores are handled by write-coalescing buffers.

The second type of counters are off-core response counters [61, Vol. 3B §20.3.8.3.1]. These counters count specific interactions between the on-core L2 cache and the L3 cache or memory. The counted events are selected with a combination of a request type (e.g., data or code read, prefetches) and a supplier (e.g., L3 cache, DRAM, PM). Similar to the on-core counters, the off-core response counters cannot provide information about writes to PM.

Finally, uncore counters provide events from the memory controller [55, 60].<sup>1</sup> The available events include commands issued to PM (e.g., reads and writes) and the state of read and write request queues. From the read and write command counts, the total read and write bandwidth to PM can be calculated: each command transfers 64 bytes.

---

<sup>1</sup>There are also uncore events for components other than the memory controller, but these are unrelated to PM.

## 2.2 Linux File System Support for PM

This thesis deals with PM file systems in the Linux kernel. In this section, we therefore introduce the interfaces that Linux provides for PM access from both kernelspace and userspace.

The upstream Linux kernel [12] supports PM for file systems in two ways: a translation layer for traditional block-based file systems and DAX support in some file systems.

### 2.2.1 Accessing PM from the Kernel

A PM namespace configured as fsdax appears as a block device `/dev/pmemX` in a Linux system.<sup>2</sup> The NVDIMM driver implements the block device access function `pmem_submit_bio`.<sup>3</sup> It supports basic read and write requests, which are fulfilled with a memory copy routine. Writes to PM are performed with non-temporal stores on x86 (via `memcpy_flushcache`). The flags `REQ_PREFLUSH` and `REQ_FUA` trigger a memory fence before or after the operation.

Consequently, file systems using the block I/O layer in Linux (*bio*) do not require modifications to run on top of PM. However, there are two major differences compared to traditional block devices (e.g., those using SCSI or NVMe). First, this thin compatibility layer does not provide any crash consistency guarantees beyond those of the underlying PM. The Block Translation Table, described below, solves this problem by implementing atomicity for larger blocks.

Second, rather than submitting the I/O request to a device and waiting for the result, the compatibility layer performs a synchronous memory copy on the kernel thread that submitted the *bio* request. This has consequences for the performance and energy efficiency of file systems on top of PM, which we discuss in Chapter 5.

File systems that target PM specifically can obtain a pointer to the PM namespace to bypass the *bio* compatibility layer. The kernel provides the function `dax_direct_access` for this purpose. Listing 2.3 shows an example of how to use this function. PM file systems such as NOVA and PMFS (introduced below) obtain a PM pointer once during initialization and then access PM exclusively through that pointer.

### 2.2.2 Block Translation Table (BTT)

With the Block Translation Table (BTT) [72, 117], the kernel provides atomic block access to traditional file systems. These file systems expect atomicity for full block updates, which usually have a size of 512 bytes or 4 KiB. The BTT provides this block atomicity with an indirection layer that maps logical block addresses (LBA) to PM offsets. Every update to a logical block allocates a new data block on PM. A journal ensures that the mapping from the old to the new data block changes atomically.

The BTT is sufficient for using PM via arbitrary file systems, but it cannot provide direct access (DAX) to PM for userspace applications. For this reason, the Linux file system developers implemented DAX support in two traditional file systems, ext4 and XFS [116].

---

<sup>2</sup>For example, an fsdax namespace called `namespace1.0` appears as `/dev/pmem1`.

<sup>3</sup>File `drivers/nvdimm/pmem.c` [12]

```

static int get_pm_pointer(

struct block_device *bdev, /* input: handle to block device */

void **pm_virt_addr,      /* output: virtual address */

long *pm_size             /* output: size in bytes */

)

{

pfn_t pfn;

struct dax_device *dax_dev;

int ret;

/* Obtain handle to a DAX device. */

dax_dev = fs_dax_get_by_bdev(bdev);

if (!dax_dev) { return -EINVAL; }

/* Obtain pointer to DAX area. */

*pm_size = dax_direct_access(dax_dev,

0, LONG_MAX / PAGE_SIZE, /* offset and maximum size */

pm_virt_addr, &pfn        /* output: address and page frame number */

) * PAGE_SIZE;           /* return: number of pages */

if (*pm_size <= 0) { return -EINVAL; }

return 0; /* success */

}

```

Listing 2.3: Example for how a file system can obtain a pointer to PM from a block device handle in Linux 5.15.<sup>4</sup>

### 2.2.3 Ext4 and XFS without BTT

Both ext4 and XFS implement journaling to protect metadata (and optionally file data) updates from crashes. Originally, ext4 implemented *physical journaling* with JBD2 [112]. Physical journaling takes place at the level of on-disk data blocks: Before overwriting a protected block, the file system stores a copy of either the old or the new block in the journal. After a crash, the file system recovers by copying the blocks in the journal to their intended disk locations.

In contrast, XFS employs *logical journaling* [112]. The entries in a logical journal describe individual file system operations. A logical journal is therefore more compact than a physical journal, leading to better runtime performance. However, crash recovery is more complex than with a physical journal, since the file system needs to replay the operations in the journal. With FastCommit [112], ext4 now also performs logical journaling for certain file system operations (e.g., file creation and deletion, appending data to a file).

Both XFS and ext4 protect journal entries with checksums. The journals are therefore already sufficiently protected from partially-written blocks after a crash. Since neither file system relies on atomic block updates without journaling for metadata updates, it is safe to use ext4 and XFS on PM without the Block Translation Table.

Previous works have analyzed the behavior of these file systems on top of traditional block devices under crashes. Mohan et al.’s CrashMonkey [93] found no crash consistency bugs in ext4 and XFS when injecting crashes at persistence points (i.e.,

<sup>4</sup>Note that although the parameters to these functions change over time, the overall process remains the same.

`fsync()` or `sync()`). Jaffer et al. evaluated the behavior of ext4 under certain faults, including incompletely written blocks (“shorn writes”) [65]. They show that ext4 can recover from such faults, although with partial data loss in some cases. Consequently, ext4 and XFS were already well-equipped for handling crashes before the introduction of PM.

### 2.2.4 DAX Support

Without the indirection from the Block Translation Table, ext4 and XFS can hand out memory mappings to file data residing on PM to userspace applications. This feature is called DAX (for direct access) in Linux.

If the underlying device supports DAX and no conflicting file system features are enabled (e.g., file system encryption), a flag in the inode controls whether DAX-mapping a file is allowed. Alternatively, the file system mount option `dax=always` overrides the inode flag and enables DAX for all files [73].

If a userspace process requests a shared memory mapping of a file with the DAX flag set, the file system will always map the file’s PM pages directly. A process can ensure that a mapping is a DAX mapping by calling `mmap` with the `MAP_SYNC` flag [13]. If the file’s DAX flag is not set, `mmap` would then return the `EOPNOTSUPP` error. Since the `MAP_SYNC` flag does not otherwise change the memory mapping, it is not possible to obtain a “traditional” mapping via the page cache for files that support DAX [50].

## 2.3 PM File Systems

PM’s byte-addressability provides new opportunities for file system design. PM file systems no longer need to organize their data in fixed-size blocks as dictated by the underlying block storage device. This allows file systems to offer crash consistency guarantees at a finer level of granularity.

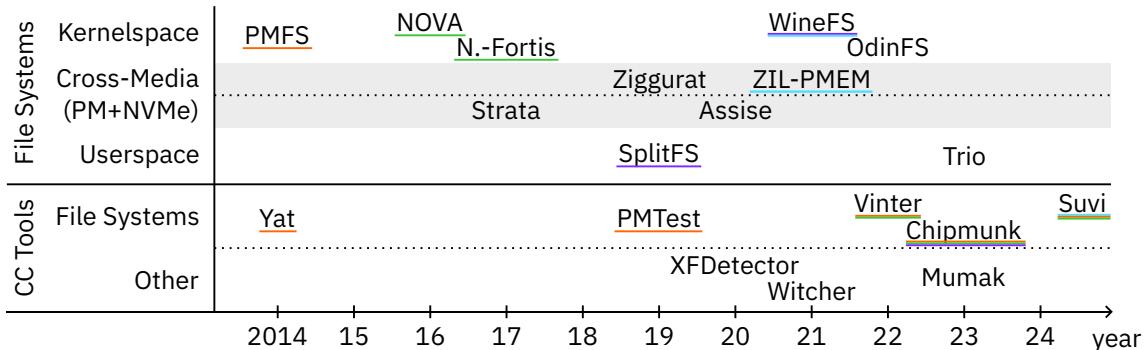

In Table 2.2, we provide an overview of research PM file systems that are relevant for this thesis. We compare the following features:

**Kernelspace/Userspace** Whether the file system runs completely in kernelspace (K) or has a userspace component (U).

**Cross-Media** Whether the file system supports storing data on traditional block storage in addition to PM. This property is relevant for **Suvi**, which can test crash consistency properties of cross-media file systems.

**PM Bandwidth Control** Whether the file system actively limits its bandwidth when writing to PM. We propose mechanisms for PM bandwidth control in this thesis.

**Strong Consistency** We consider a file system to implement strong consistency if all individual file system operations are immediately and atomically persisted to PM. In contrast, traditional file systems implement delayed persistence and only guarantee that data is retained after a later call to `fsync()` [14]. **Suvi** can automatically test strong consistency properties of file systems.

**Artifact Available** Whether an artifact with the file system’s source code is publicly available. We need access to the source code in order to evaluate crash consistency with **Suvi** or to compare PM bandwidth control mechanisms.

We describe ZIL-PMEM in Chapter 3 and give a more detailed overview of the other file systems in the following sections.

| File System       | Year | Kernel/User Space | Cross-Media | PM Bandwidth Control | Strong Consistency | Artifact Available |

|-------------------|------|-------------------|-------------|----------------------|--------------------|--------------------|

| PMFS [41]         | 2014 | K                 | ✗           | ✗                    | ✓                  | ✓                  |

| Aerie [118]       | 2014 | U                 | ✗           | ✗                    | ✗                  | ⚠                  |

| NOVA [125]        | 2016 | K                 | ✗           | ✗                    | ✓                  | ✓                  |

| NOVA-Fortis [126] | 2017 | K                 | ✗           | ✗                    | ✓                  | ✓                  |

| Strata [79]       | 2017 | U                 | ✓           | ✗                    | ⚠                  | ✓                  |

| Ziggurat [132]    | 2019 | K                 | ✓           | ✗                    | (✓)                | ⚠                  |

| SplitFS [67]      | 2019 | U                 | ✗           | ✗                    | ✓                  | ✓                  |

| WineFS [66]       | 2021 | K                 | ✗           | ✗                    | ✓                  | ✓                  |

| ZIL-PMEM [111]    | 2021 | K                 | ✓           | ✓                    | ✓                  | ✓                  |

| SPMFS [128]       | 2021 | U                 | ✗           | ✓                    | (✓)                | ✗                  |

| OdinFS [134]      | 2022 | K                 | ✗           | ✓                    | ✓                  | ✓                  |

| Assise [25]       | 2022 | U                 | ✓           | ✗                    | ✗                  | ✓                  |

| Trio [133]        | 2023 | U                 | ✗           | ✓                    | ⚠                  | ✓                  |

| P2CACHE [84]      | 2023 | K                 | ✓           | ✗                    | ⚠                  | ✓                  |

| SlotFS [131]      | 2023 | U                 | ✗           | ✗                    | ⚠                  | ✓                  |

Table 2.2: Overview of research PM file systems with a comparison of features relevant for this thesis. ⚠ denotes problems with the file system implementation’s crash consistency guarantees that are obvious without detailed analysis.

### 2.3.1 PMFS, WineFS, and OdinFS

PMFS [41] was the first file system designed for persistent memory in current x86 systems and implemented as a Linux kernel file system. Its data layout is optimized for byte-addressable PM. In particular, its allocator manages data in blocks according to the processor’s page sizes (4 KiB, 2 MiB, 1 GiB) to support DAX mappings. Metadata is updated in-place with atomic instructions if possible. Otherwise, PMFS implements fine-granular journaling with cache-line-sized log entries (64 bytes). Writes to file data pages are protected with a copy-on-write mechanism.

Since PMFS was designed before hardware with support for PM was available, the authors had to make assumptions about the interaction of atomic instructions with PM [41, §3.2]. Besides 8-byte atomic updates, PMFS also uses `cmpxchg16b` for atomic 16-byte updates, and optionally transactional memory for atomic 64-byte updates. Real hardware ended up guaranteeing atomicity only for 8-byte updates. In our analysis in Chapter 10, we can therefore observe crash consistency bugs in two places where PMFS uses `cmpxchg16b` to update multiple fields in the inode:

- File size (8 bytes) and modification timestamps ( $2 \times 4$  bytes)

- Root pointer and height of the B-Tree referencing the file data (both 8 bytes)

PMFS is used as the basis of multiple later research file systems. These file systems inherit PMFS's usage of `cmpxchg16b`. In the following, we introduce two such file systems, WineFS and OdinFS.

### WineFS

WineFS [66] improves the performance of memory-mapped files in *aged* file systems. Repeated allocation and deletion over time leads to a fragmented PM area. Since PM is byte-addressable and has a (mostly) uniform access latency, such fragmentation usually does not have an effect on access performance. However, fragmentation is relevant for memory-mapped files. If sufficiently large parts of the data on PM are contiguous and aligned, the file system can employ hugepages when memory mapping the file to a userspace process.

The authors of WineFS show that previous PM file systems suffer from reduced access bandwidth once the file system cannot use hugepages anymore due to fragmentation. They introduce an alignment-aware allocator that avoids fragmentation over time. The authors evaluate the throughput as well as application benchmarks on aged file systems. WineFS outperforms the other PM file systems in these benchmarks.

We analyze WineFS with **Suvi** in Chapter 10 and show that some but not all crash consistency issues of PMFS are fixed in WineFS.

### OdinFS

As we show in Section 2.1, Optane PM suffers from low bandwidth with parallel accesses, as well as remote NUMA accesses. OdinFS [134] extends PMFS with a delegation mechanism for accessing PM to mitigate these problems. For each NUMA node, OdinFS runs a fixed number of delegation threads. Every read or write access to PM is delegated to a thread on the same NUMA node as the data. OdinFS therefore both limits the amount of threads that access PM in parallel, and prevents remote NUMA access to PM.<sup>5</sup>

In Chapter 5, we discuss alternative approaches for mitigating performance loss from parallel PM accesses. We show that although OdinFS's delegation threads ensure a constantly high PM bandwidth, they come with a high CPU cost, decreasing the overall efficiency of the file system.

OdinFS additionally stripes data across all available NUMA nodes. It thereby spreads the load evenly across the PM modules and allows higher parallelism, including for large accesses from a single thread.

Since OdinFS inherits all metadata management from PMFS, we expect identical crash consistency behavior. We therefore do not analyze OdinFS separately with **Suvi**.

## 2.3.2 Aerie

Aerie [118] was the first modern userspace PM file system. It introduces the concept of a user-mode library file system with direct PM access in combination with a

<sup>5</sup>Note that although OdinFS might increase the number of remote DRAM accesses, these do not hurt performance as much as remote PM accesses.

trusted file system service running partially in the kernel. The library file system has direct read-only access to metadata and file data, as well as a write area for new file data. To write a file, the library file system first writes the file data to PM, then requests a metadata update from the trusted file system service. Aerie can delay metadata updates, so file operations with outstanding metadata may be lost in the event of a crash.

Aerie was implemented for x86 Linux systems, but predates support for PM in processors and the Linux kernel. In contrast to PMFS, its artifact [1] was never updated with support for real PM hardware and Linux DAX interfaces. It is therefore not usable for performance comparisons or crash consistency testing.

Concepts from Aerie can be found in most later userspace file systems. We describe some of them in the following sections.

### 2.3.3 NOVA, NOVA-Fortis, and Ziggurat

NOVA [125] is a log-structured file system for PM. Its primary goals are high performance and strong consistency. NOVA is implemented as a Linux kernel file system.

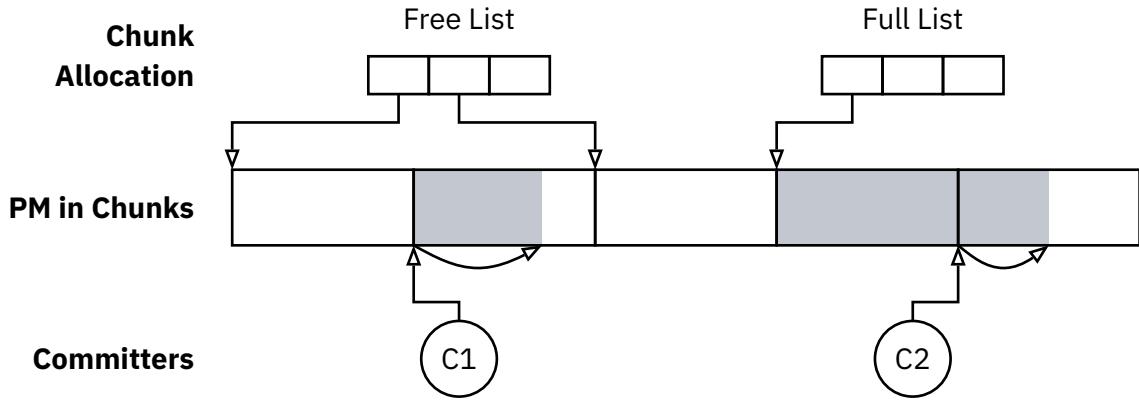

NOVA’s data layout is optimized for concurrent access by maintaining private data structures for each CPU, including inode tables, journals, and free lists. Traditional log-structured file systems maintain a global log containing all file system data, allowing mostly linear write access to the storage media [106]. PM enables efficient random access with small access sizes, allowing NOVA to maintain a private log for each inode. This enables concurrent log operations on different inodes. For operations involving multiple inodes, NOVA uses journaling.

To speed up file access, NOVA maintains volatile runtime data in DRAM, including the file radix tree, the directory entry tree, and free lists. These data structures do not require persistence and are always rebuilt during mounting.

NOVA does not use logging for all inode data. If possible, inode fields are updated directly with 8-byte atomic store instructions (e.g., timestamps and log pointers). File data is updated with copy-on-write, by writing the data to a new data page and updating data pointers through the log.

#### NOVA-Fortis

NOVA-Fortis [126] extends NOVA with features for protecting the file system from software and hardware faults. It implements consistent whole file system snapshots, including for files that are DAX-mmapped during the snapshot operation.

NOVA-Fortis can handle PM media errors. All file system metadata and file data in NOVA-Fortis is protected with a checksum. Using ECC, the PM hardware can transparently correct certain media errors and detect others. The CPU communicates detected errors via *machine check exceptions* (MCE). In case of an MCE or a checksum mismatch, NOVA-Fortis recovers metadata from a replica and file data using RAID-4 parity. However, it cannot protect file data while it is DAX-mmapped and defers responsibility for data protection to the userspace application.

NOVA and NOVA-Fortis were introduced before Optane PM was available. The authors continued work on the artifact [6], updating it to Linux 5.1 and ensuring compatibility with commercial Optane modules. In this thesis, we use NOVA as a baseline for a PM file system without managed concurrency for write accesses in Chapter 5. We then evaluate our mechanisms for limiting concurrency with NOVA. NOVA and NOVA-Fortis are also part of our crash consistency analysis in Chapter 10.

### Ziggurat

Ziggurat [132] extends NOVA with support for cross-device storage. In contrast to other cross-device file systems that use PM as a cache for a disk file system (e.g., ZIL-PMEM or P2CACHE, both described below), Ziggurat prefers to place data in PM.

A *synchronicity predictor* decides whether new file data is placed on PM or a lower tier. The predictor bases its decision on previous `fsync()` calls, the size of the new data, and the size of previous accesses. Data placed in lower tiers is written asynchronously using a page cache in DRAM. Ziggurat therefore does not implement strong consistency for all writes. However, applications can request strong consistency by opening a file with the `O_DIRECT` flag.

Data placement in Ziggurat is not fixed. A migration thread can move hot data from disk to PM and cold data from PM to disk. In particular, background migration is helpful for small writes which are placed in PM at first, then later coalesced into a large, sequential write to disk.

We were unable to analyze the crash consistency of Ziggurat with **Suvi**. Although Ziggurat’s source code is published, we found that it is not in a usable state.

### 2.3.4 Strata and Assise

Strata [79] is the first modern PM-based cross-media file system. A userspace component *LibFS* handles writes by logging directly to a private PM area mapped into the process. The kernel component *KernelFS* then creates a digest of the userspace log. This digest can then be placed either in PM or in lower storage tiers. Strata also supports data migration between storage tiers based on access patterns.

**Assise** [25] is a distributed file system that builds on Strata. Assise uses Strata’s design for node-local storage and extends it with a cache coherence layer *CC-NVM* for replication. Using RDMA, Assise replicates the write log to different nodes, allowing the file system to survive node failures.

LeBlanc et al. attempted to analyze Strata and Assise with Chipmunk, but learned that neither artifact supports crash recovery [81, §4.1]. We therefore do not analyze these file systems with **Suvi**.

### 2.3.5 SPMFS

SPMFS [128] is a userspace file system featuring PM bandwidth management. It implements most file system operations in its userspace component, with a kernel module handling some “complex” metadata operations as well as free space management. Notably, the authors do not discuss security considerations in case multiple processes share a file system.

SPMFS implements an I/O thread pool to limit parallel write accesses to PM. Applications may not write to PM directly and insert their requests into a queue instead. Based on a predictor, SPMFS then either handles the request synchronously or asynchronously.<sup>6</sup> Synchronous requests are immediately processed by an I/O thread, with the application waiting for completion. Asynchronous requests are inserted into a write cache in DRAM. Similar to the kernel’s page cache, SPMFS can serve reads from the write cache and will write back data if `fsync()` is called. SPMFS therefore implements delayed persistence by default, but applications can request strong consistency with the `O_SYNC` flag.

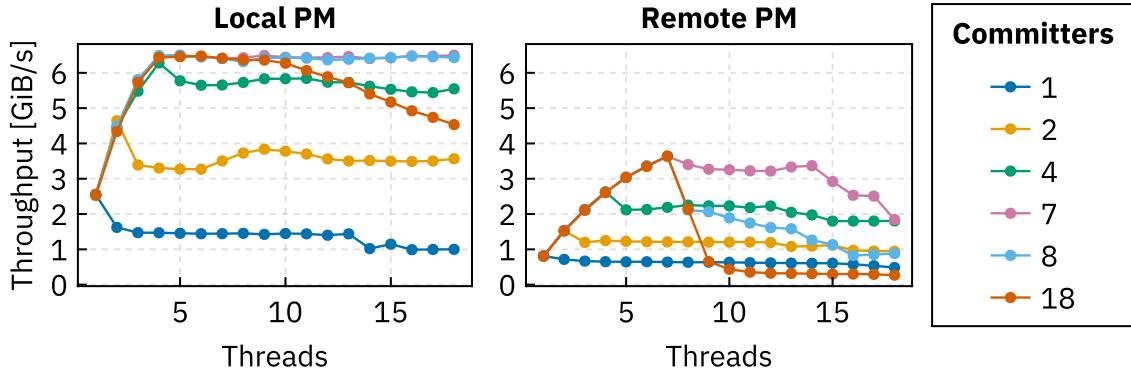

The authors evaluate SPMFS’s PM bandwidth management by comparing the parallel synchronous write throughput with and without the I/O thread pool [128, Fig. 6]. They show that the total bandwidth increases with the number of I/O threads and does not decrease as much as the amount of threads increases.

In contrast to our analysis of similar mechanisms in Chapter 5, the authors of SPMFS do not analyze the CPU efficiency of their approach. Since they did not publish any source code, we cannot directly compare SPMFS to our approach.

### 2.3.6 Trio

Trio [133] is an architecture for secure userspace file systems. Its key feature is an in-kernel access controller that mediates PM access to a userspace library file system. If multiple processes want to access a shared file, the kernel controller ensures exclusive write access. Once a process releases its write access to a file, a verifier checks that the file’s metadata is consistent.

This design allows different file system implementations that agree on a core metadata format as enforced by the verifier. Trio’s authors implement three library file systems: a POSIX-compatible file system ArckFS, and two customized file systems KVFS and FPFS with a key-value interface and with optimizations for deep directory structures.

To limit parallel accesses to PM, ArckFS implements the delegation mechanism from OdinFS [134]. For bulk data accesses, the library file system sends write requests to in-kernel delegation threads. To reduce overhead, it performs small PM accesses directly from userspace. Since the underlying mechanism is the same as in OdinFS, we do not evaluate ArckFS in Chapter 5.

We attempted to analyze the crash consistency of ArckFS with Suvi, but found a number of issues with the published artifact:

- ArckFS requires large amounts of PM and DRAM for statically-allocated metadata. Reducing the size of these allocations is not trivial because of implicit alignment requirements.

- We ran into multiple bugs when accessing ArckFS from multiple sequential processes like in shell scripts. Such a scenario does not come up in the authors’ evaluation since they only evaluated single long-running benchmark programs.

---

<sup>6</sup>The predictor appears very similar to the one originally introduced in Ziggurat [132], which we describe above.

- Support for the POSIX API is incomplete. For example, ArckFS requires custom functions for accessing directories instead of `opendir()` and `readdir()`.

- ArckFS always formats the file system on mount. We removed this unconditional formatting, but were unable to successfully remount an initialized (and properly unmounted) file system.

These problems prevented us from successfully running **Suvi**'s test cases, making a crash consistency analysis impossible.

### 2.3.7 P2CACHE

P2CACHE [84] is a PM-based cache designed to improve the performance of traditional kernel file systems such as ext4. It sits between the VFS layer and the file system and records all file system operations in a persistent write-ahead log. Additionally, it caches all writes in DRAM to serve reads, similar to the page cache.

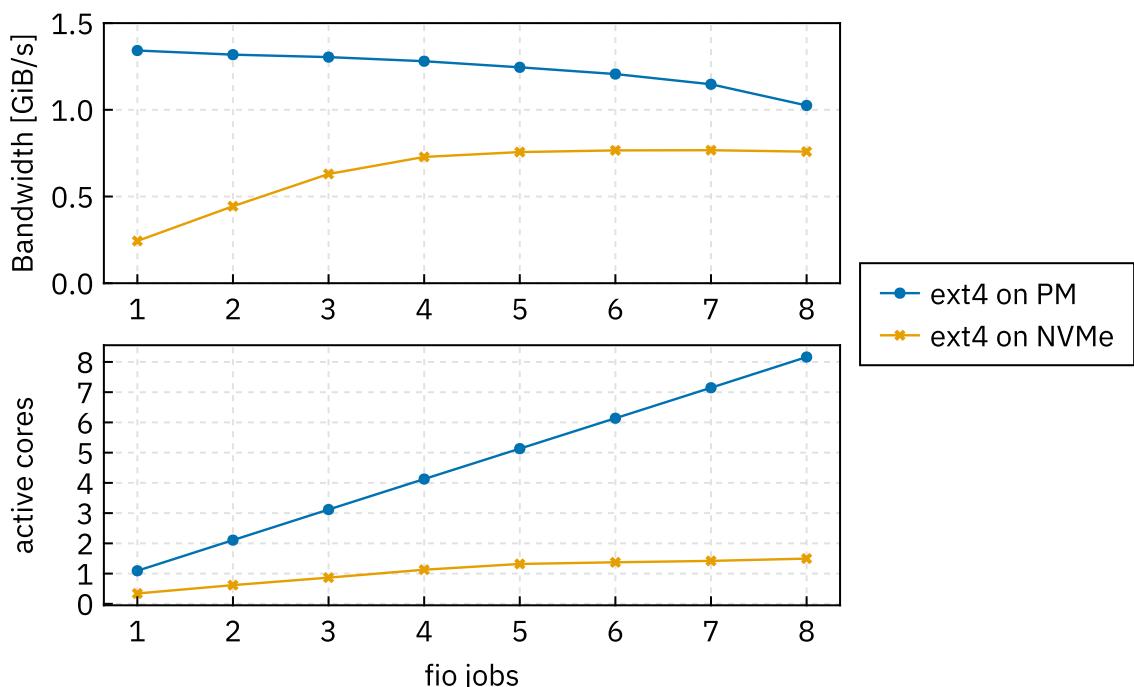

The authors evaluate P2CACHE on top of ext4, comparing with ext4, XFS, and NOVA. They show that P2CACHE is significantly faster than the traditional Linux file systems ext4 and XFS, both on an NVMe SSD and on PM. It also surpasses NOVA in some benchmarks.

P2CACHE does not implement any PM bandwidth control. The authors show results of a scalability benchmark [84, Fig. 10], but their evaluation system is not set up in a way where Optane contention becomes an issue.<sup>7</sup>

The authors designed P2CACHE to support strong consistency. They developed a custom crash consistency checker to check for crash consistency bugs [84, §4.1]. Unfortunately, these consistency checks were not part of the published artifacts and therefore not reproduced in the artifact evaluation [84, §A.3].

We attempted to evaluate P2CACHE with **Suvi**, but found that the published artifact does not support retaining any data and always formats the PM with an empty file system on mount.

### 2.3.8 SlotFS

SlotFS [131] is a userspace log-structured file system. SlotFS improves upon prior log-structured file systems such as NOVA by implementing *scattered logging*. Since random access to PM is cheap, there is no need to keep a contiguous log. According to the authors, scattered logging completely eliminates overhead from garbage collection of log entries, as individual freed log entries can immediately be reused.

We attempted to evaluate the crash consistency of SlotFS with **Suvi**, but found a number of issues with the published artifact that prevented an analysis:

- The required Linux kernel is unclear. According to the artifact description [131, §A.2.3], SlotFS requires Linux kernel version 5.1.0 with patches for SplitFS [67] and Hodor [52]. Hodor is a system for isolating components in a userspace process using memory protection keys. SlotFS uses Hodor to isolate its library file system from untrusted processes that access the file system. However, the Hodor patches are only available for kernel version 4.15 or 5.4. We found that the published artifacts do not actually use Hodor in any way, so we attempted evaluation without Hodor.

---

<sup>7</sup>The evaluation system has four Optane DIMMs attached to a 12-core CPU without hyperthreading.

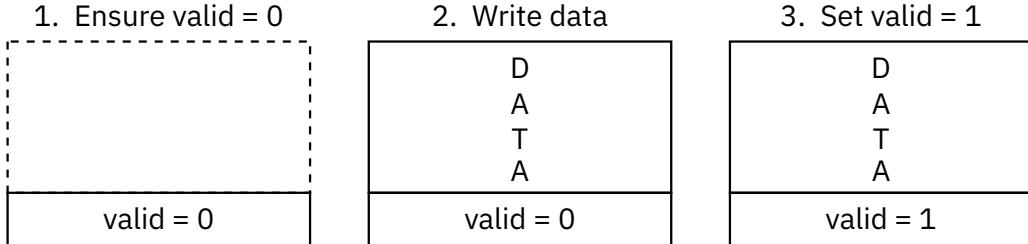

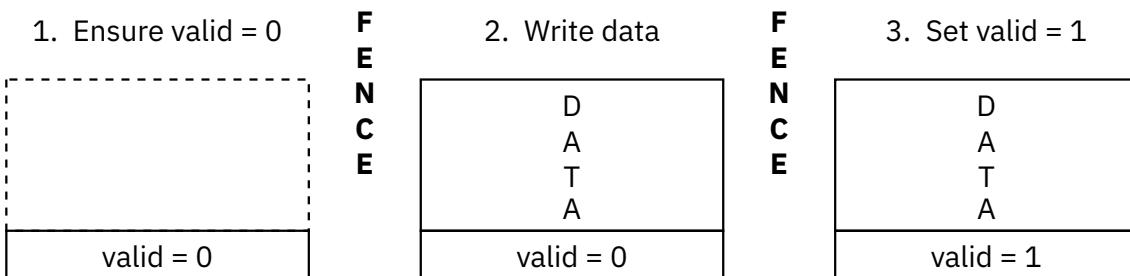

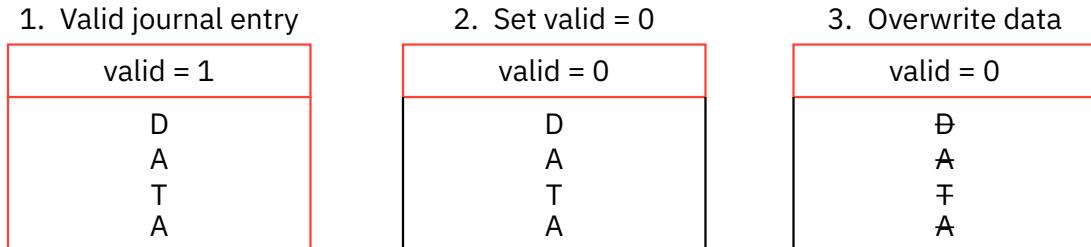

Figure 2.2: Steps when writing a journal entry. For crash consistency to hold, these steps must not be reordered.

- The recovery code is disabled and the SlotFS initialization code always formats the file system. We were able to remove the forced formatting.

- A routine performing cache flushes for a memory range with an optional memory fence was disabled. This routine is used for some metadata updates (e.g., in inodes and directory entries). We re-enabled the routine by removing an early return statement.

- SlotFS expects a PM area with size 48 GiB by default, which is too large for an analysis with crash images. It cannot automatically scale its metadata allocation to smaller PM areas.

- We observed crashes when accessing the file system from multiple consecutive processes, such as in shell scripts. SlotFS sets up a volatile shared memory area that is retained across consecutive processes. Some retained state appears to cause crashes.

Even with multiple fixes to the issues above, we were unable to run basic file system tests on SlotFS without crashes. An analysis of crash consistency properties is therefore not possible.

## 2.4 Crash Consistency

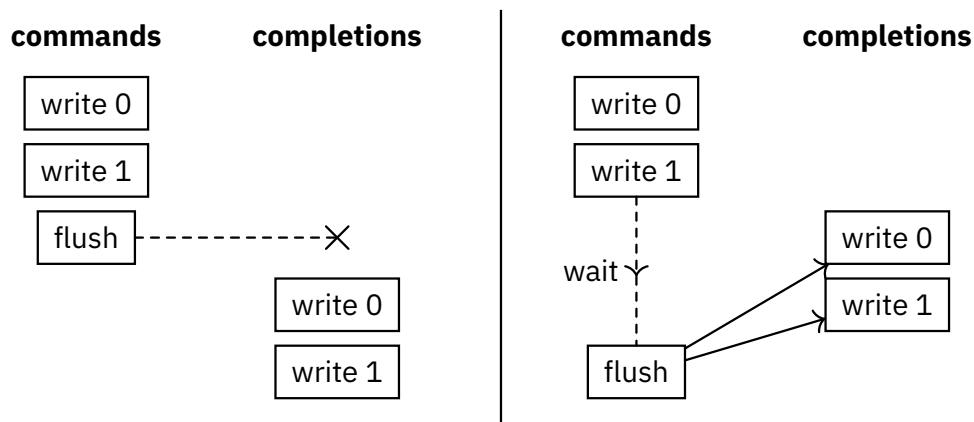

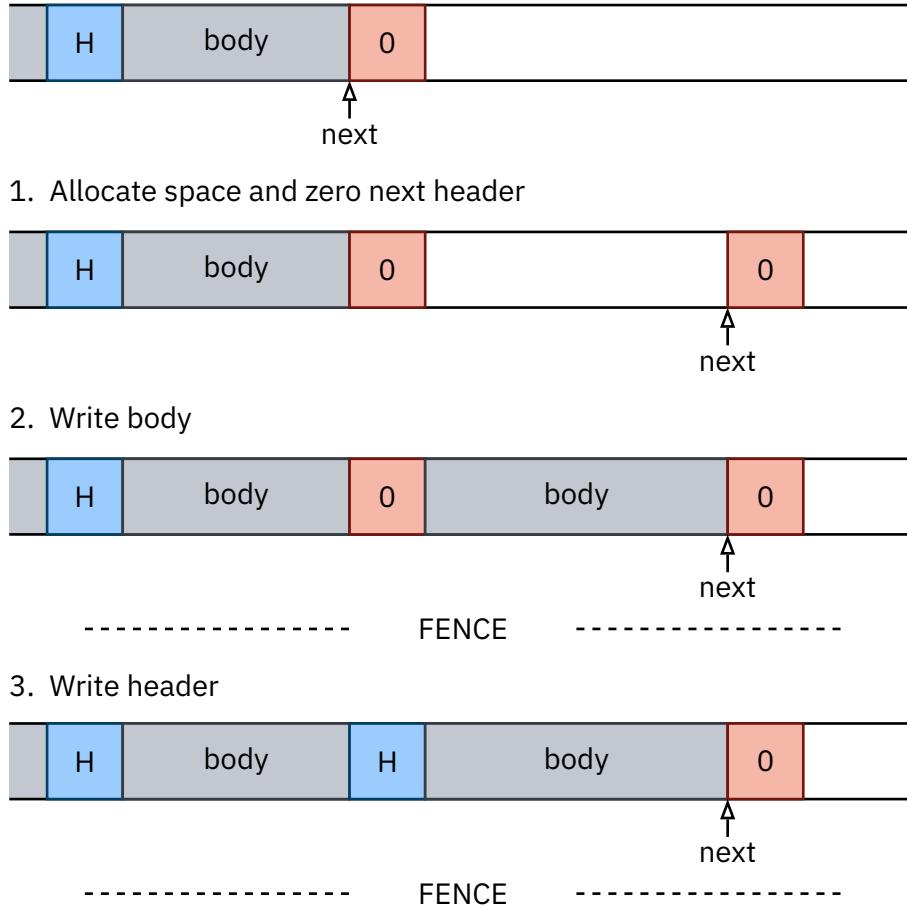

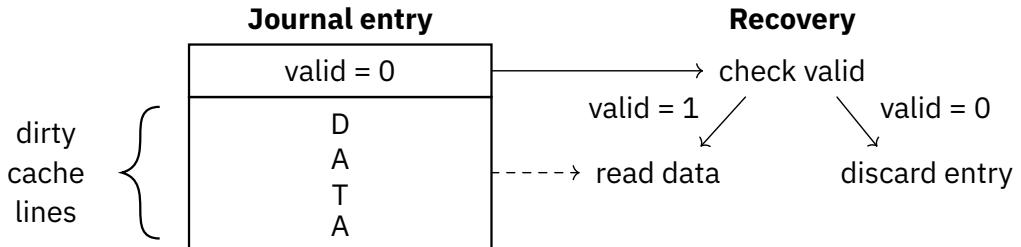

Crash-consistent software needs to control the order in which its writes reach non-volatile memory. As motivating example, consider a journal as commonly used by file systems or databases to perform complex updates atomically. For this example, each journal entry contains arbitrary data, followed by a valid flag. Writing a journal entry works in three steps, pictured in Figure 2.2:

1. Ensure that the valid flag is not set, for example by zero-initializing the journal memory.

2. Write the data. There is no requirement for atomic writes so that an arbitrary amount of data may be written.