# **Physical Security of Emerging AI Hardware Accelerators: From Vulnerability to Countermeasures**

Zur Erlangung des akademischen Grades eines

Doktors der Ingenieurwissenschaften

von der KIT-Fakultät für Informatik

des Karlsruher Instituts für Technologie (KIT)

genehmigte

Dissertation

von

**Brojogopal Sapui**

aus Kolkata, India

---

---

Tag der mündlichen Prüfung: 16. January 2026

1. Referent: Prof. Dr. Mehdi B. Tahoori

Karlsruhe Institute für Technology (KIT)

2. Referent: Prof. Dr. Amir Moradi

TU Darmstadt

---

## Acknowledgement

Reflecting on this journey, I feel incredibly fortunate to have been surrounded by extraordinary individuals whose support, kindness, and patience made this dissertation possible.

First and foremost, I would like to express my deepest gratitude to my advisor, Prof. Dr. Mehdi Tahoori. I could not have asked for a better mentor throughout my PhD. His scientific insight, thoughtful feedback, and unwavering support-especially during the more difficult phases of this work-have shaped both this dissertation and my development as a researcher.

My sincere thanks go to all my colleagues at the Chair of Dependable Nano Computing (CDNC). I am especially grateful to our secretary, Ms. Iris Schröder-Piepka, for her tireless efforts in keeping everything running smoothly in the background. I would like to thank Dr.-Ing. Jonas Krautter and Dr.-Ing. Christopher Münch for their generous help, insightful discussions, and willingness to answer my questions, even while they were already transitioning to positions outside KIT.

Most importantly, I would like to express my heartfelt gratitude to my family. I am profoundly thankful to my parents, whose unconditional love, sacrifices, and belief in me have been a constant source of strength. I am equally grateful to my elder sister and my dear nieces, whose affection and encouragement brought warmth and joy across the distance. I also owe special thanks to my dear friends Priyanjana Pal and Surendra Hemaram, who were like family to me during this journey and whose friendship, conversations, and humour helped me through many difficult days. I am likewise grateful for the friendship and support of my wonderful colleagues and friends already mentioned above-including Atousa Jafari, Vincent Meyers, Sina Bakhtavari Mamaghani, Seyedehmaryam Ghasemi, Shanmukha Mangadahalli Siddaramu, Ali Nezhadi Khelejani, Gürol Saglam, Maha Shatta, Zhe Zhang, Simon Pankner, Tara Gheshlaghi, Aradhana Dube, Mahboobe Sadeghipourrudsari and Mahta Mayahinia-who each, in their own way, made this path lighter and more enjoyable.

---

Hiermit erkläre ich an Eides statt, dass ich die von mir vorgelegte Arbeit selbstständig verfasst habe, dass ich die verwendeten Quellen, Internet-Quellen und Hilfsmittel vollständig angegeben haben und dass ich die Stellen der Arbeit – einschließlich Tabellen, Karten und Abbildungen – die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

Karlsruhe, 21. November 2025

Brogopal sapui

# Abstract

The widespread deployment of Artificial Intelligence (AI) at the edge has driven a paradigm shift toward domain-specific hardware accelerators. Emerging architectures-ranging from Analog Compute-in-Memory (CiM) and Non-Volatile Memory (NVM)-centric processors to Neuromorphic Computing and Hyperdimensional Computing (HDC)-promise orders-of-magnitude improvements in energy efficiency and latency. However, while these substrates are often used for their intrinsic robustness to noise and stochastic process variations, this dissertation demonstrates that such robustness does *not* translate into resilience against targeted physical attacks. This work systematically explores the physical security gap in post-Von Neumann computing, establishing that the very physical properties enabling efficiency often introduce novel, exploitable attack surfaces.

To address these challenges, this thesis develops a set of cross-layer analysis frameworks and countermeasures, spanning device physics, circuit simulation, and real-hardware validation. First, the research investigates Analog Compute-in-Memory (CiM) based on ReRAM and STT-MRAM. By developing a physics-aware simulation framework, it is shown that analog non-idealities-such as device-to-device variability and random telegraph noise-manifest as data-dependent leakage signatures. These signatures allow adversaries to recover fixed weights using correlation-based and profiling attacks, enabling the extraction of proprietary neural network models.

Second, the thesis uncovers a critical vulnerability in processor-centric NVM architectures. Through real-hardware experiments on STT-MRAM, a novel class of persistent fault attacks is demonstrated. By targeting the specific magnetic commit window of MRAM writes with nanosecond-scale voltage glitches, an attacker can induce stable, non-volatile bit corruptions in stored cryptographic keys. This persistence mechanism collapses the data complexity required for differential fault analysis (DFA) by orders of magnitude, enabling full AES key recovery with fewer than 20 ciphertext pairs.

Third, the security of Neuromorphic Computing is analyzed through the introduction of *FlexSpy*, the first design-time security framework for thin-film transistor (TFT)-based Spiking Neural Networks (SNNs). The analysis reveals a unique *quasi-DC* leakage mechanism inherent to event-driven processing on flexible substrates. Despite the absence of internal triggers, an attacker can exploit this leakage to infer input classes and recover layer-wise spiking activity with high fidelity. Lightweight circuit-level countermeasures are proposed that suppress this leakage by up to 70% with minimal power overhead.

Finally, the thesis presents a comprehensive security evaluation of FPGA-based Hyperdimensional Computing (HDC). It exposes a “robustness mismatch,” where HDC’s algorithmic error tolerance masks severe physical vulnerabilities. The work demonstrates successful Intellectual Property (IP) theft via deep-learning-assisted side-channel analysis and remote, internal sensing attacks using on-chip time-to-digital converters (TDCs). Furthermore, a targeted fault injection methodology (*HyFault*) is developed, capable of inducing precise misclassifications. In response, effective defenses-including dynamic masking and hypervector randomization-are introduced to restore security.

Collectively, these contributions provide a foundational understanding of the physical security risks in emerging AI hardware, offering actionable design guidelines to ensure that the next generation of efficient edge accelerators is secure by design.

# Zusammenfassung

Die weit verbreitete Nutzung von Künstlicher Intelligenz (KI) am Randbereich (*Edge*) hat einen Paradigmenwechsel hin zu domänenspezifischen Hardware-Beschleunigern ausgelöst. Neuartige Architekturen - von Analog *Compute-in-Memory* (CiM) und nichtflüchtigkeitsspeicherzentrierten (*Non-Volatile Memory*, NVM) Prozessoren bis hin zu Neuromorpher Datenverarbeitung (NC) und Hyperdimensional Computing (HDC) - versprechen Größenordnungen an Verbesserungen hinsichtlich Energieeffizienz und Latenz. Obwohl diese Substrate häufig aufgrund ihrer intrinsischen Robustheit gegenüber Rauschen und stochastischen Prozessvariationen eingesetzt werden, zeigt diese Dissertation, dass eine solche Robustheit *keinesfalls* zu einer Widerstandsfähigkeit gegenüber gezielten physikalischen Angriffen führt. Die Arbeit untersucht systematisch die Sicherheitslücke in post-von-Neumann-Systemen und zeigt, dass gerade die physikalischen Eigenschaften, die Effizienz ermöglichen, neuartige und ausnutzbare Angriffsflächen eröffnen.

Um diese Herausforderungen anzugehen, entwickelt diese Dissertation eine Reihe von schichtübergreifenden Analyseframeworks und Gegenmaßnahmen, die von der Bauelementphysik über die Schaltungssimulation bis hin zur Validierung auf realer Hardware reichen. Zunächst untersucht die Arbeit Analog-*Compute-in-Memory* (CiM) auf Basis von ReRAM und STT-MRAM. Durch die Entwicklung eines physikbewussten Simulationsframeworks wird gezeigt, dass analoge Nichtidealitäten - wie Bauelement-zu-Bauelement-Variabilität und *Random Telegraph Noise* - datenabhängige Leckagesignaturen erzeugen. Diese Signaturen ermöglichen es Angreifern, stationäre Gewichte mittels korrelationsbasierter und profilierender Seitenkanalangriffe zurückzugewinnen und somit proprietäre neuronale Netzwerkmodelle auszulesen.

Zweitens deckt die Dissertation eine kritische Schwachstelle in prozessorzentrierten NVM-Architekturen auf. Durch Realhardware-Experimente an STT-MRAM wird eine neuartige Klasse von *persistenten Fehlerangriffen* gezeigt. Durch das präzise Anvisieren des magnetischen Commit-Fensters des MRAM-Schreibvorgangs mit Spannungsglitches im Nanosekundenbereich kann ein Angreifer stabile, nichtflüchtige Bitfehler in gespeicherten kryptografischen Schlüsseln erzeugen. Dieser Persistenzmechanismus reduziert die Datenkomplexität für differentielle Fehleranalyse (DFA) um mehrere Größenordnungen und ermöglicht eine vollständige AES-Schlüsselrekonstruktion mit weniger als 20 Chiffretextpaaren.

Drittens wird die Sicherheit der Neuromorphen Datenverarbeitung anhand der Einführung von *FlexSpy* analysiert, dem ersten Entwurfszeit-Sicherheitsframework für dünnschichttransistorbasierte (TFT) Spiking Neural Networks (SNNs). Die Analyse zeigt einen einzigartigen *quasi-DC*-Leckagemechanismus, der inhärent mit ereignisgetriebener Verarbeitung auf flexiblen Substraten verbunden ist. Trotz des Fehlens interner Trigger kann ein Angreifer diese Leckage ausnutzen, um Eingangsklassen abzuleiten und schichtweise Spiking-Aktivität mit hoher Genauigkeit zu rekonstruieren. Leichte Schaltungs-Gegenmaßnahmen werden vorgeschlagen, die diese Leckage um bis zu 70% reduzieren - bei minimalem zusätzlichen Energieaufwand.

Abschließend präsentiert die Dissertation eine umfassende Sicherheitsanalyse hardwarebeschleunigter Hyperdimensional Computing (HDC) Implementierungen auf FPGAs. Die Arbeit zeigt eine "*Robustheitsdiskrepanz*", bei der die algorithmische Fehlertoleranz von HDC schwerwiegende physikalische Verwundbarkeiten verdeckt. Die Ergebnisse demonstrieren erfolgreichen Diebstahl geistigen Eigentums durch Deep-Learning-unterstützte Seitenkanalanalyse sowie durch entfernte, interne Messangriffe mittels *On-Chip Time-to-Digital Converters* (TDCs). Daraüber hinaus wird eine gezielte Fehlerinjektionsmethodik (*HyFault*) entwickelt, die präzise Fehlklassifikationen hervorrufen kann. Als Reaktion werden wirksame Gegenmaßnahmen - einschließlich dynamischem Masking und Hypervektor-Randomisierung - vorgestellt, die die Sicherheit maßgeblich wiederherstellen.

Insgesamt liefern diese Beiträge ein grundlegendes Verständnis der physikalischen Sicherheitsrisiken in aufkommenden KI-Hardwarebeschleunigern und bieten konkrete Entwurfsrichtlinien, um sicherzustellen, dass die nächste Generation energieeffizienter Edge-Beschleuniger *von Grund auf sicher* gestaltet wird.

# Contents

|                                                                                              |     |

|----------------------------------------------------------------------------------------------|-----|

| <b>Abstract</b> . . . . .                                                                    | iii |

| <b>Zusammenfassung</b> . . . . .                                                             | v   |

| <b>List of Figures</b> . . . . .                                                             | 1   |

| <b>List of Tables</b> . . . . .                                                              | 7   |

| <b>Acronyms</b> . . . . .                                                                    | 9   |

| <br>                                                                                         |     |

| <b>I. Preliminaries</b> . . . . .                                                            | 13  |

| <b>1. Introduction and Motivation</b> . . . . .                                              | 15  |

| 1.1. Motivation . . . . .                                                                    | 15  |

| 1.1.1. The Crisis: The Memory Wall and the Energy Efficiency Gap . . . . .                   | 15  |

| 1.1.2. The Paradigm Shift: Emerging Hardware Accelerators . . . . .                          | 16  |

| 1.1.3. The Security Gap: Physical Vulnerabilities in the Post-Digital Era . . . . .          | 17  |

| 1.2. Problem Statement . . . . .                                                             | 18  |

| 1.2.1. The Failure of Digital Leakage Models in Analog Computing . . . . .                   | 18  |

| 1.2.2. The Threat of Persistence: Non-Volatility as an Attack Vector . . . . .               | 18  |

| 1.2.3. Security Blind-Spots in Emerging Neuromorphic Hardware . . . . .                      | 19  |

| 1.2.4. The "Robustness Mismatch" in Hyperdimensional Computing . . . . .                     | 19  |

| 1.3. Research Objectives and Contributions . . . . .                                         | 19  |

| 1.3.1. RQ1: Vulnerabilities of Emerging NVM-based In-memory Computing (Analog) . . . . .     | 20  |

| 1.3.2. RQ2: Persistent Faults in Processor-Centric NVM Architectures (MRAM) . . . . .        | 21  |

| 1.3.3. RQ3: Security of Emerging Spiking Neuromorphic Computing (Flexible Edge-AI) . . . . . | 21  |

| 1.3.4. RQ4: Vulnerability of FPGA-based (HDC) . . . . .                                      | 21  |

| 1.4. Methodology: Cross-Level Co-Optimization . . . . .                                      | 22  |

| 1.5. Summary . . . . .                                                                       | 22  |

| <br>                                                                                         |     |

| <b>2. Background</b> . . . . .                                                               | 23  |

| 2.1. Introduction . . . . .                                                                  | 23  |

| 2.2. Accelerator Paradigms and Physical Foundations . . . . .                                | 24  |

| 2.2.1. Reference Platform: The Sub-10 nm SRAM Fabric . . . . .                               | 24  |

| 2.2.2. Memory-Centric Accelerators: Analog Compute-in-Memory (CiM) . . . . .                 | 25  |

| 2.2.3. Hyperdimensional Computing (HDC) on FPGA/ASIC . . . . .                               | 28  |

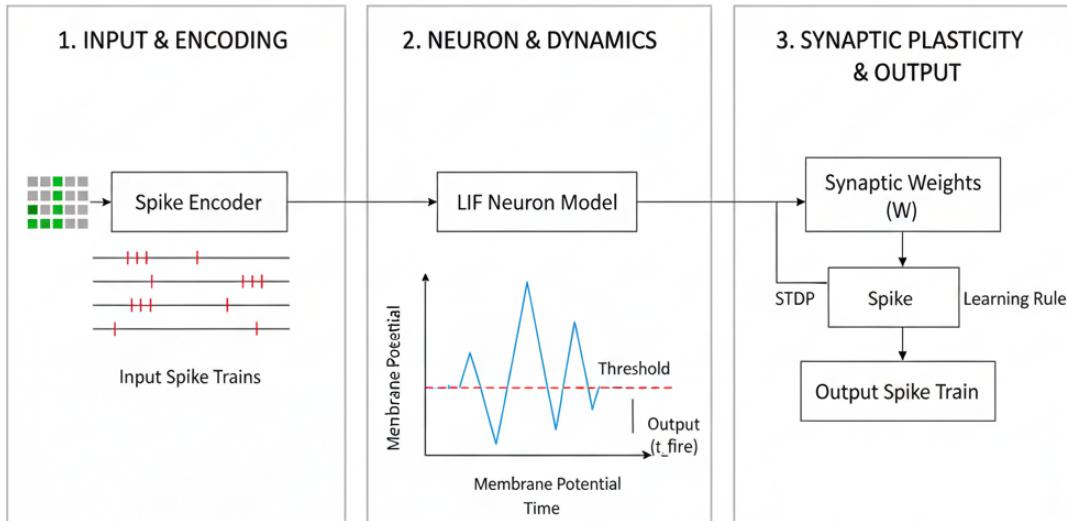

| 2.2.4. Spiking Neuromorphic Computing (NC) on Emerging Technology . . . . .                  | 29  |

| 2.3. Adversary Models and Attack Taxonomy . . . . .                                          | 29  |

| 2.3.1. Formal Models of Physical Attack Vectors . . . . .                                    | 30  |

| 2.4. Identified Research Gaps and Thesis Positioning . . . . .                               | 33  |

| 2.5. Summary . . . . .                                                                       | 34  |

|                                                                                                       |           |

|-------------------------------------------------------------------------------------------------------|-----------|

| <b>II. Contributions</b>                                                                              | <b>35</b> |

| <b>3. Vulnerabilities of Emerging Non-Volatile Memory (NVM)-based In-memory Computing: Simulation</b> | <b>37</b> |

| 3.1. Introduction                                                                                     | 37        |

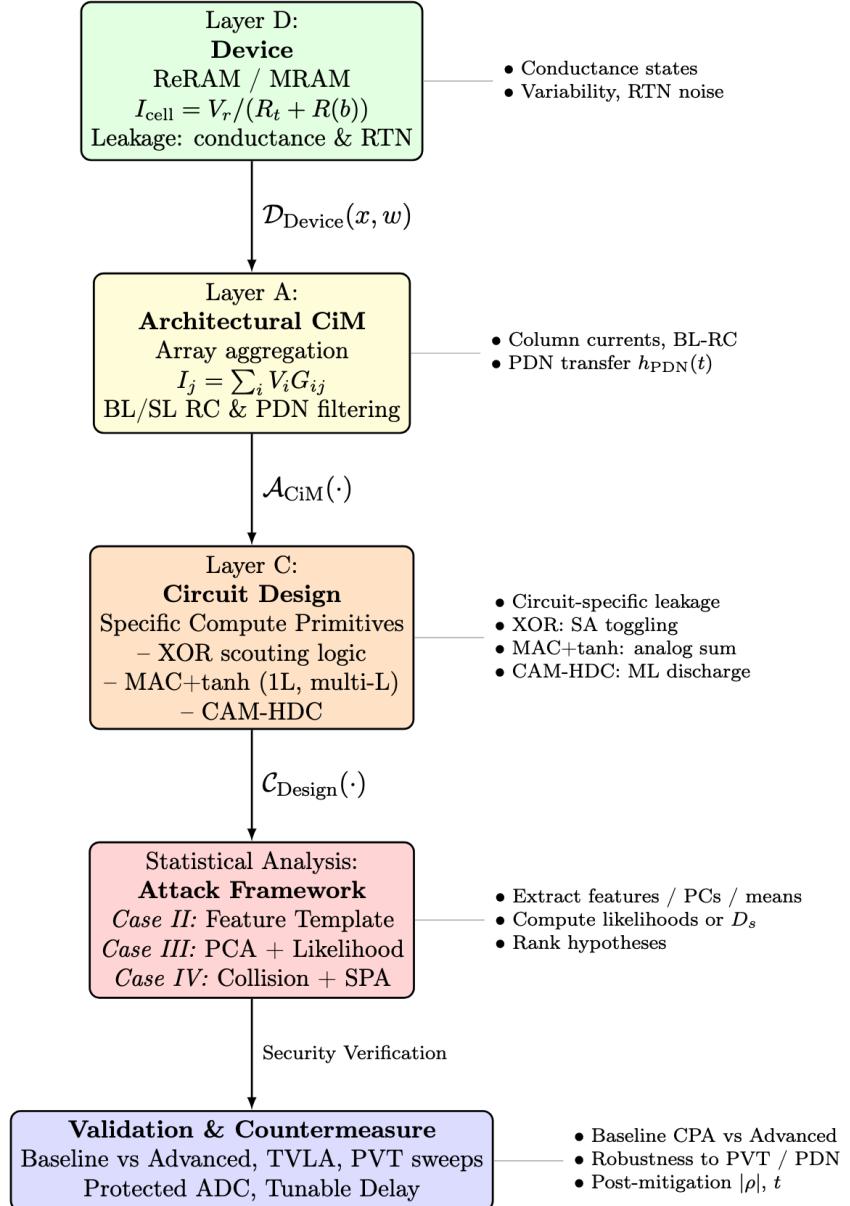

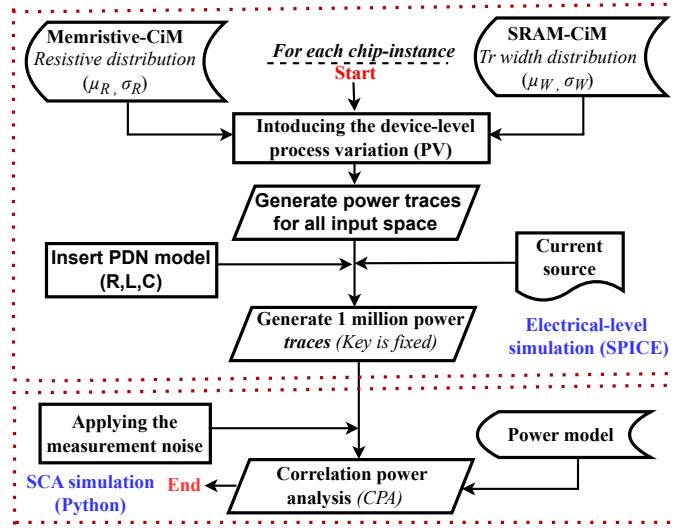

| 3.2. Physical Origins of Analog Leakage: From Device Physics to Circuit Dynamics                      | 38        |

| 3.2.1. Layer D - Device-Level Leakage Models                                                          | 40        |

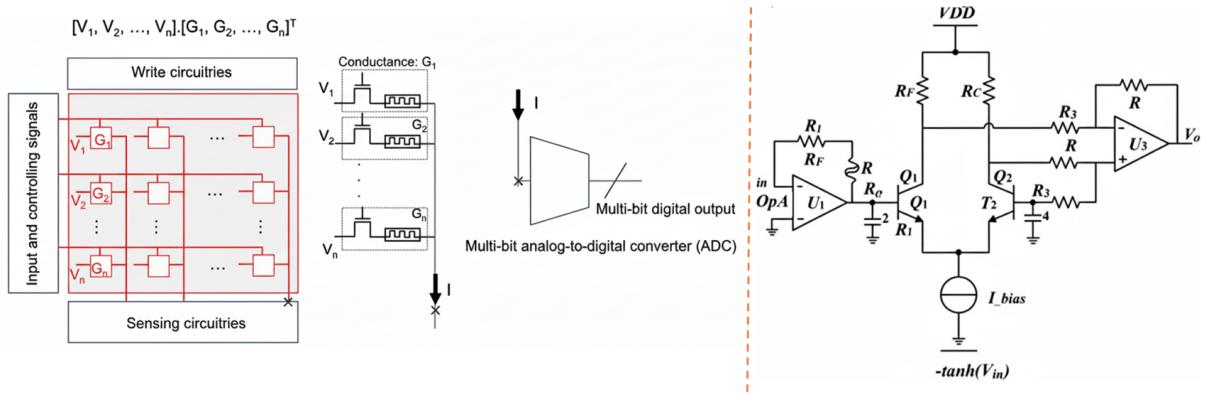

| 3.3. Layer C - Circuit Design-Specific Leakage Realizations                                           | 41        |

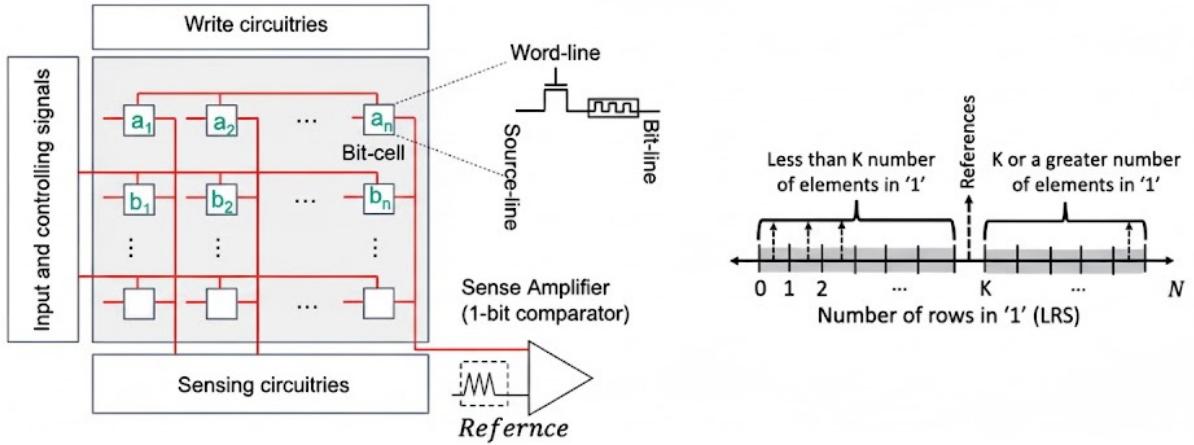

| 3.3.1. Case I - Scouting-Logic XOR                                                                    | 42        |

| 3.3.2. Case II - Multiply-Accumulate (MAC) + tanh activation Layer                                    | 48        |

| 3.3.3. Case III - Multi-Layer MAC + tanh activation Network                                           | 51        |

| 3.3.4. Case IV - Content Addressable Memory (CAM)-Based Hyperdimensional Computing (HDC)              | 54        |

| 3.3.5. Common Pre-Processing and Evaluation Protocol (used in Cases II-IV)                            | 57        |

| 3.4. Summary                                                                                          | 58        |

| <b>4. Vulnerabilities of Emerging NVM-Backed Processor-centric Computing: FPGA Emulation</b>          | <b>59</b> |

| 4.1. Introduction                                                                                     | 59        |

| 4.2. From Analog CiM Variability to Digital Persistent Faults                                         | 60        |

| 4.2.1. Why MRAM's Physics Matters for Security                                                        | 60        |

| 4.2.2. The Intuition: Persistence $\Rightarrow$ Constancy $\Rightarrow$ Low Samples                   | 60        |

| 4.3. Threat Model                                                                                     | 60        |

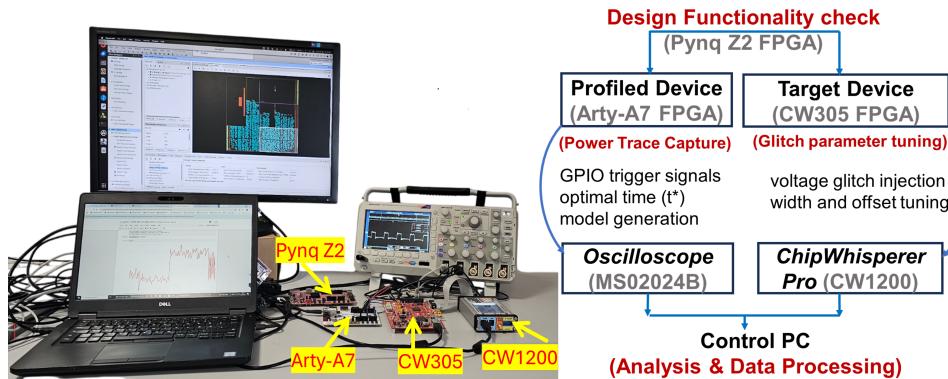

| 4.4. Experimental Platform and Instrumentation                                                        | 61        |

| 4.4.1. Board-Level Setup                                                                              | 61        |

| 4.4.2. AES Integration and Key-Schedule Handling                                                      | 62        |

| 4.5. Attack Methodology: Targeting the MRAM Commit Window                                             | 62        |

| 4.5.1. Timing Model and Parameter Sweep                                                               | 62        |

| 4.5.2. Persistence Definition and Morphology                                                          | 62        |

| 4.6. Cryptanalysis Under Persistent Faults                                                            | 62        |

| 4.6.1. Notation and Fault Model                                                                       | 62        |

| 4.6.2. Case A: Persistent Fault in $K_{10}$ (Direct Leakage)                                          | 63        |

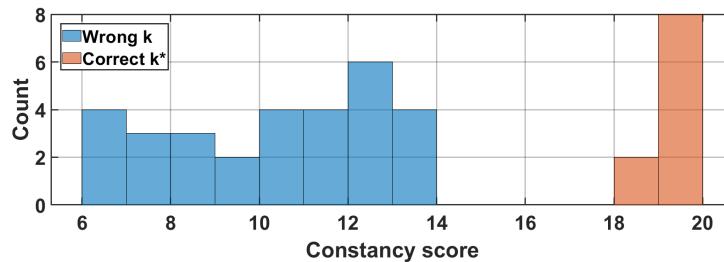

| 4.6.3. Case B: Persistent Fault in $K_9$ (Constancy Test)                                             | 64        |

| 4.6.4. From Per-Byte to Full-Key: Required Reliability                                                | 64        |

| 4.6.5. Robustness: SPFA Scoring                                                                       | 64        |

| 4.7. Results and Analysis                                                                             | 65        |

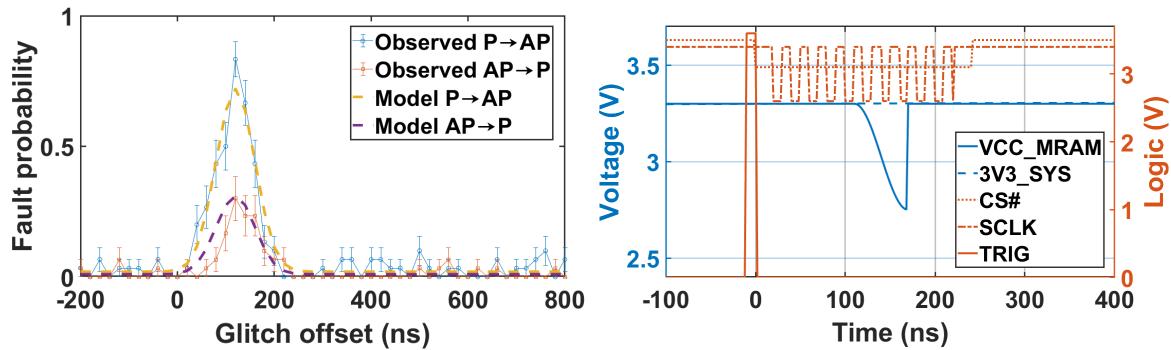

| 4.7.1. Selective Glitching Without Board Destabilization                                              | 65        |

| 4.7.2. Glitch Window and Asymmetry                                                                    | 65        |

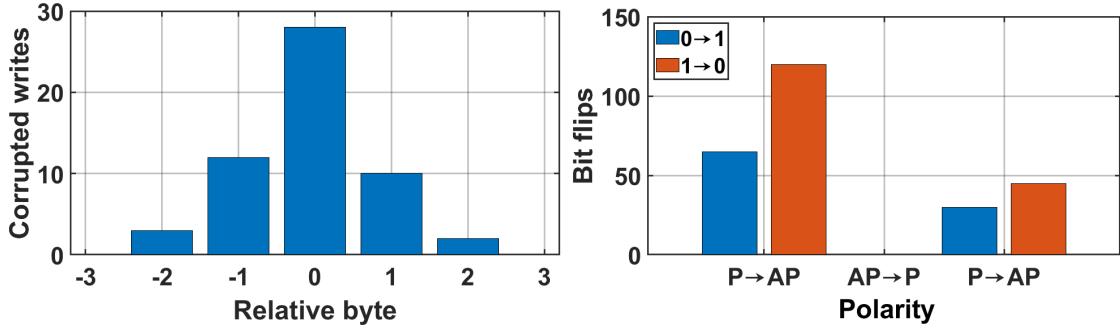

| 4.7.3. Persistence and Morphology                                                                     | 66        |

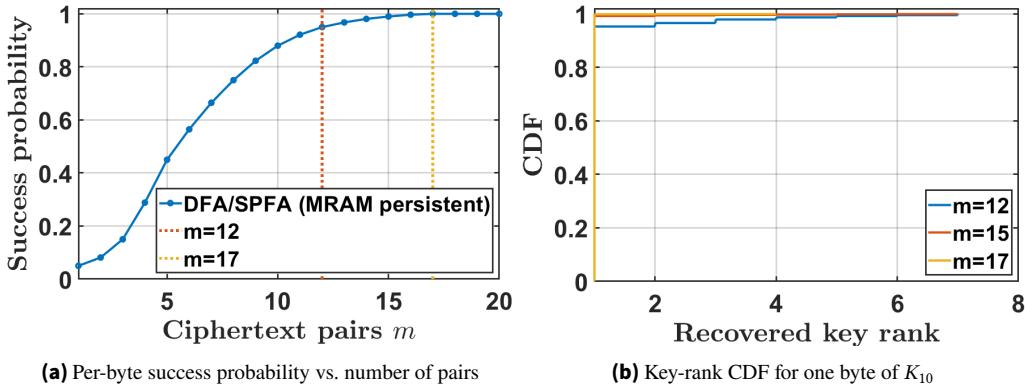

| 4.7.4. Key-Recovery Effectiveness                                                                     | 66        |

| 4.7.5. Why 12–17 on Hardware (vs. 2–3 in the Ideal Model)                                             | 66        |

| 4.7.6. Comparison to Volatile-Memory DFA                                                              | 67        |

| 4.8. Ablations and Sensitivity                                                                        | 67        |

| 4.8.1. Targeting $K_{10}$ vs. $K_9$                                                                   | 67        |

| 4.8.2. Effect of Multi-Byte Bursts                                                                    | 67        |

| 4.8.3. Plaintext Selection                                                                            | 67        |

| 4.9. Countermeasures Tailored to MRAM                                                                 | 67        |

| 4.9.1. PUF-Bound Sealing of Key Slots                                                                 | 68        |

| 4.9.2. Randomized Commit Timing (Write Dither)                                                        | 68        |

| 4.9.3. Dual-Slot + ECC/CRC + Write-Verify                                                             | 68        |

| 4.9.4. Rail Monitoring and Write Gating                                                               | 68        |

| 4.9.5. Architectural Surface Reduction                                                                | 68        |

|                                                                                                                                     |           |

|-------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 4.10. Discussion and Outlook . . . . .                                                                                              | 68        |

| 4.10.1. Why This Work is Effective . . . . .                                                                                        | 68        |

| 4.10.2. Beyond This Chapter: Invertible Randomized Wrappers . . . . .                                                               | 69        |

| 4.11. Practical Deployment Guidance . . . . .                                                                                       | 69        |

| 4.11.1. Implications for Emerging AI Accelerators . . . . .                                                                         | 69        |

| 4.12. Summary . . . . .                                                                                                             | 70        |

| <b>5. Vulnerability of Flexible Edge-AI-based Neuromorphic Computing: Simulation . . . . .</b>                                      | <b>71</b> |

| 5.1. Introduction . . . . .                                                                                                         | 71        |

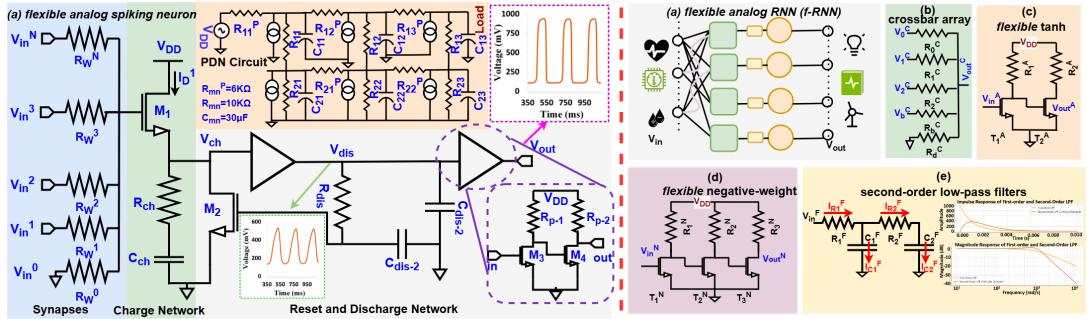

| 5.2. Hardware Design . . . . .                                                                                                      | 72        |

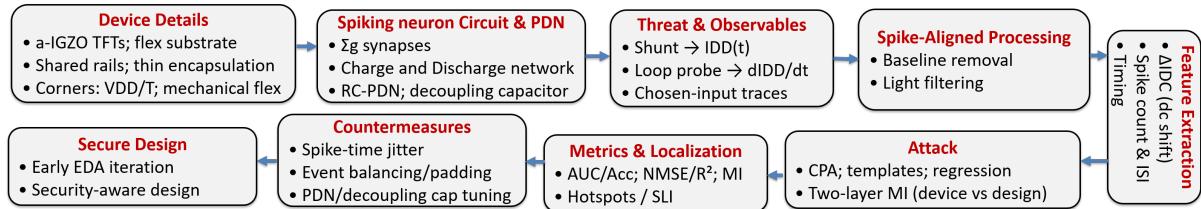

| 5.3. The FlexSpy Framework Methodology . . . . .                                                                                    | 72        |

| 5.3.1. Threat Model and Leakage Observables . . . . .                                                                               | 73        |

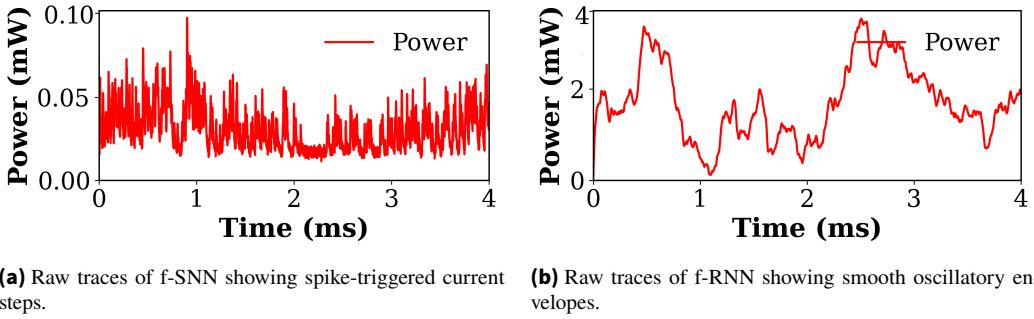

| 5.3.2. Substrate-Aware Leakage Model for f-SNNs . . . . .                                                                           | 73        |

| 5.3.3. Trace Synthesis and Spike-Aligned Feature Extraction . . . . .                                                               | 74        |

| 5.3.4. Calibrated Attack Suite . . . . .                                                                                            | 74        |

| 5.3.5. Leakage Quantification and Localization . . . . .                                                                            | 75        |

| 5.4. Experimental Evaluation and Results . . . . .                                                                                  | 75        |

| 5.4.1. Experimental Setup . . . . .                                                                                                 | 75        |

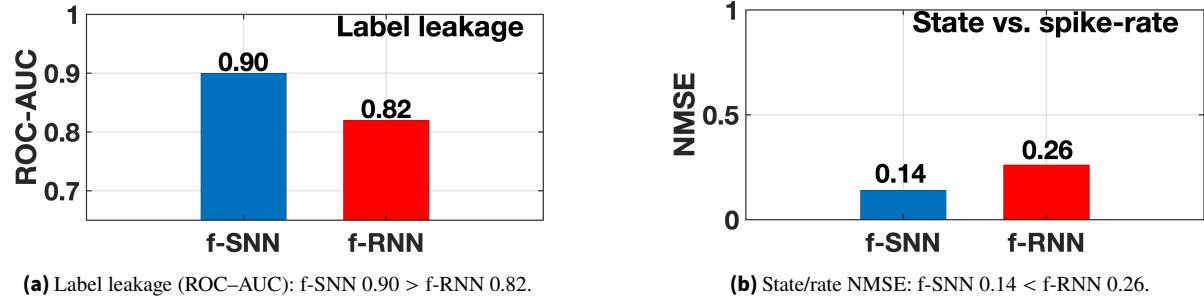

| 5.4.2. Label Inference from Power Leakage . . . . .                                                                                 | 76        |

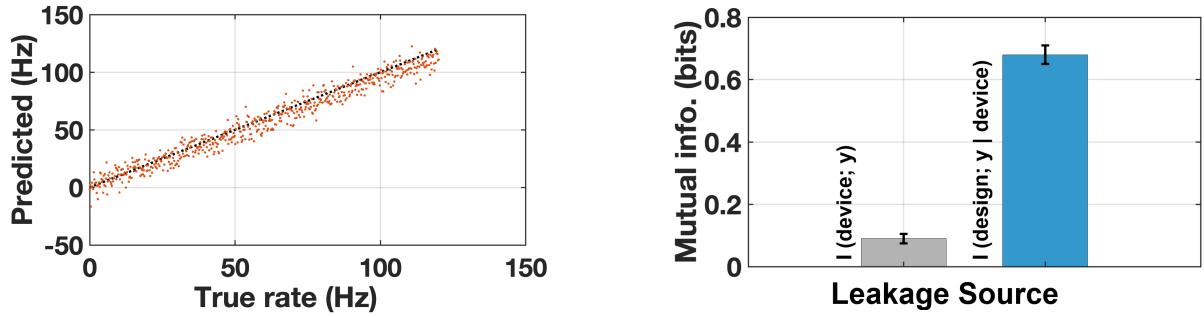

| 5.4.3. Spike-Rate Recovery and Mutual Information . . . . .                                                                         | 77        |

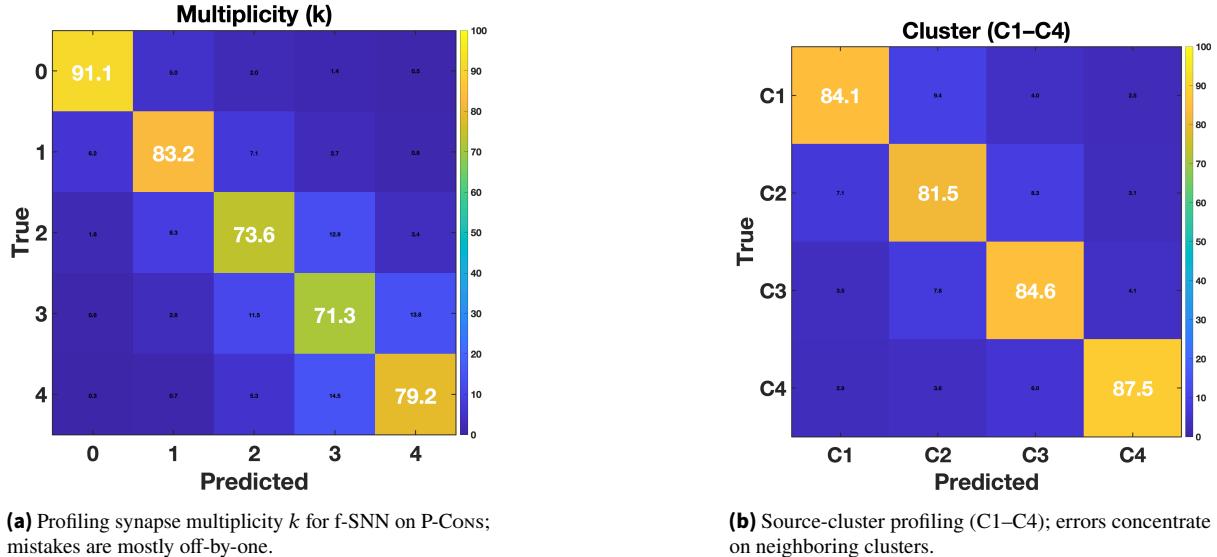

| 5.4.4. Structural Profiling from Power Traces . . . . .                                                                             | 78        |

| 5.4.5. Comparative Study: f-SNN vs. f-RNN . . . . .                                                                                 | 79        |

| 5.5. Countermeasures and Mitigation . . . . .                                                                                       | 79        |

| 5.5.1. Countermeasure 1: Spike-Time Randomization (Jitter) . . . . .                                                                | 80        |

| 5.5.2. Countermeasure 2: Event Balancing (Dummy Conductance) . . . . .                                                              | 80        |

| 5.5.3. Evaluation of Defenses . . . . .                                                                                             | 80        |

| 5.6. Summary . . . . .                                                                                                              | 81        |

| <b>6. Vulnerability of Edge-AI-based Hyperdimensional Computing: FPGA Emulation . . . . .</b>                                       | <b>83</b> |

| 6.1. Introduction . . . . .                                                                                                         | 83        |

| 6.2. Theoretical Framework: Hyperdimensional Computing and Hardware Vulnerability . . . . .                                         | 83        |

| 6.2.1. The Algebra of Hypervectors and Hardware Mapping . . . . .                                                                   | 83        |

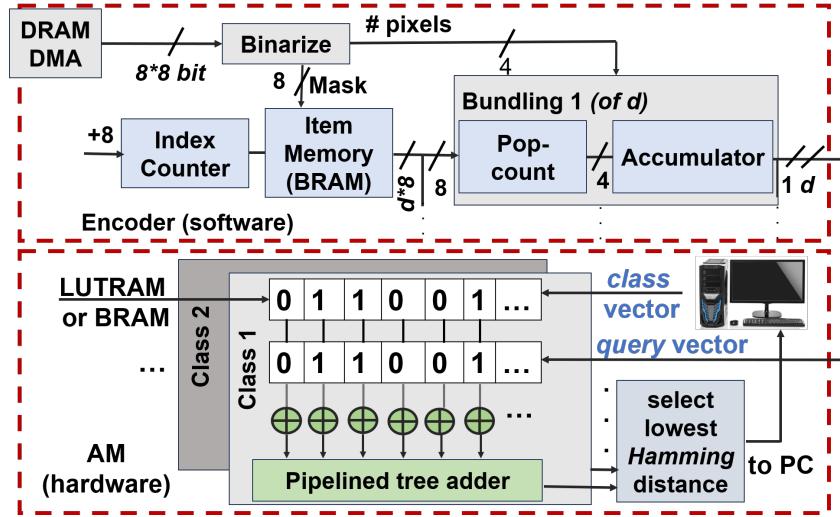

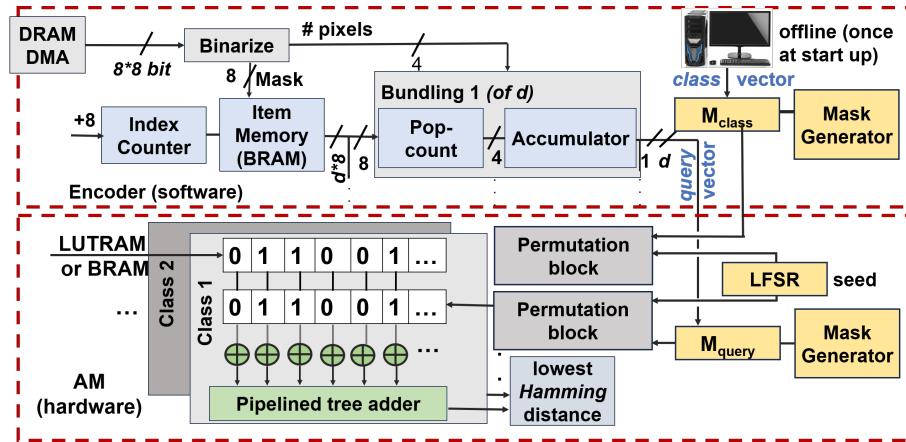

| 6.2.2. Hyperdimensional Computing Hardware . . . . .                                                                                | 84        |

| 6.2.3. The Threat Landscape: Physical Access and Adversarial Capability . . . . .                                                   | 85        |

| 6.3. Deep Learning-Assisted Power Attack . . . . .                                                                                  | 85        |

| 6.3.1. The Dimensionality Limitations in Classical SCA . . . . .                                                                    | 85        |

| 6.3.2. Attack Methodology . . . . .                                                                                                 | 86        |

| 6.3.3. Empirical Evaluation and Transferability . . . . .                                                                           | 87        |

| 6.3.4. Evaluation of Side-Channel Attack Effectiveness . . . . .                                                                    | 89        |

| 6.4. Dynamic workload scheduling and Internal Sensing Side-Channel Analysis (SCA) Attack: Collision-Based Timing Analysis . . . . . | 92        |

| 6.4.1. Attack Overview and Threat Model . . . . .                                                                                   | 92        |

| 6.4.2. On-Chip Sensing with Time-to-Digital Converters . . . . .                                                                    | 93        |

| 6.4.3. Collision Analysis in High-Dimensional HDC . . . . .                                                                         | 93        |

| 6.4.4. Implicit Triggering via Staircase Profiling . . . . .                                                                        | 94        |

| 6.4.5. Two-Stage Internal SCA Methodology . . . . .                                                                                 | 95        |

| 6.4.6. Experimental Setup . . . . .                                                                                                 | 96        |

| 6.4.7. Vulnerability Assessment of Unprotected HDC Designs . . . . .                                                                | 97        |

| 6.4.8. Randomization-Based Countermeasure . . . . .                                                                                 | 99        |

| 6.4.9. Comparison with Other Attacks on HDC . . . . .                                                                               | 100       |

| 6.5. Active Integrity Attacks: Targeted Voltage-Level Fault Injection (HyFault) . . . . .                                           | 100       |

| 6.5.1. Threat Model . . . . .                                                                                                       | 100       |

|                                                                |            |

|----------------------------------------------------------------|------------|

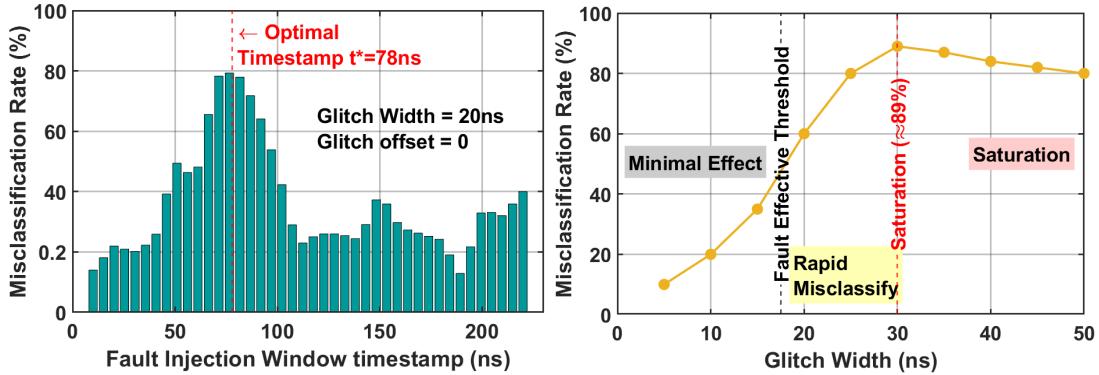

| 6.5.2. Profiling and Sensitivity Analysis . . . . .            | 101        |

| 6.5.3. Fault Injection Attack Methodology . . . . .            | 102        |

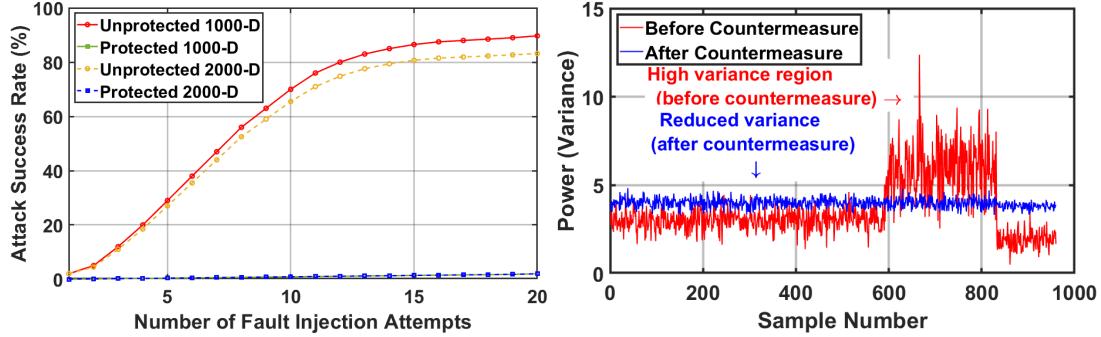

| 6.5.4. Countermeasures for Voltage Fault Injection . . . . .   | 104        |

| 6.5.5. Evaluation and Results . . . . .                        | 106        |

| 6.5.6. Integrated Countermeasures and the Robustness . . . . . | 109        |

| 6.5.7. Summary . . . . .                                       | 110        |

| <b>7. Conclusion and Outlook . . . . .</b>                     | <b>111</b> |

| <b>III. Appendix</b>                                           | <b>115</b> |

| <b>Bibliography . . . . .</b>                                  | <b>121</b> |

# List of Figures

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

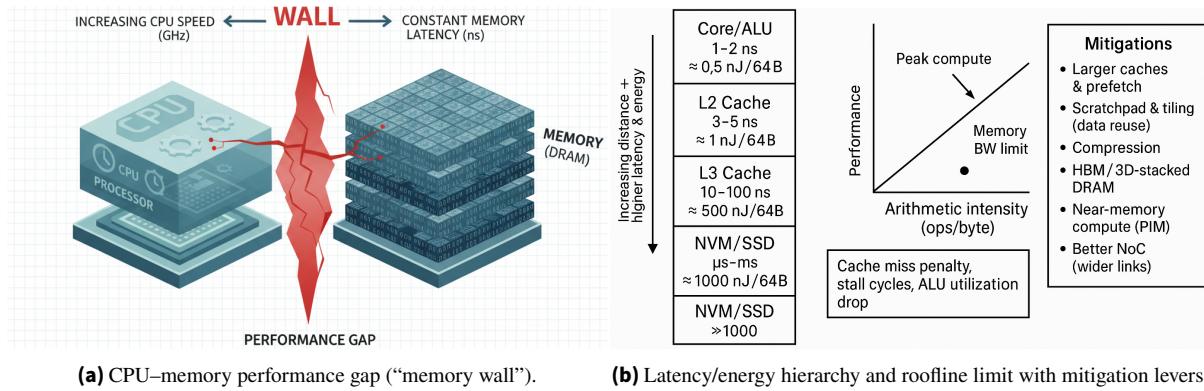

| 1.1. Visualization of the memory wall: Central Processing Unit (CPU) performance increases rapidly while Dynamic Random-Access Memory (DRAM) latency stays nearly constant, creating a fundamental bottleneck. The accompanying memory hierarchy and roofline model highlight latency/energy scaling across cache levels and motivate mitigation techniques such as data reuse, compression, near-memory compute, and wider Network-on-Chip (NoC). . . . .                                                                                                                                   | 16 |

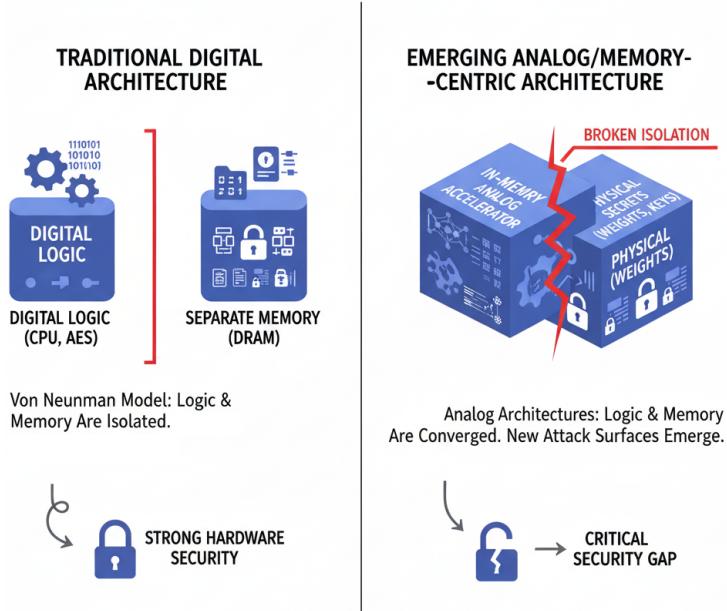

| 1.2. Traditional digital architectures maintain strict physical separation between logic (e.g., CPUs, Advanced Encryption Standard (AES) engines) and memory (e.g., DRAM), providing strong isolation and mature hardware-security guarantees. Emerging analog and memory-centric accelerators collapse this boundary by co-locating computation and storage. While this improves efficiency, it breaks architectural isolation and introduces new attack surfaces that expose physical weights, internal states, and stored secrets to leakage and fault-injection vulnerabilities. . . . . | 17 |

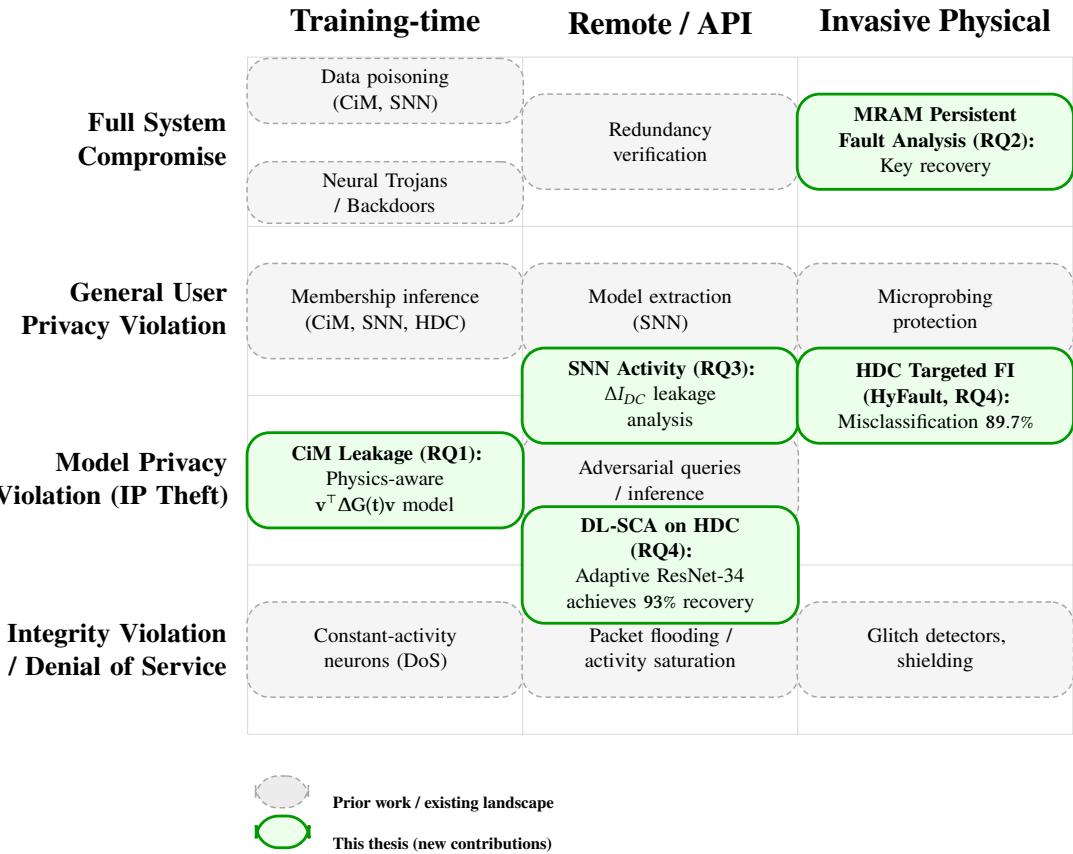

| 1.3. Coverage of research gaps by this thesis. The diagram maps the threat landscape across attack vectors (columns) and impact severity (rows). Green ovals denote the specific contributions of this work, filling critical gaps in prior research (gray dashed ovals). . . . .                                                                                                                                                                                                                                                                                                            | 20 |

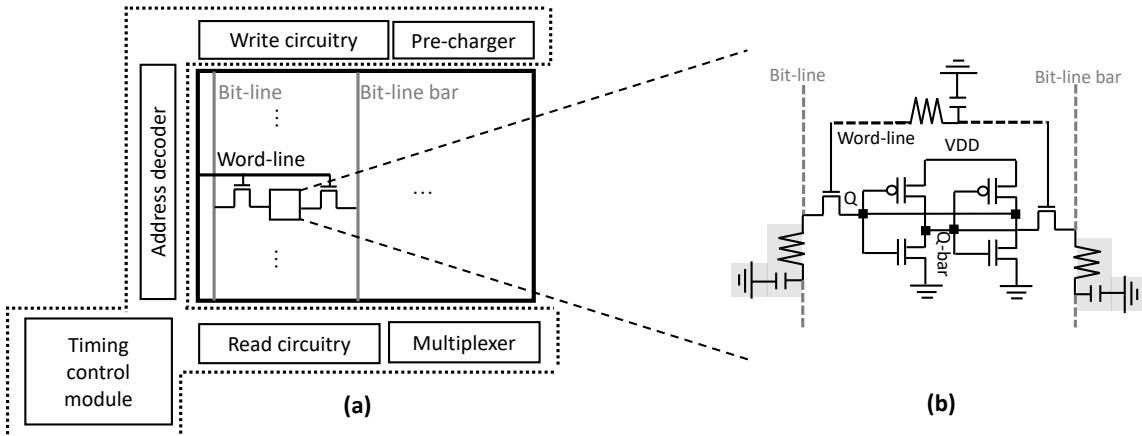

| 2.1. (a) SRAM macro with periphery; (b) 6T bitcell. Distributed Wordline (WL)/Bitline (BL) Resistance–Capacitance (RC) parasitics degrade read/write margins and shape dynamic current signatures. . . . .                                                                                                                                                                                                                                                                                                                                                                                   | 25 |

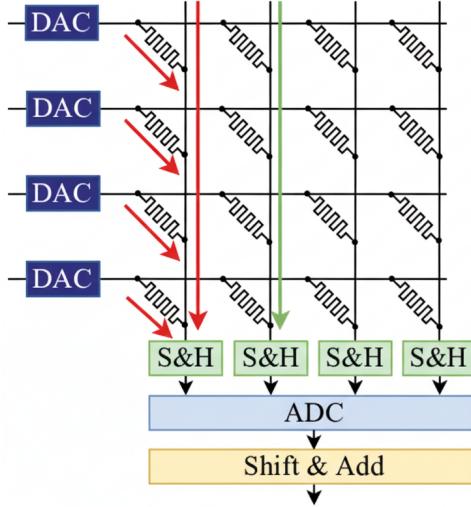

| 2.2. Architecture of Compute-in Memory (CiM). . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 26 |

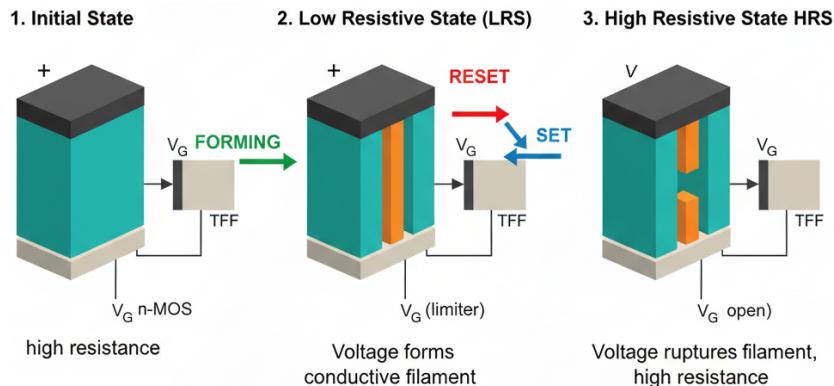

| 2.3. Structure and operation of Resistive-Random Access Memory (ReRAM). . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 26 |

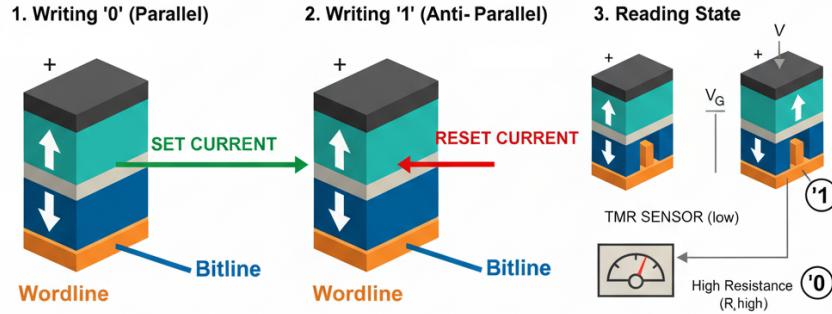

| 2.4. Structure and operation of Spin Torque Transfer-Magnetic Random Access Memory (STT-MRAM). . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 27 |

| 2.5. Overview of different operations in Hyperdimensional Computing (HDC). . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 28 |

| 2.6. Overview of different operations in spike-based Neuromorphic Computing (NC). . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 29 |

| 3.1. Layer-wise leakage extraction in Compute-in-Memory (CiM) framework . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 39 |

| 3.2. Schematic of a scouting-based logic: different references create different logic operations (XOR, AND, etc.). . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 42 |

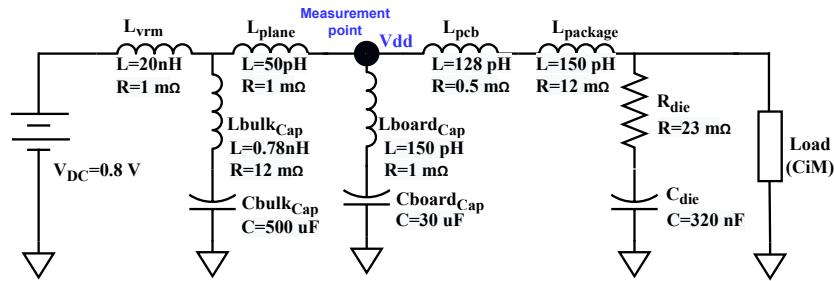

| 3.3. End-to-end simulation framework for evaluating the Correlation Power Analysis (CPA) vulnerability of CiM operations. The pipeline incorporates device-level variation, electrical-level SPICE simulation, Power Delivery Network (PDN) filtering, noise injection, and statistical CPA analysis. . . . .                                                                                                                                                                                                                                                                                | 44 |

| 3.4. End-to-end simulation framework for evaluating the CPA vulnerability of CiM operations. The pipeline incorporates device-level variation, electrical-level SPICE simulation, PDN filtering, noise injection, and statistical CPA analysis. . . . .                                                                                                                                                                                                                                                                                                                                      | 44 |

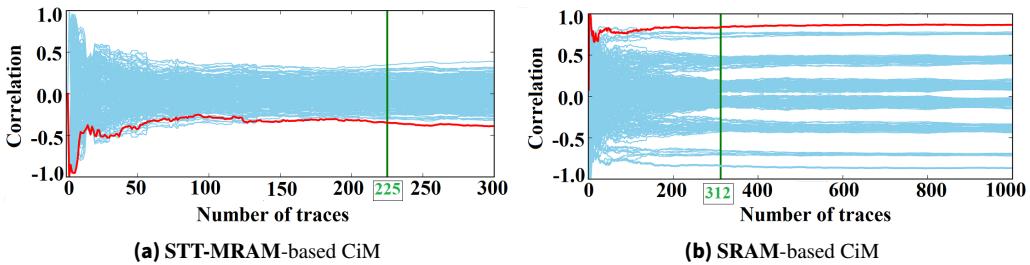

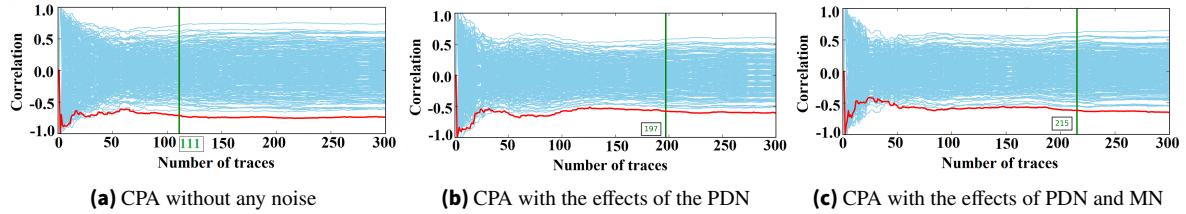

| 3.5. CPA on different CiM implementations of an 8-bit XOR operation with the minimum number of traces for key recovery (marked green) in all plots. For all attacks, the effects of the PDN and Measurement Noise (MN) are considered. . . . .                                                                                                                                                                                                                                                                                                                                               | 45 |

| 3.6. CPAs on Resistive Random-Access Memory (ReRAM)-Magnetoresistive Random-Access Memory (MRAM)-based CiM. Effect of adding the PDN and MN to the simulation flow on the vulnerability of the design, shown by the amount of measurements needed for key recovery (marked green). . . . .                                                                                                                                                                                                                                                                                                   | 46 |

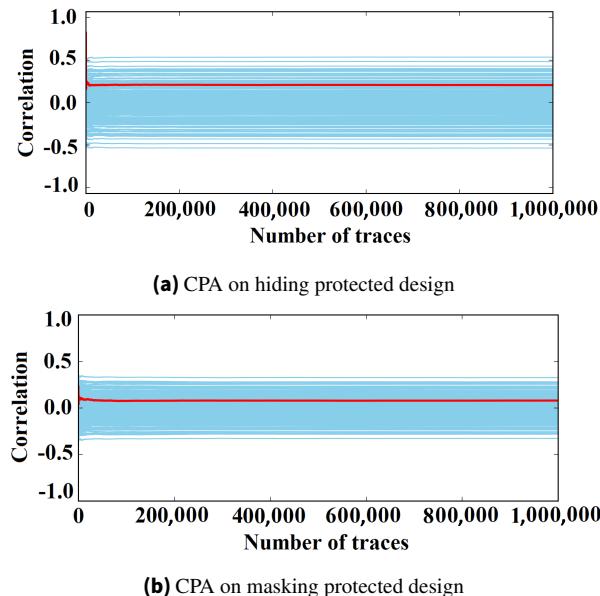

| 3.7. CPA performed on ReRAM-based CiM-design on which our protections are applied, showing in both cases key recovery is unsuccessful. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                               | 47 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.8. Schematic of a MAC+tanh column: weighted current summation followed by a differential-pair tanh activation and optional quantization. . . . .                                                                                                                                                                                                                                                                                                                                                                                                 | 48 |

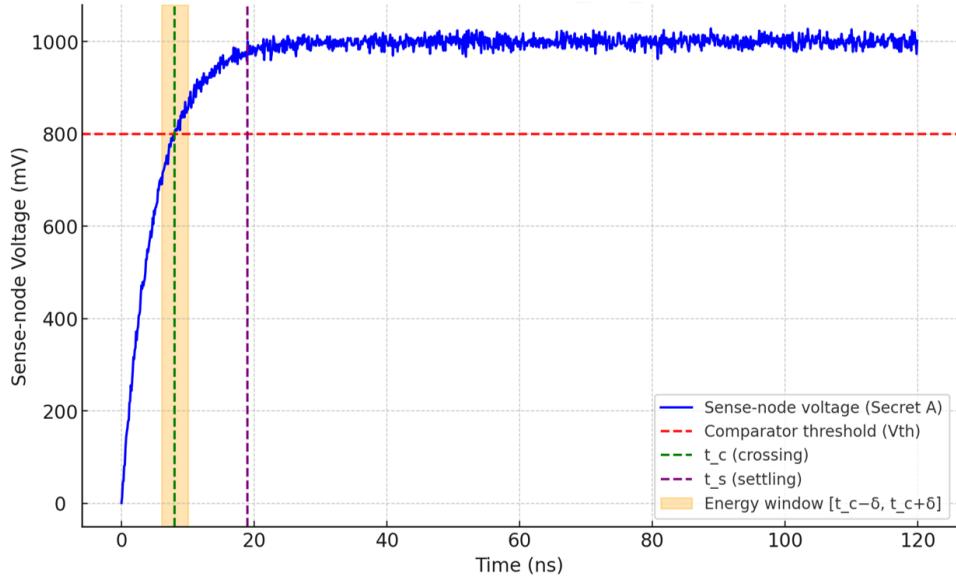

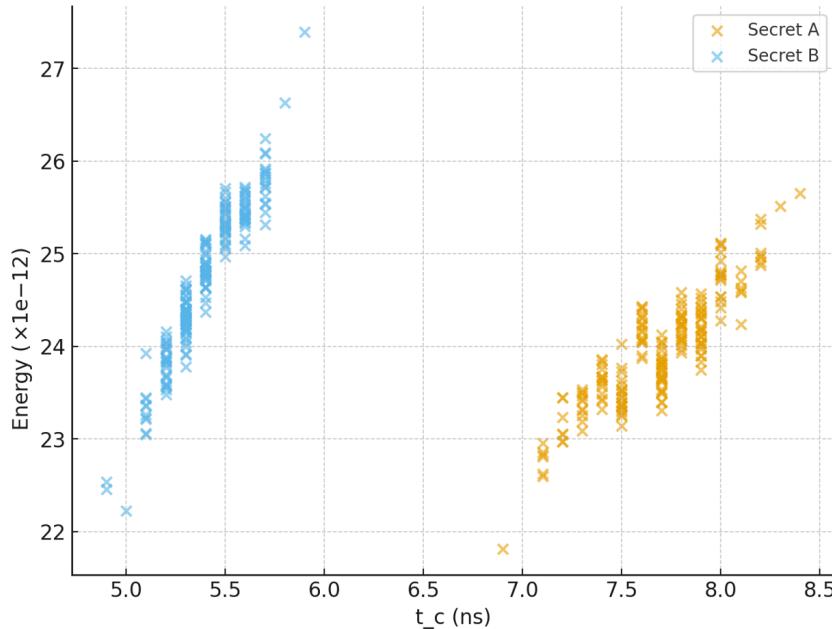

| 3.9. Feature extraction around evaluate and activation: timing landmarks, local energy, slope at the activation edge, and comparator fault flag. . . . .                                                                                                                                                                                                                                                                                                                                                                                           | 50 |

| 3.10. Template separation for different weight codes using activation-edge features; clusters remain linearly separable even under PDN filtering. . . . .                                                                                                                                                                                                                                                                                                                                                                                          | 50 |

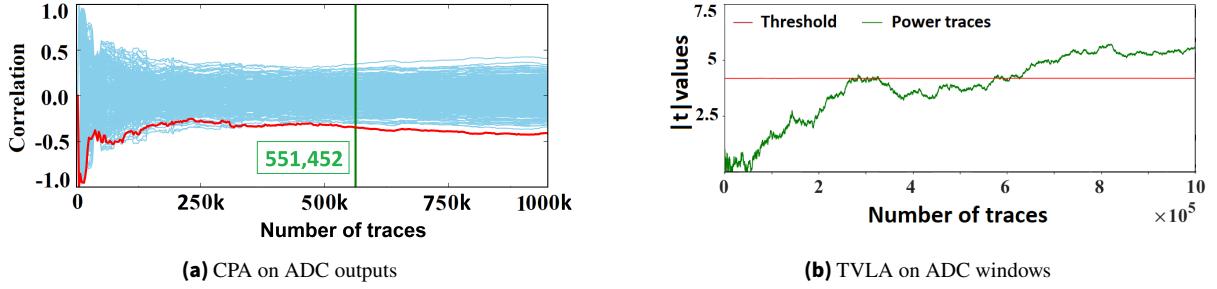

| 3.11. CPA and Test Vector Leakage Assessment (TVLA) on an unprotected MAC+tanh path (16 rows active). Minimum trace counts for disclosure are marked in green in the original plots. . . . .                                                                                                                                                                                                                                                                                                                                                       | 51 |

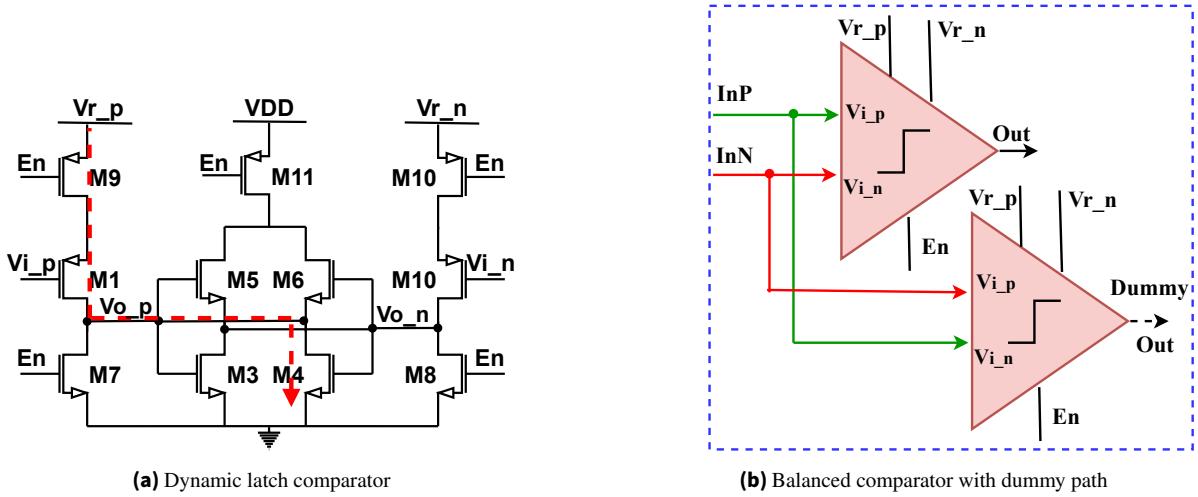

| 3.12. Unprotected and protected comparators used in the activation/quantization stage. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 52 |

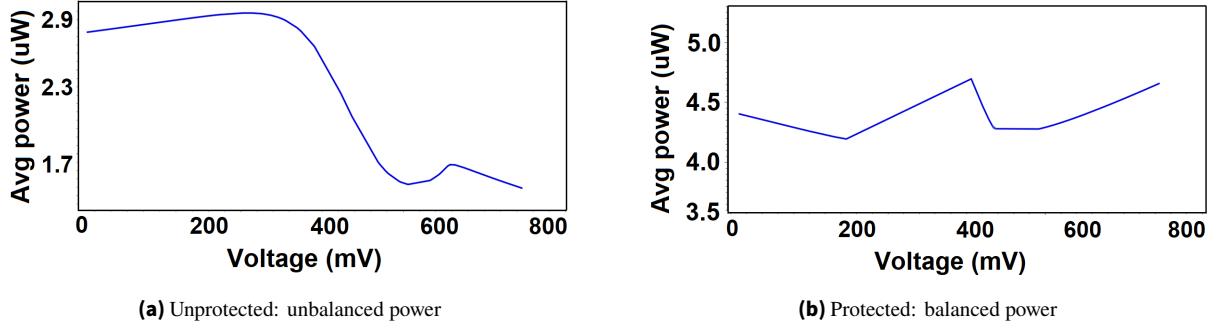

| 3.13. Comparator power vs. input common-mode voltage before and after protection. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 53 |

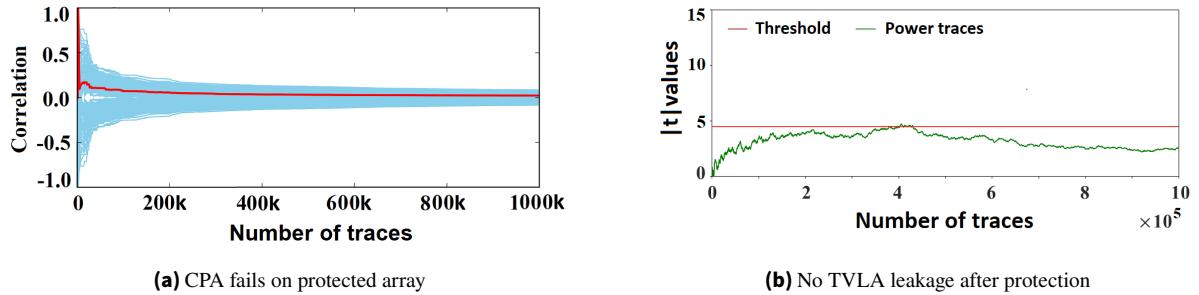

| 3.14. Failed CPA and TVLA on the protected CiM sub-array (8 rows active). . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 53 |

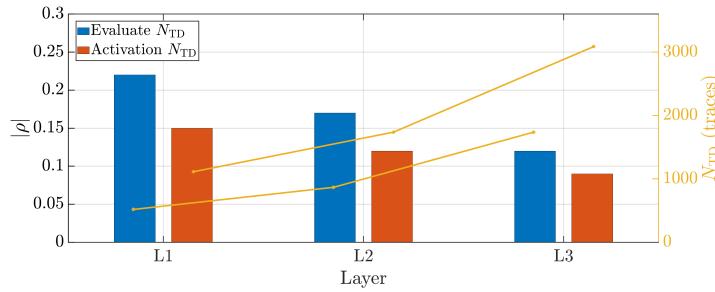

| 3.15. Layer-wise leakage: grouped bars show $ \rho $ in evaluate/activation windows for L1-L3; lines (right axis) show $N_{TD}$ computed with $z = 5$ . L1 dominates; deeper layers are attenuated by tanh and PDN superposition. . . . .                                                                                                                                                                                                                                                                                                          | 54 |

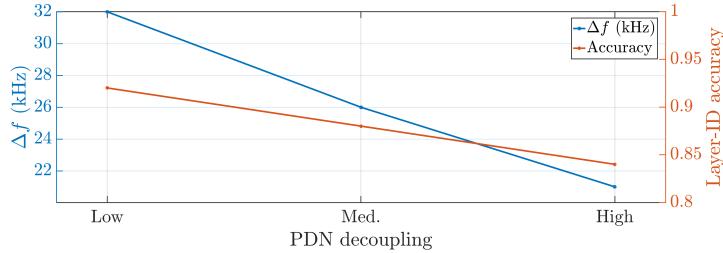

| 3.16. Frequency-domain separability vs. PDN decoupling: $\Delta f$ (left axis) decreases with stronger decoupling, which also reduces a simple layer-ID classifier's accuracy (right axis). . . . .                                                                                                                                                                                                                                                                                                                                                | 55 |

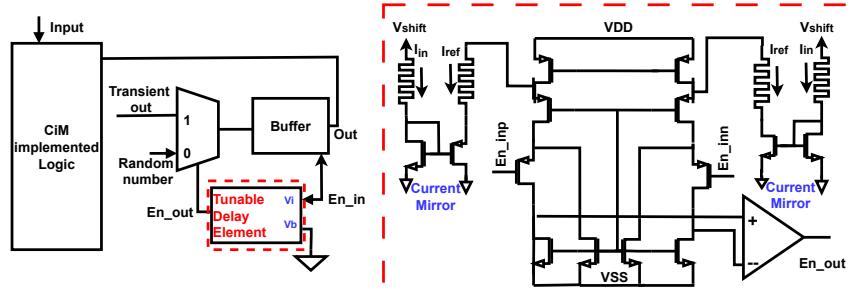

| 3.17. Protected CiM design: tunable delay element in the comparator path to randomize activation timing. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                   | 55 |

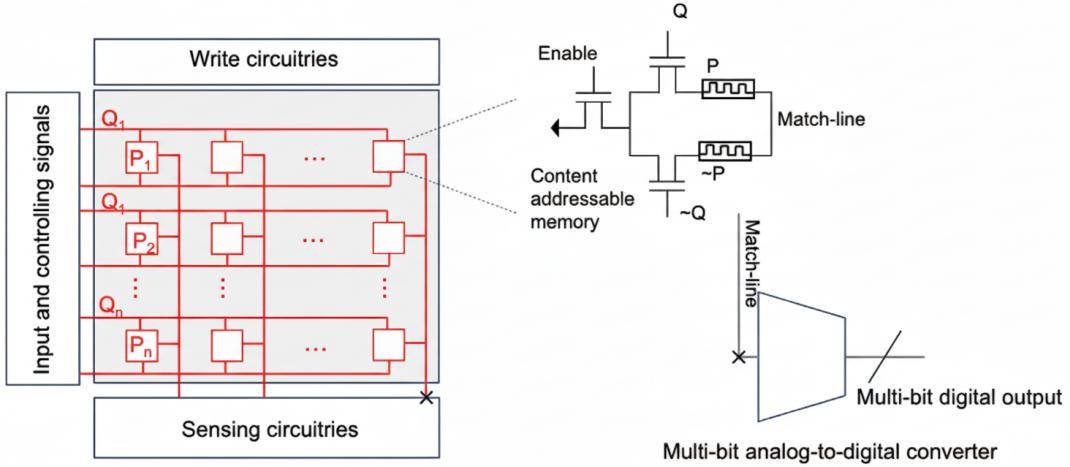

| 3.18. CAM-based HDC search: ML precharge/evaluate and winner-take-all sense. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 56 |

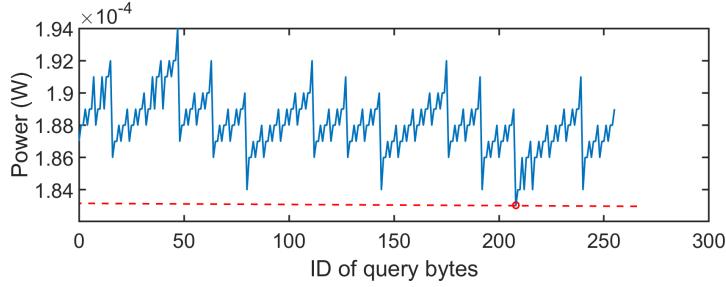

| 3.19. Evaluate-window power vs. 1-byte query candidates: minimum at the correct class hypervector (example: 0xd0). . . . .                                                                                                                                                                                                                                                                                                                                                                                                                         | 57 |

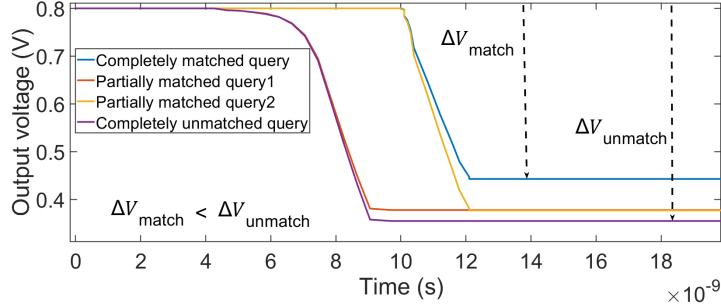

| 3.20. ML voltage: least discharge (closest to $V_{pre}$ ) when $HD(\mathbf{x}, \mathbf{w}_r)$ is minimal (match). . . . .                                                                                                                                                                                                                                                                                                                                                                                                                          | 57 |

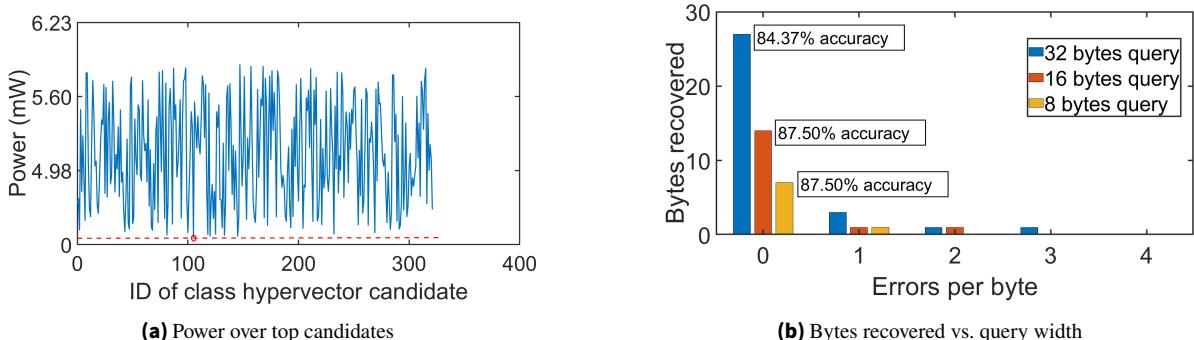

| 3.21. Successful collision+Simple Power Analysis (SPA) attack on class-4 hypervector: correct ID shows the minimum power; byte recovery statistics for 32/16/8-byte queries. . . . .                                                                                                                                                                                                                                                                                                                                                               | 57 |

| 3.22. Protected CAM-HDC: power attack fails. Correct and incorrect candidates are indistinguishable. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                       | 58 |

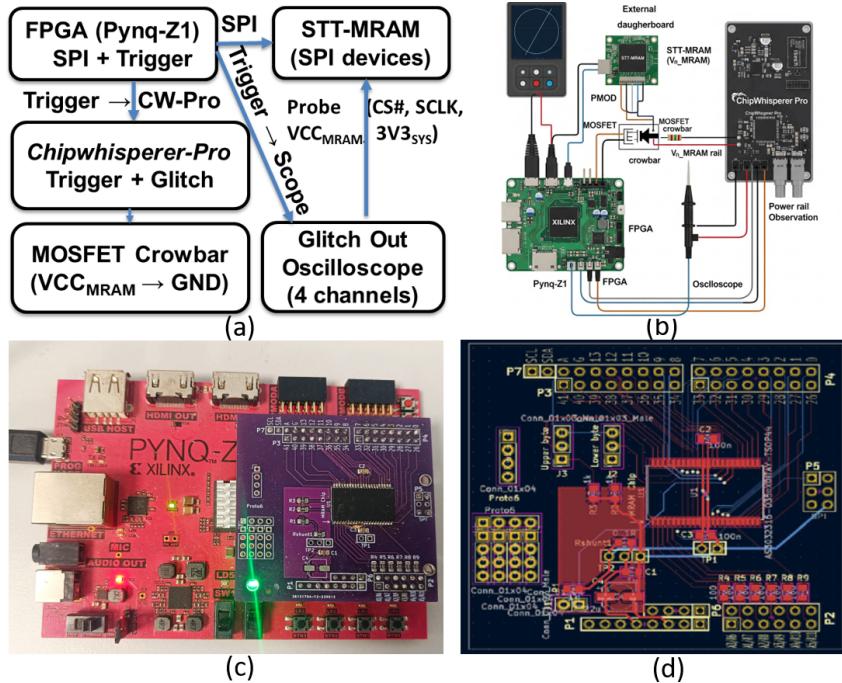

| 4.1. Experimental setup for voltage glitching attacks on Spin-Transfer-Torque Magnetoresistive RAM (STT-MRAM). (a) System-level architecture showing Field-Programmable Gate Array (FPGA) (Pynq-Z1), ChipWhisperer-Pro, and oscilloscope connections for glitch injection and monitoring. (b) Laboratory setup with MRAM mounted on Pynq-Z1, ChipWhisperer CW305, and CW1200. (c) Hardware implementation with MRAM daughterboard interfaced to the Pynq-Z1 FPGA. (d) Printed Circuit Board (PCB) layout of the custom MRAM daughterboard. . . . . | 61 |

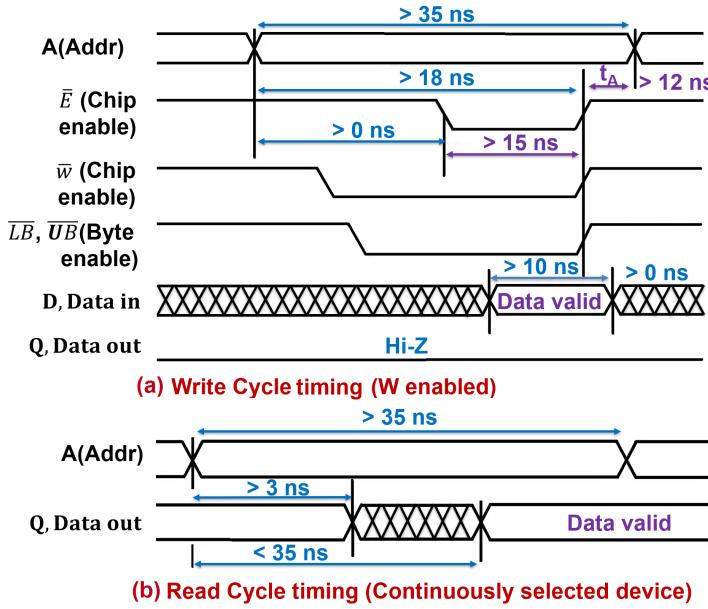

| 4.2. Timing diagrams at the device interface, showing longer write cycle requirements compared to read access. The extended write window makes write operations more susceptible to precisely timed glitch injection, which is leveraged in our fault attack model. . . . .                                                                                                                                                                                                                                                                        | 63 |

| 4.3. Empirical characterization and validation of optimal glitch injection timing in MRAM writes. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                          | 63 |

| 4.4. Spatial/polarity characterization of persistent MRAM faults, used later to weight SPFA scores. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                        | 64 |

| 4.5. Differential Fault Analysis (DFA)/Statistical Persistent Fault Analysis (SPFA) effectiveness under persistent faults: (a) $\approx 12$ pairs reach $\sim 95\%$ per-byte success; (b) with $m=17$ , the correct key reaches rank-1 in $> 99\%$ of trials. . . . .                                                                                                                                                                                                                                                                              | 65 |

| 4.6. SPFA score distribution: the correct key $k^*$ yields a sharp, stable peak at the same $\delta$ across pairs; wrong keys are near-uniform. . . . .                                                                                                                                                                                                                                                                                                                                                                                            | 65 |

| 5.1. Circuit-level implementations of flexible neuromorphic circuits (f-NCs) analyzed in this work. Left: f-SNN cell with Synapse, Charge/Integrate, and Reset/Discharge stages. Right: f-RNN cell with recurrent <i>RC</i> dynamics for continuous-time state evolution. . . . .                                                                                                                                                                                                                                                                  | 72 |

| 5.2. Distinct leakage primitives from raw power traces: spike-driven quasi-DC offsets in f-SNN (left) vs. smoother low-frequency RC oscillations in f-RNN (right). . . . .                                                                                                                                                                                                                                                                                                                                                                         | 73 |

| 5.3. Overview of the FlexSpy framework pipeline. FlexSpy provides a complete design-time flow: from technology-calibrated device simulation and PDN modeling to spike-aligned feature extraction, a calibrated attack suite (CPA, templates, regression, MI), and quantitative localization (SLI), enabling in-loop evaluation of countermeasures. . . . .                                                                                                                                                                                         | 73 |

|                                                                                                                                                                                                                                                                                                                                                                                       |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

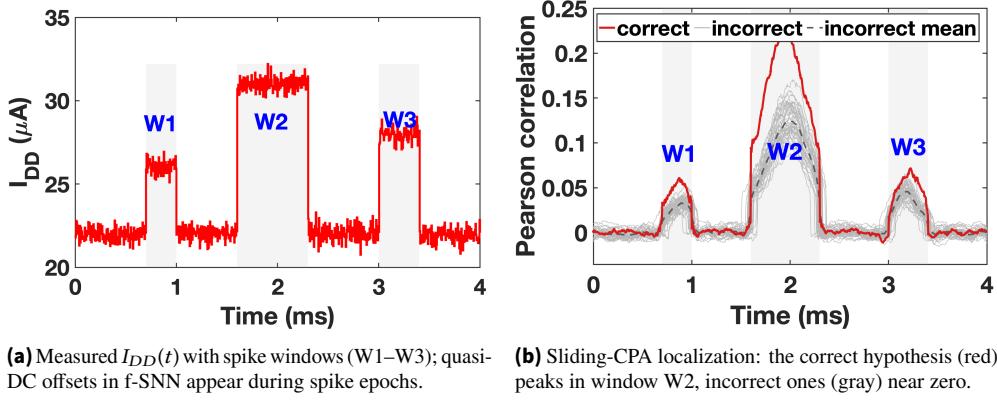

| 5.4. Leakage localization in time for f-SNN on P-Cons. Left: quasi-DC $\Delta I_{DC}$ offsets in $I_{DD}(t)$ during spike epochs. Right: sliding-CPA shows that leakage is maximized in W2. . . . .                                                                                                                                                                                   | 77 |

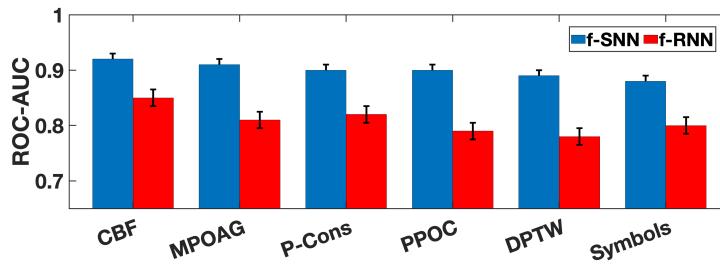

| 5.5. Cross-dataset leakage at the nominal corner: ROC–AUC for label inference using spike-window features on six workloads. Blue bars: <i>f</i> -SNN; red bars: <i>f</i> -RNN; the dotted line indicates chance (AUC = 0.5). The <i>f</i> -SNN consistently leaks more than the <i>f</i> -RNN. . . . .                                                                                | 77 |

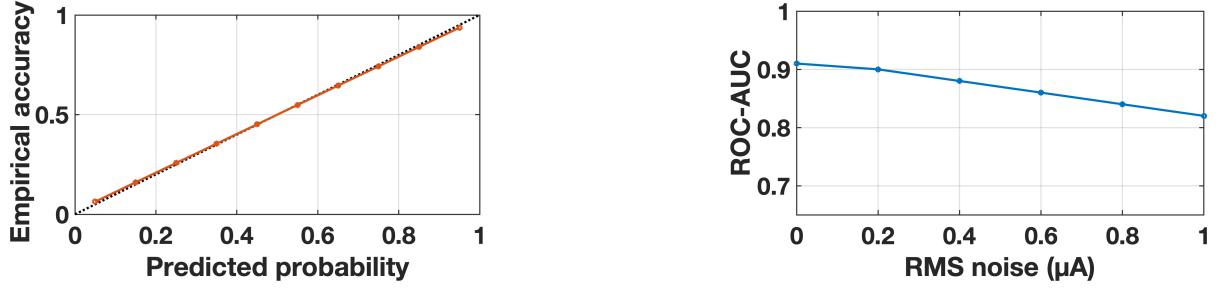

| 5.6. Model reliability and measurement robustness for label inference in f-SNN on P-Cons. . . . .                                                                                                                                                                                                                                                                                     | 78 |

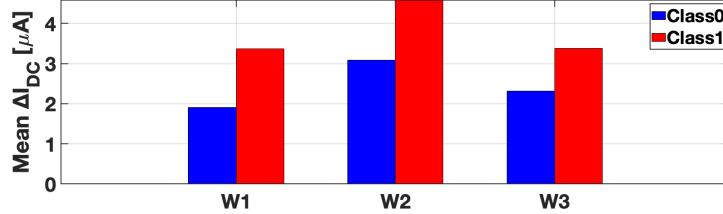

| 5.7. Windowed quasi-DC current shift $\Delta I_{DC}$ by class for f-SNN on P-Cons. Distinct class clusters in the dominant W2 window visualize the rate-weighted $\sum_i g_i s_i$ leakage mechanism. . . . .                                                                                                                                                                          | 78 |

| 5.8. Spike-rate recovery and mutual information analysis for f-SNN. . . . .                                                                                                                                                                                                                                                                                                           | 79 |

| 5.9. Confusion matrices for structural profiling from power traces in f-SNN. Gaussian templates trained on spike-window features can recover both multiplicity and input source clusters. . . . .                                                                                                                                                                                     | 79 |

| 5.10. Direct security comparison of f-SNN vs. f-RNN on P-Cons. The f-SNN’s spike-window $\Delta I_{DC}$ offsets produce stronger instantaneous leakage than the f-RNN’s smoother envelopes. . . . .                                                                                                                                                                                   | 80 |

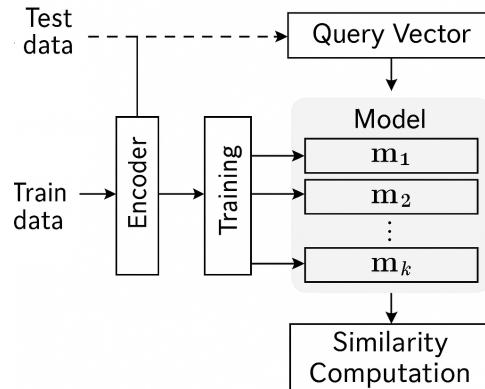

| 6.1. Architecture of the FPGA-based HDC accelerator. Raw data is streamed via DMA, encoded as hypervectors, and classified in the associative memory (AM). Class hypervectors are written by the CPU and stored in AM (large hypervectors are partitioned into segments). The class with the smallest Hamming distance to the query is returned as the classification result. . . . . | 85 |

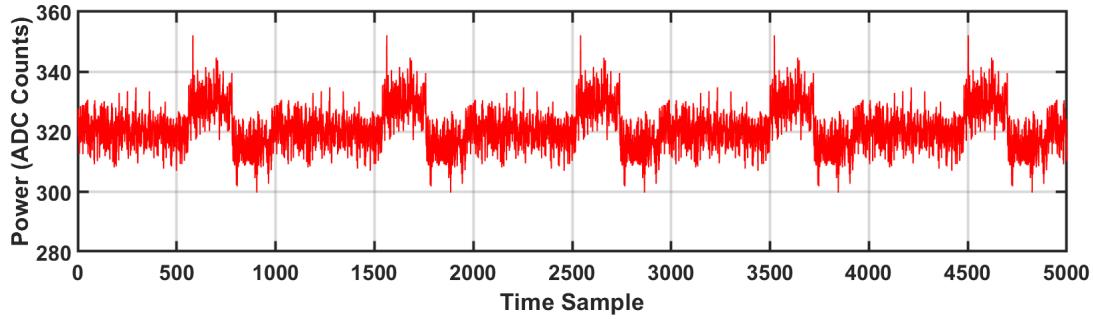

| 6.2. <i>ChipWhisperer</i> -captured FPGA power trace showing different stages of HDC operations. The trace exhibits a periodic pattern after a fixed timestamp, corresponding to similarity computations, which is critical for SCA. . . . .                                                                                                                                          | 86 |

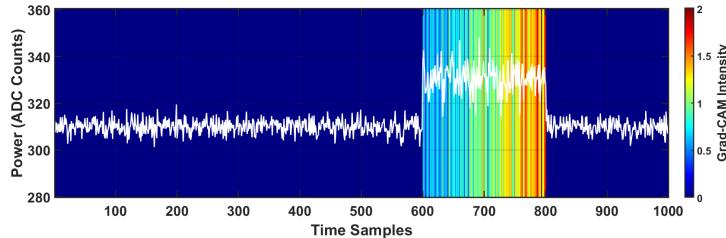

| 6.3. Grad-CAM heatmap highlighting regions within FPGA-based HDC power traces that contribute most to ResNet-34 predictions. The highlighted intervals correspond primarily to XOR similarity and POPCOUNT computations. . . . .                                                                                                                                                      | 87 |

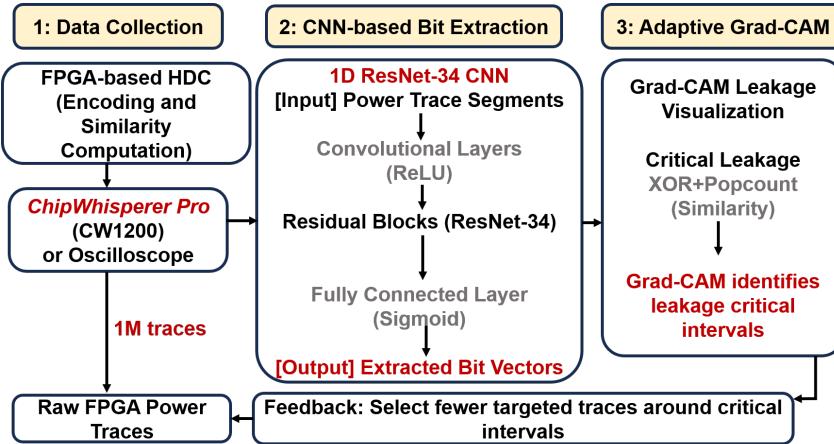

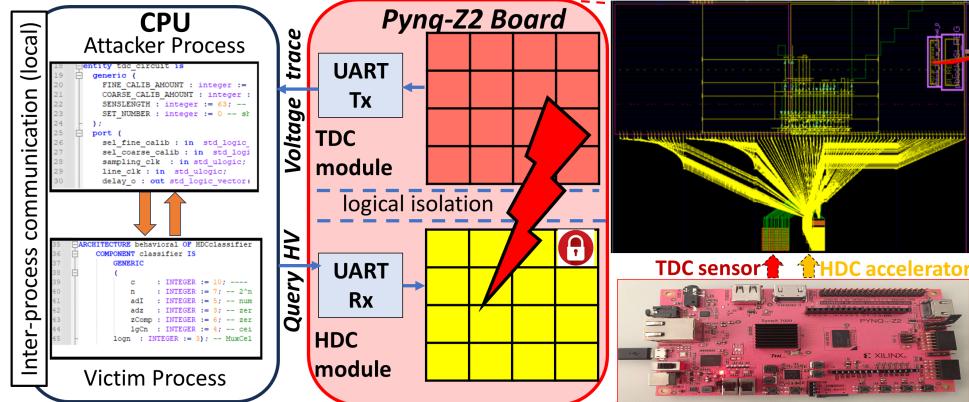

| 6.4. Overview of the proposed adaptive Grad-CAM-based attack workflow. Power traces from HDC inference are fed to a 1D ResNet-34 CNN for bit extraction. Grad-CAM visualizations identify and refine critical leakage intervals, guiding targeted trace selection and cropping to enhance attack efficiency. . . . .                                                                  | 87 |

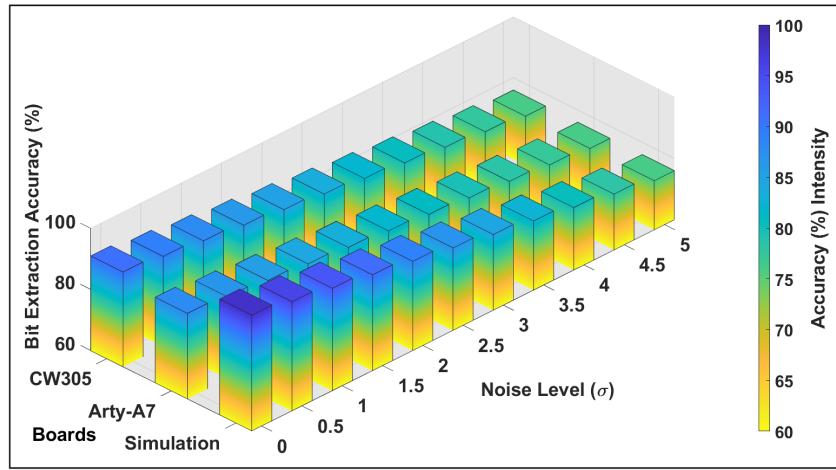

| 6.5. ResNet-34-based bit extraction accuracy across FPGA platforms under explicit noise and jitter conditions. Cross-platform consistency highlights that leakage is dominated by architectural similarity (XOR + POPCOUNT structure) rather than chip-specific artifacts. . . . .                                                                                                    | 88 |

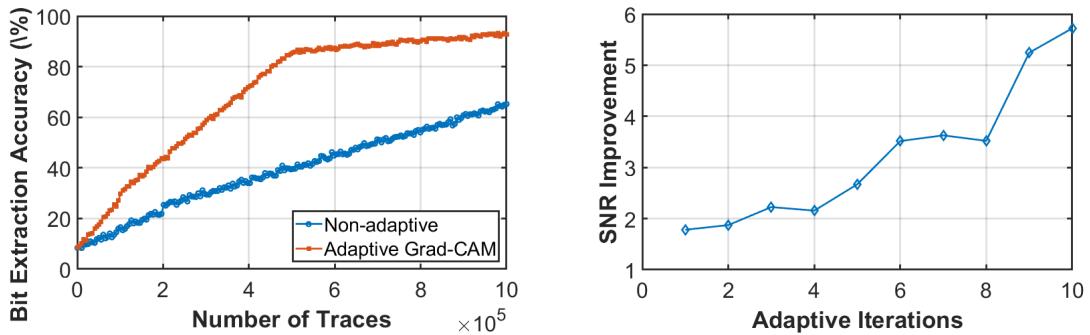

| 6.6. Impact of adaptive Grad-CAM guidance. Left: bit extraction accuracy improvement across iterations for adaptive vs. non-adaptive approaches. Right: SNR improvement across adaptive iterations. The adaptive method achieves significantly higher accuracy with fewer traces by focusing on critical leakage intervals. . . . .                                                   | 89 |

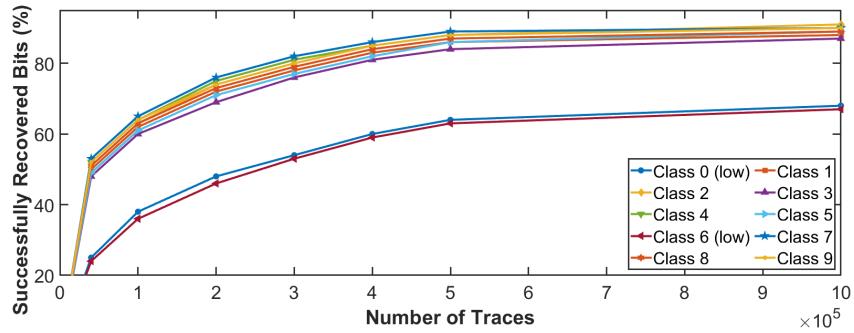

| 6.7. Bit recovery accuracy vs. number of analyzed traces for MNIST. ResNet-34-based SCA converges above 90% accuracy for most classes after $\approx 8 \times 10^5$ traces; some classes (0 and 6) remain harder to recover due to weaker leakage. . . . .                                                                                                                            | 90 |

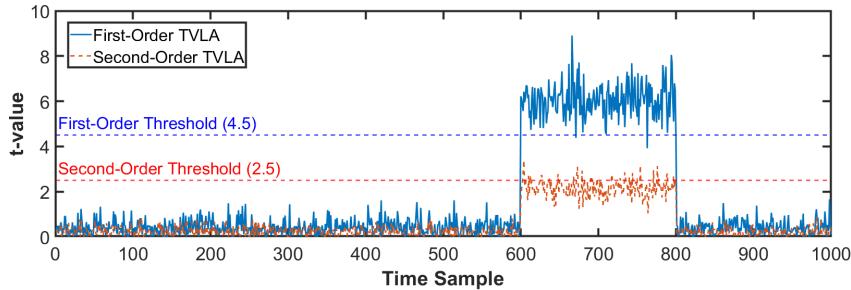

| 6.8. TVLA analysis on unprotected HDC (MNIST): severe first-order leakage (t-values > 4.5) and non-negligible second-order leakage (t-values > 2.5) during XOR and POPCOUNT operations, confirming vulnerability to both first- and higher-order SCA. . . . .                                                                                                                         | 91 |

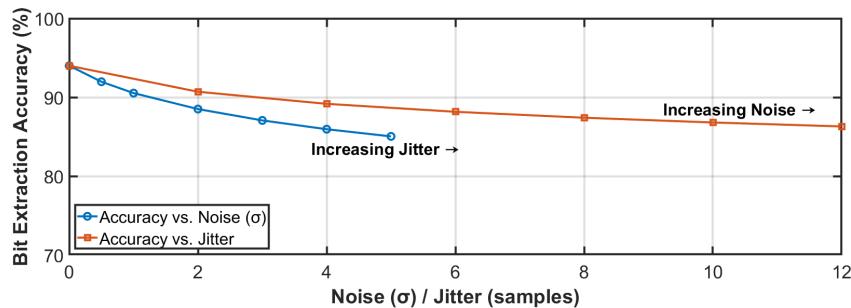

| 6.9. Robustness analysis (MNIST). Bit extraction accuracy of ResNet-34 under increasing Gaussian noise and timing jitter. While accuracy degrades from ideal conditions, the attack remains effective across realistic noise/jitter levels. . . . .                                                                                                                                   | 91 |

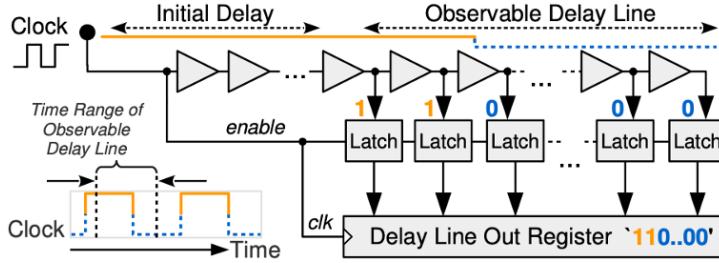

| 6.10. TDC circuit used as an on-chip sensor [67]. A delay line, latches, and capture registers convert fine-grained voltage-induced delay variations into a digital value observable by the attacker. . . . .                                                                                                                                                                         | 93 |

| 6.11. (a) TDC values captured for different class candidates (MNIST) during profiling, demonstrating distinct peaks per candidate. (b) Query injection time vs. peak power timing with queries injected every 100 ns. The staircase pattern reveals the victim HDC execution period (300 ns) and the internal latency ( $\approx 20$ ns offset) to reach peak power. . . . .          | 95 |

---

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

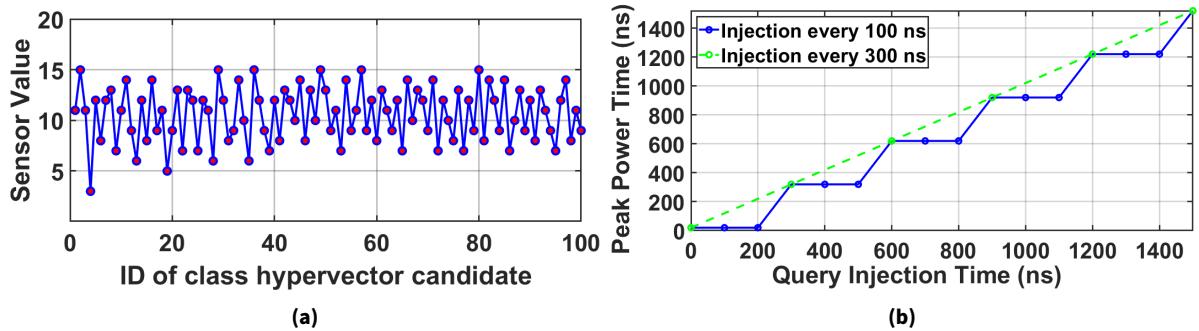

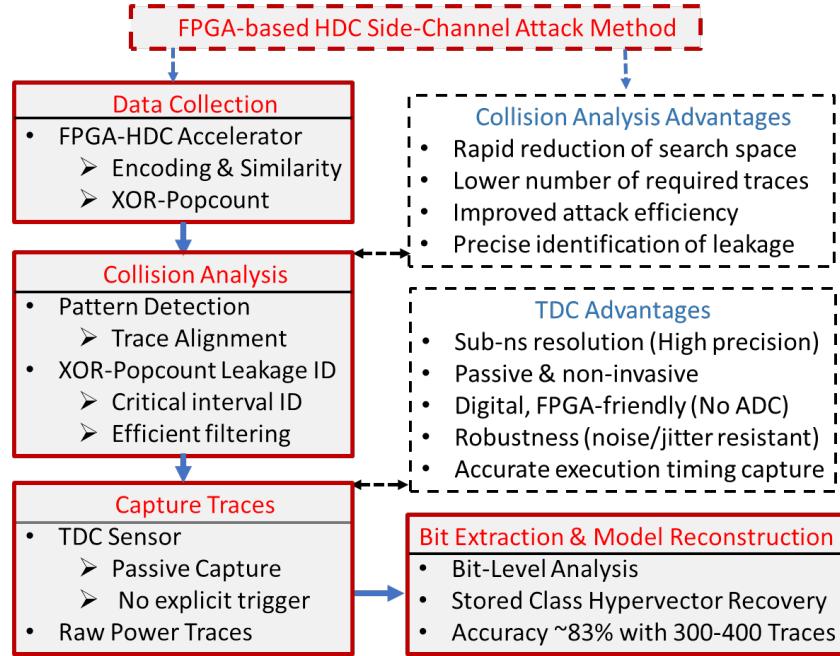

| 6.12. Proposed internal SCA methodology on an HDC accelerator. Stage 1 performs collision-based sensitivity analysis to reduce the hypervector search space. Stage 2 uses a TDC sensor and implicit triggering to distinguish candidate ClassHVs via power-induced timing variations. . . . .                                                                                                                                                                                                                                                                              | 96  |

| 6.13. Floorplan of the proposed attack on Pynq-Z2. The HDC accelerator (victim, red) and TDC sensor (attacker, yellow) are placed in different clock regions within the same FPGA fabric but share the same PDN. Screenshot from Xilinx Vivado. . . . .                                                                                                                                                                                                                                                                                                                    | 96  |

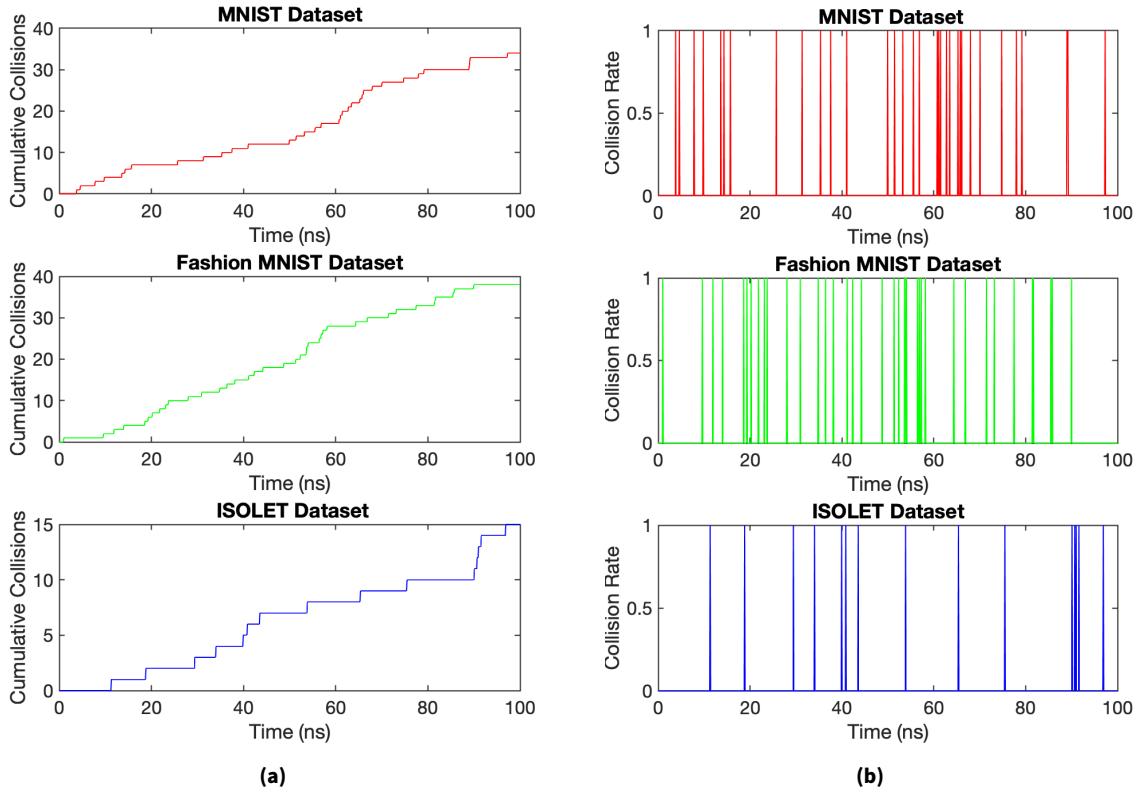

| 6.14. (a) Cumulative number of collisions over time, showing an increasing trend as more query hypervectors are classified. (b) Collision frequency over time, with peaks indicating hypervectors that are particularly likely to align with the target ClassHV. . . . .                                                                                                                                                                                                                                                                                                   | 97  |

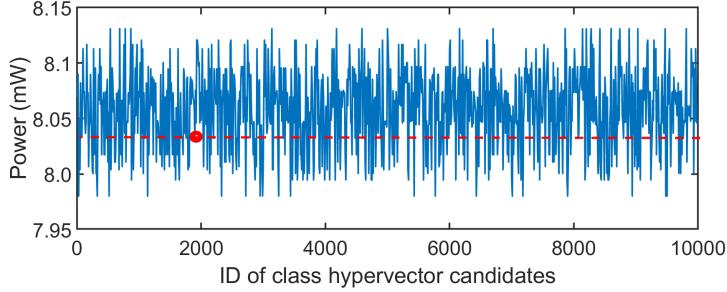

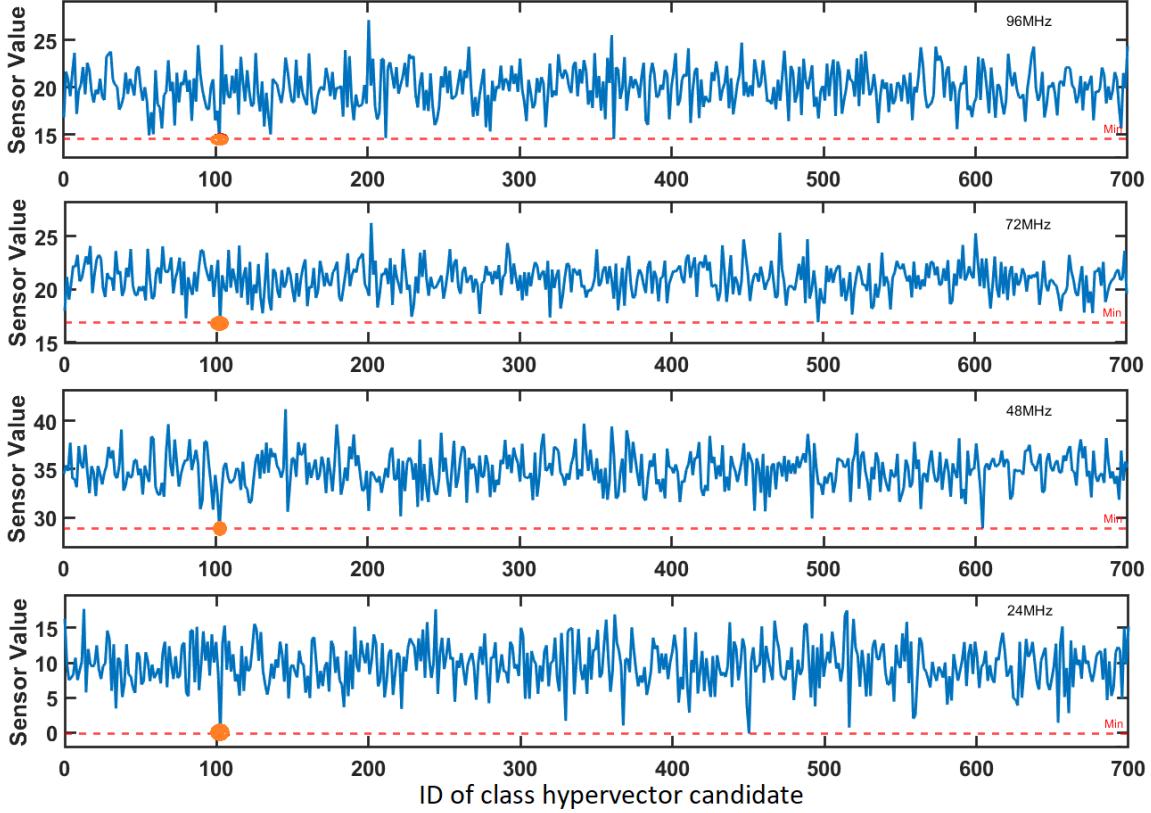

| 6.15. TDC delay-line calibration for candidate ClassHVs on MNIST. The minimum TDC value (red circle) corresponds to the correct candidate (ID 102). Measurements are performed with TDC clocked at 24, 48, 72, and 96 MHz while the HDC remains at 24 MHz. . . . .                                                                                                                                                                                                                                                                                                         | 98  |

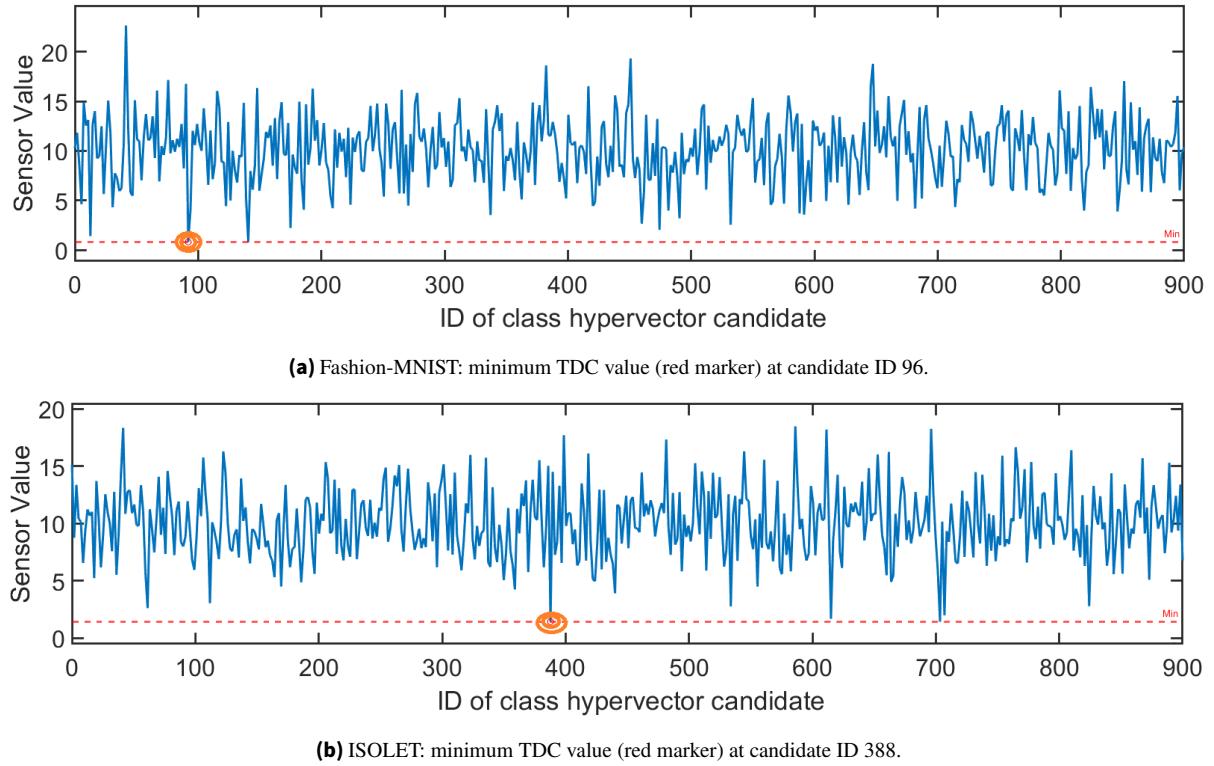

| 6.16. Successful TDC-based power attacks on recovered ClassHVs for Fashion-MNIST and ISOLET when both HDC and TDC modules operate at 24 MHz. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                       | 99  |

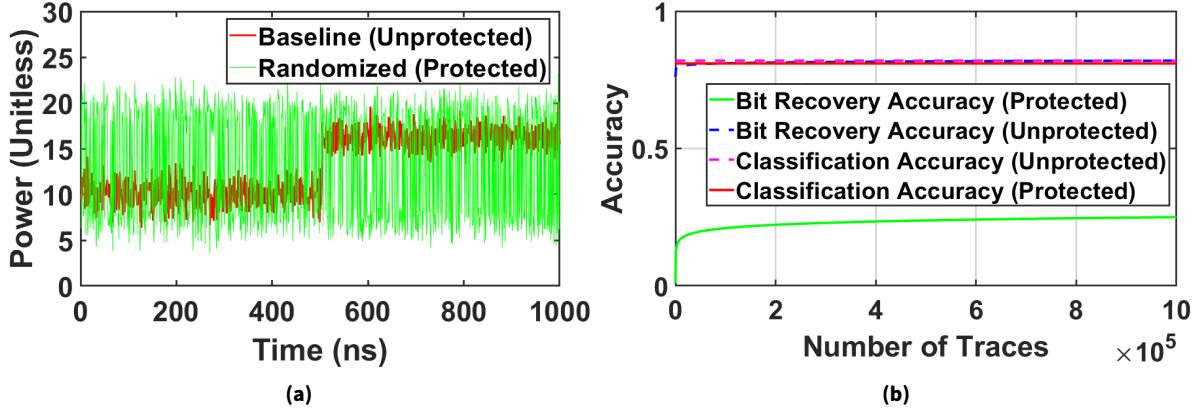

| 6.17. Effect of randomization on MNIST. (a) Sample power patterns of HDC operations with and without randomization: the baseline (blue) shows predictable patterns, while the randomized design (green) significantly disrupts correlation and peak structure. (b) Classification accuracy (black, overlapping for protected and unprotected designs) and maximum bit recovery accuracy for a single class: randomization reduces recovery from $\approx 80$ – $83\%$ (blue) to $\approx 19\%$ (green). . . . .                                                            | 100 |

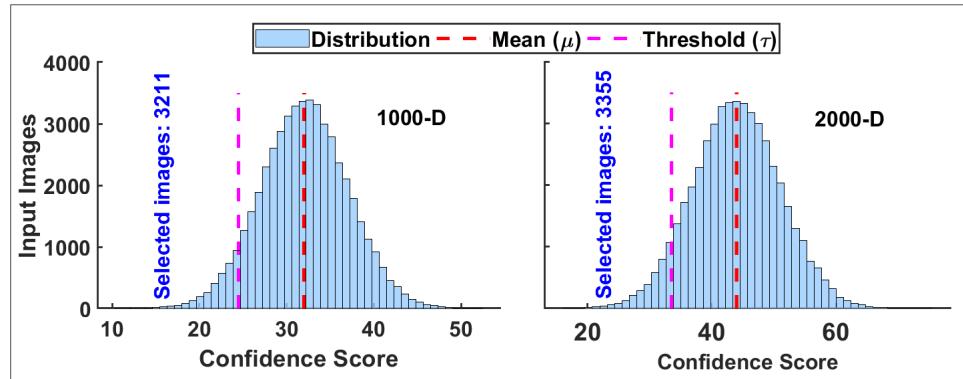

| 6.18. Confidence score distribution for 100k random input hypervectors (1000-D and 2000-D). The adaptive threshold $\tau$ (pink) selects boundary-sensitive inputs near the decision boundary. . . . .                                                                                                                                                                                                                                                                                                                                                                     | 102 |

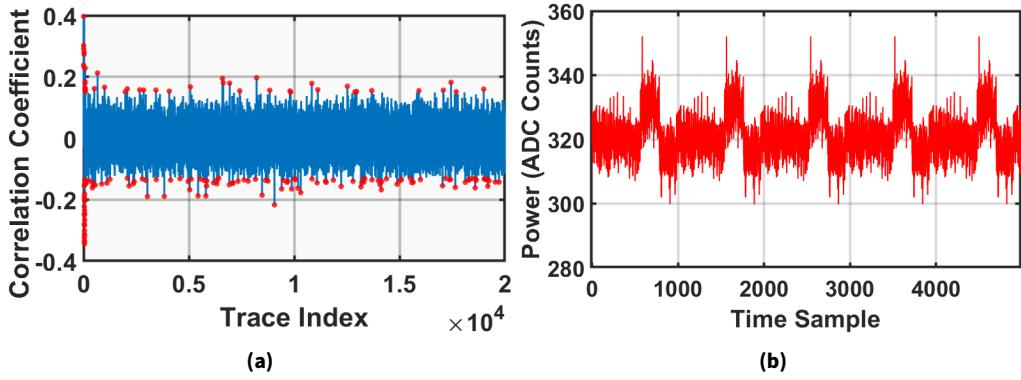

| 6.19. Profiling and sensitivity analysis on 1000-D HDC (MNIST). (a) CPA correlation coefficients; hypervectors above the 0.15 threshold (red line) are highly sensitive and suitable for targeted FI. (b) Representative power trace showing three phases: encoding, similarity computation, and writing. The similarity phase exhibits the highest data-dependent variance and becomes the primary target for fault injection. . . . .                                                                                                                                    | 103 |

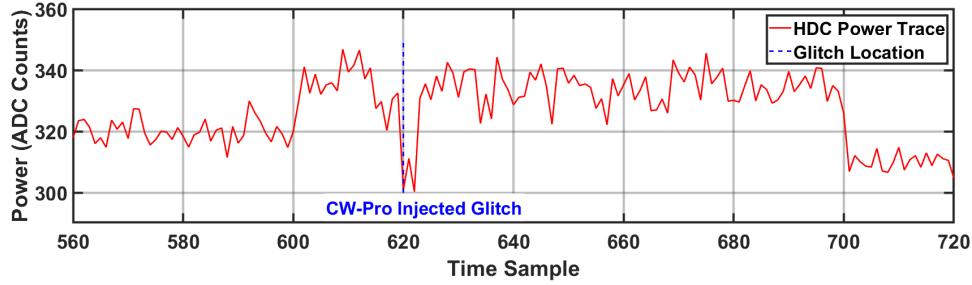

| 6.20. ChipWhisperer Pro trace with a single voltage glitch (blue) at 622 ns within the similarity computation window (MNIST). This window is identified as highly fault-sensitive via profiling. . . . .                                                                                                                                                                                                                                                                                                                                                                   | 104 |

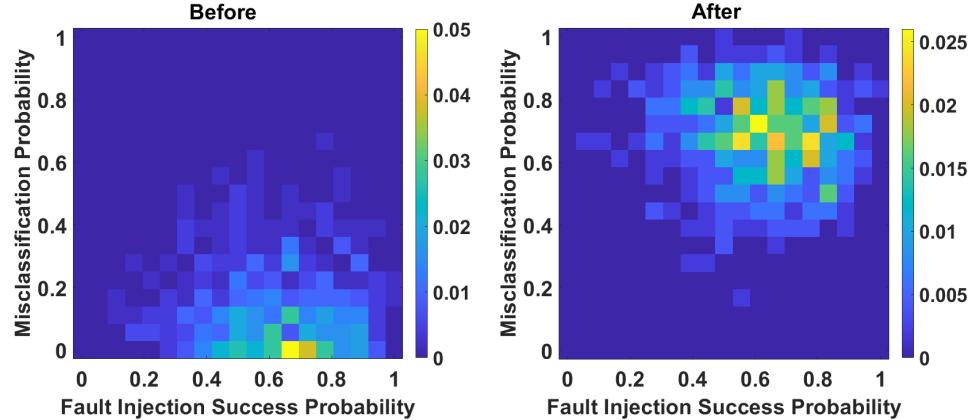

| 6.21. Comparison of fault injection effectiveness before and after parameter optimization (1000-D MNIST). After tuning glitch width, offset, and repetition count, successful faults more consistently result in misclassification rather than resets or benign behavior. . . . .                                                                                                                                                                                                                                                                                          | 104 |

| 6.22. Countermeasure structure combining LFSR-based permutation randomization and dual XOR masking. Class hypervectors are masked and permuted offline; query hypervectors are dynamically masked and permuted at runtime, complicating precise glitch timing and profiling. . . . .                                                                                                                                                                                                                                                                                       | 106 |

| 6.23. Experimental setup: control PC, Pynq Z2 and Arty-A7 FPGA boards, ChipWhisperer Pro (CW1200) for voltage glitching, and CW305 Artix-7 FPGA target board for precise characterization of HyFault. . . . .                                                                                                                                                                                                                                                                                                                                                              | 106 |

| 6.24. Empirical analysis for optimal fault injection. (a) Misclassification probability across candidate timestamps (5 ns increments); the optimal region near 78 ns is highlighted. (b) Misclassification vs. glitch width, showing minimal effect at small widths, rapid growth between 20–30 ns, and saturation beyond 30 ns. . . . .                                                                                                                                                                                                                                   | 107 |

| 6.25. Comparison of unprotected and protected HDC designs on MNIST under voltage-level fault injection. (a) Attack success rate as a function of the number of glitch attempts for 1000-D and 2000-D hypervectors, showing that countermeasures suppress misclassification from $\sim 89\%$ down to $\leq 2$ – $3\%$ . (b) Power-trace variance before and after protection: the unprotected design (red) exhibits strong data-dependent fluctuations, whereas the protected design (blue) drastically reduces variance, indicating effective leakage suppression. . . . . | 108 |

|                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

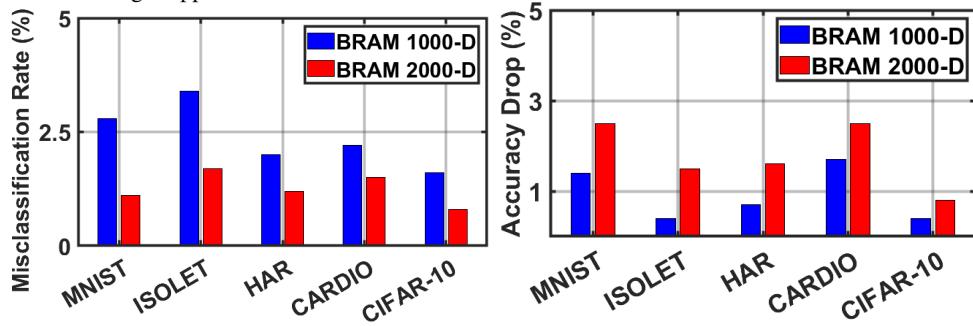

| 6.26. Effect of hypervector dimensionality and countermeasures on BRAM-based HDC accelerators.<br>(a) Higher dimensionality (2000-D) further suppresses misclassification rates across all<br>datasets, especially in protected designs. (b) The resulting accuracy loss remains small<br>(2–3%), demonstrating that the proposed countermeasures provide strong robustness with<br>minimal performance overhead. . . . . | 108 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

# List of Tables

|                                                                                                                                                                                                                                                                                                                                                                |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1. Physical attack taxonomy used in this thesis. . . . .                                                                                                                                                                                                                                                                                                     | 30 |

| 2.2. Attacks and defenses on emerging AI accelerators arranged by <i>Impact</i> (rows) and <i>Access</i> (columns). Red bullets denote <i>attacks</i> ; blue bullets denote <i>defenses</i> . Technology tags: CiM = compute-in-memory, SNN = spiking neural networks, HDC = hyperdimensional computing. . . . .                                               | 33 |

| 3.1. Side-channel paradigms: Digital Complementary Metal–Oxide–Semiconductor (CMOS) vs. Analog CiM. . . . .                                                                                                                                                                                                                                                    | 38 |

| 3.2. Simulation parameters . . . . .                                                                                                                                                                                                                                                                                                                           | 45 |

| 3.3. Leakage predictors and timing windows for scouting-logic XOR. . . . .                                                                                                                                                                                                                                                                                     | 45 |

| 3.4. Minimum number of traces needed to attack various CiM technologies, based on simulations including PV, PDN and MN. The result is averaged over 10 different chip instances. . . . .                                                                                                                                                                       | 46 |

| 3.5. Predictors and timing windows for MAC+tanh. . . . .                                                                                                                                                                                                                                                                                                       | 49 |

| 3.6. MAC+tanh leakage as a function of technology and PDN decoupling. Peak Pearson correlation $ \rho $ is reported for the <i>evaluate</i> window (RC discharge) and the <i>activation</i> window (tanh bias modulation). $N_{TD}$ is the traces-to-disclosure estimate using $N_{TD} \approx z^2/\rho^2$ with $z=5$ . . . . .                                | 51 |

| 3.7. Impact of Analog-to-Digital Converter (ADC) resolution and dithering on MAC+tanh CPA. Median traces to disclosure ( $N_{TD}$ ) and empirical success rate after 1000 traces, averaged over several seeds and PDN states. Dithering adds small, uniformly distributed input noise at the ADC to break deterministic binning. . . . .                       | 52 |

| 3.8. Layer-wise leakage in a 3-layer analog Multi-Layer Perceptron (MLP) (ReRAM, medium decoupling). Correlation and traces-to-disclosure are reported for <i>evaluate</i> and <i>activation</i> windows per layer. $N_{TD}$ uses $z=5$ . The first layer leaks the most, deeper layers are attenuated by the tanh nonlinearity and PDN superposition. . . . . | 54 |

| 3.9. Frequency-domain separability of layer windows under different PDN decoupling. $\Delta f$ is the mean spectral-centroid difference between adjacent layers (larger is better). “Layer-ID accuracy” is the cross-validated accuracy of a simple frequency-domain classifier that assigns a window to its layer. . . . .                                    | 55 |

| 3.10. CAM-HDC identifiability: goodness-of-fit between predicted (Hamming Distance (HD)) and measured match-line energy, together with median traces to disclosure for exact class-HV recovery with a 32-byte query. ReRAM exhibits higher amplitude and slightly better model fit, MRAM is cleaner but smaller in magnitude. . . . .                          | 56 |

| 3.11. Collision-style class-HV recovery for CAM-HDC. Reported are recovered bytes and number of required candidate queries for different query widths. Protected design uses random precharge, staggered activation, and reference dithering. . . . .                                                                                                          | 56 |

| 4.1. Our work vs prior MRAM security literature . . . . .                                                                                                                                                                                                                                                                                                      | 66 |

| 5.1. Spike-Leakage Index (SLI) in dominant window W2 for f-SNN on P-CONS. Both countermeasures (CMs) are effective, and the combination provides the strongest hotspot suppression. . . . .                                                                                                                                                                    | 80 |