SIMULATION UND MODELLIERUNG

DER ELEKTRISCHEN EIGENSCHAFTEN GEDRUCKTER ELEKTRONIK

Zur Erlangung des akademischen Grades eines

Doktors der Naturwissenschaften (Dr. rer. nat.)

von der KIT-Fakultät für Physik

des Karlsruher Instituts für Technologie (KIT)

angenommene

Dissertation

von

M. Sc. Manuel Rommel

Tag der mündlichen Prüfung:

07.11.2025

1. Referent:

Prof. Dr. Wolfgang Wenzel

2. Korreferentin:

Prof. Dr. Jasmin Aghassi-Hagmann

Dieses Werk ist lizenziert unter einer Creative Commons Namensnennung 4.0 International Lizenz (CC BY 4.0): <https://creativecommons.org/licenses/by/4.0/deed.de>

# Inhaltsverzeichnis

|                                                                             |           |

|-----------------------------------------------------------------------------|-----------|

| <b>1 Einleitung</b>                                                         | <b>7</b>  |

| <b>2 Grundlagen</b>                                                         | <b>11</b> |

| 2.1 Gedruckte Transistoren/Elektronik . . . . .                             | 11        |

| 2.2 Feldeffekttransistoren . . . . .                                        | 12        |

| 2.3 Elektrochemische Doppelschicht . . . . .                                | 16        |

| 2.4 Elektrolyt als Gatekontakt . . . . .                                    | 18        |

| 2.5 Metalloxide . . . . .                                                   | 19        |

| 2.6 Kohlenstoff-Nanoröhrchen . . . . .                                      | 21        |

| 2.7 Markov-Chain-Monte-Carlo . . . . .                                      | 23        |

| 2.8 Drift-Diffusionsmodell, Halbleitergleichungen . . . . .                 | 25        |

| 2.9 Numerische Lösungsmethoden partieller Differenzialgleichungen . . . . . | 28        |

| <b>3 Methoden</b>                                                           | <b>30</b> |

| 3.1 Monte-Carlo-Simulation der Mikrostruktur . . . . .                      | 30        |

| 3.2 Lösung der Halbleitergleichungen . . . . .                              | 31        |

| 3.2.1 Geometrieaufbau und externe Vorbereitung . . . . .                    | 32        |

| 3.2.2 Definitionen und Randbedingungen im Halbleitermodul . . . . .         | 32        |

| 3.2.3 Vernetzung . . . . .                                                  | 35        |

| 3.2.4 Numerischer Löser . . . . .                                           | 36        |

| 3.2.5 3D-vFET-Modell . . . . .                                              | 38        |

| 3.2.6 2D-vFET-Modell mit Elektrolyt . . . . .                               | 39        |

| <b>4 Gedruckter Feldeffekttransistor mit vertikalem Stromfluss</b>          | <b>41</b> |

| 4.1 Experimentelles Setup . . . . .                                         | 42        |

| 4.2 Morphologie und Geometrie . . . . .                                     | 43        |

| 4.3 Modellierung des vFET und mikroskopische Ladungsverteilung . . . . .    | 46        |

| 4.3.1 Anpassung der Parameter . . . . .                                     | 46        |

| 4.3.2 Ladungsverteilung im Halbleiter . . . . .                             | 50        |

| 4.3.3 Ionenverteilung im Elektrolyt . . . . .                               | 53        |

| 4.4 Systematische Untersuchung des Verhaltens des vFET . . . . .            | 55        |

| 4.4.1 Einfluss der Domänengröße . . . . .                                   | 56        |

| 4.4.2 Einfluss der Dotierkonzentration . . . . .                            | 58        |

| 4.5 Randverluste und Eindringtiefe des Elektrolyt . . . . .                 | 61        |

| 4.5.1 Randströme . . . . .                                                  | 61        |

| 4.6 Zusammenfassung . . . . .                                               | 66        |

|                                                                         |            |

|-------------------------------------------------------------------------|------------|

| <b>5 Schwellspannungs-Modell basierend auf Grenzschicht-Kapazitäten</b> | <b>68</b>  |

| 5.1 Qualitatives Modell der Schwellspannung im EGFET . . . . .          | 69         |

| 5.1.1 Motivation . . . . .                                              | 69         |

| 5.1.2 Annahmen und Voraussetzungen . . . . .                            | 70         |

| 5.1.3 Beschreibung und Diskussion des Modells . . . . .                 | 71         |

| 5.2 Berechnung der Schwellspannung über die Ladungsdichte . . . . .     | 74         |

| 5.2.1 Ersatzschaltbild des Gate-Stromkreises . . . . .                  | 74         |

| 5.2.2 Herleitung der Ladungsdichte am der Halbleiter-Grenzschicht .     | 76         |

| 5.2.3 Herleitung des geschlossenen Ausdrucks für die Schwellspannung    | 78         |

| 5.2.4 Bedeutung von Kontaktspannungen . . . . .                         | 80         |

| 5.3 Anwendung des Modells auf reale Systeme . . . . .                   | 81         |

| 5.3.1 Skalierung der Schwellspannung mit der Länge des Leitungskanals   | 81         |

| 5.3.2 Einfluss der Größe der Gate-Elektrode auf die Schwellspannung     | 88         |

| 5.4 Zusammenfassung . . . . .                                           | 93         |

| <b>6 Teilchendiffusion auf Kohlenstoffnanoröhrchen</b>                  | <b>94</b>  |

| 6.1 Simulation der Diffusion und Ladungsübergänge in 1D (CNT) . . . . . | 95         |

| 6.2 Verringerung der Photoeffizienz durch Exziton-Exziton-Quenching . . | 98         |

| 6.3 Stromfluss durch asymmetrische Photoexzitonen-Erzeugung . . . . .   | 101        |

| <b>7 Zusammenfassung und Ausblick</b>                                   | <b>105</b> |

| <b>8 Anhang</b>                                                         | <b>108</b> |

| 8.1 Nutzung von COMSOL . . . . .                                        | 108        |

| 8.1.1 Überblick über COMSOL . . . . .                                   | 108        |

| 8.1.2 Beschleunigung der Berechnungen . . . . .                         | 110        |

| 8.1.3 Konvergenzerleichterungen . . . . .                               | 112        |

| 8.1.4 Geometrieerstellung, Import und Prozessierung . . . . .           | 113        |

| 8.1.5 Aufbereitung der Ergebnisse . . . . .                             | 115        |

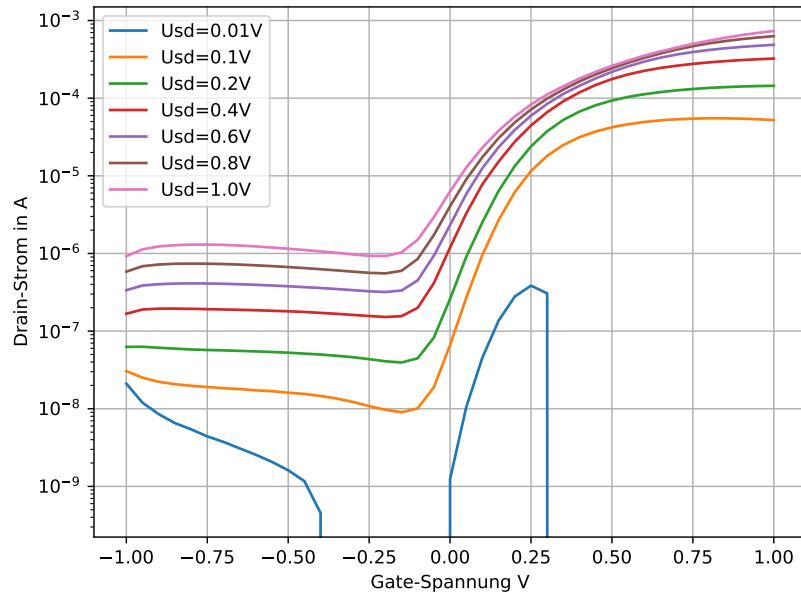

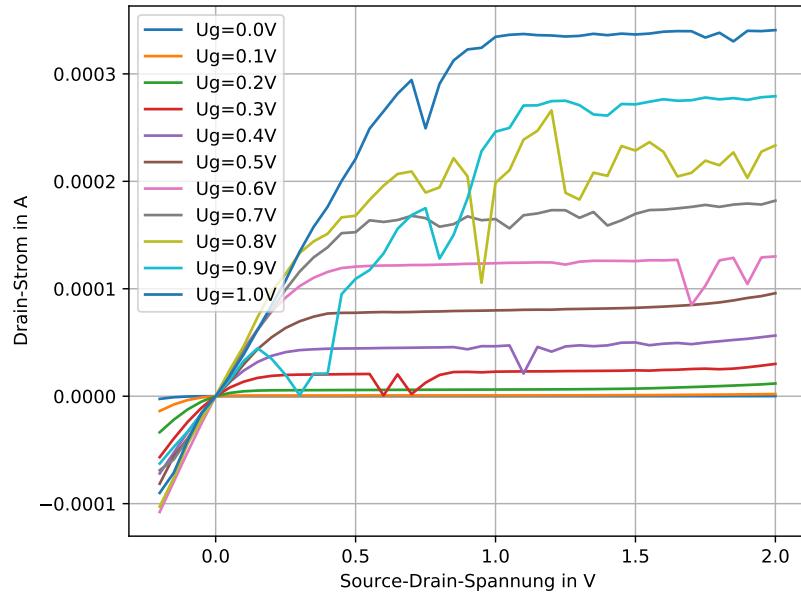

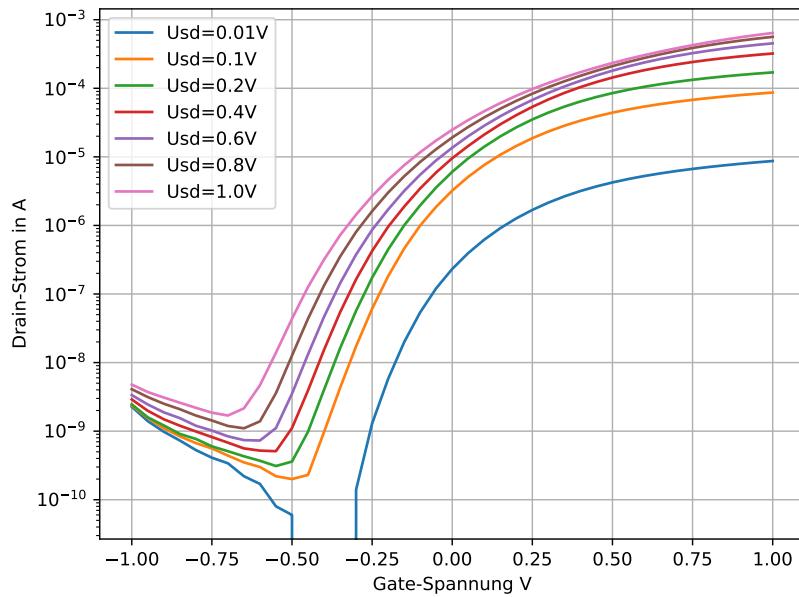

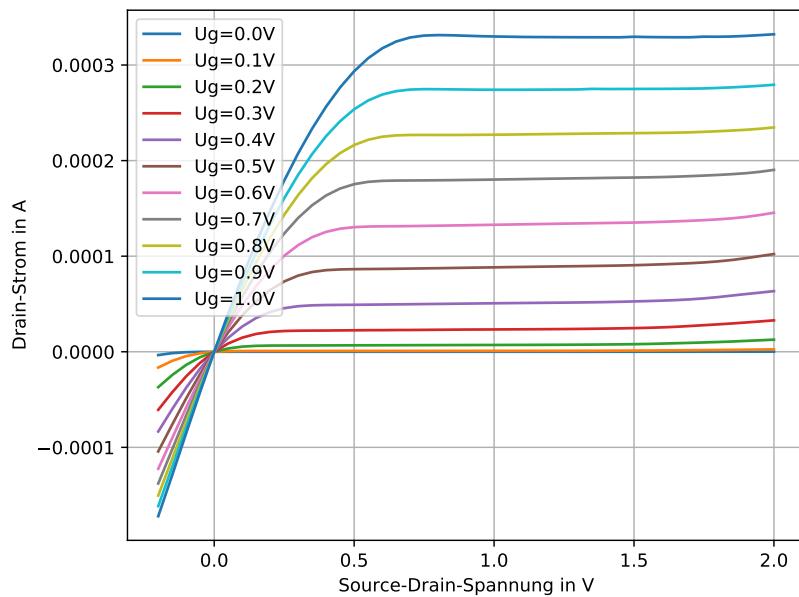

| 8.2 Beispiele für Transfer- und Outputkurven . . . . .                  | 115        |

| 8.3 Gekoppelte Halbleiter-Elektrolyt-Simulation . . . . .               | 119        |

| 8.4 Korrelation der Elektrolyt-Fläche mit der Schwellspannung . . . . . | 122        |

| 8.5 Parameter-Stabilität der Kohlenstoffnanoröhrchen-Simulationen . .   | 127        |

| 8.5.1 Wahl des Zeitschritts . . . . .                                   | 127        |

| 8.5.2 Wahl der Akzeptanzwahrscheinlichkeit für die Ladungsträger in     |            |

| die Elektroden . . . . .                                                | 128        |

# **Publikationen und Beiträge**

## **Veröffentlichungen**

- T. T. Baby<sup>†</sup>, M. Rommel<sup>†</sup>, F. von Seggern, P. Friederich, C. Reitz, S. Dehm, C. Kübel, W. Wenzel, H. Hahn und S. Dasgupta. „Sub-50 nm Channel Vertical Field-Effect Transistors using Conventional Ink-Jet Printing“. In: *Advanced Materials* 29.4 (2017), S. 1603858. DOI: 10.1002/adma.201603858

<sup>†</sup> Geteilte Erstautorenschaft

- F. Rasheed, M. Rommel, G. C. Marques, W. Wenzel, M. B. Tahoori und J. Aghassi-Hagmann. „Channel Geometry Scaling Effect in Printed Inorganic Electrolyte-Gated Transistors“. In: *IEEE Transactions on Electron Devices* 68.4 (2021), S. 1866–1871. DOI: 10.1109/TED.2021.3058929

- S. Kumar, Y. Pramudya, K. Müller, A. Chandresh, S. Dehm, S. Heidrich, A. Fediai, D. Parmar, D. Perera, M. Rommel, L. Heinke, W. Wenzel, C. Wöll und R. Krupke. „Sensing Molecules with Metal–Organic Framework Functionalized Graphene Transistors“. In: *Advanced Materials* 33.43 (2021), S. 2103316. DOI: 10.1002/adma.202103316

## **Konferenzbeiträge**

- M. Rommel, P. Friederich und W. Wenzel. „Simulation of morphology and electric behavior of a printed vertical field effect transistor“. Poster DPG/EPS-Frühjahrtagung. 15. März 2018

- M. Rommel, R. Krupke und W. Wenzel. „Simulation of light-induced exciton diffusion and quenching on SWCNTs“. Poster DPG-Frühjahrtagung (online). 22. März 2021

# 1 Einleitung

Die Industrialisierung hat zu vielfältigen wirtschaftlichen, gesellschaftlichen und sozialen Umbrüchen geführt. Ähnliches gilt für den Übergang ins Informations- bzw. Computerzeitalter, in dem wir uns gegenwärtig befinden. Grundlage hierfür ist die effiziente, automatisierte und schnelle Informationsbearbeitung. Dies hat die in den letzten Jahrzehnten rasante Entwicklung der elektronischen Datenverarbeitung ermöglicht. Angefangen von (elektro-)mechanischen Rechnern wie der Zuse-Maschinen[6, 7] über vollelektrische Röhrenschaltungen und erste Halbleiterbauteile bis hin zu den heutigen Computerchips mit Milliarden von integrierten Elementen ist die Rechenleistung exponentiell gestiegen.[8] Berühmt ist dieser Zusammenhang durch Gordon Moore, der diese Abhängigkeit 1965 empirisch feststellte[9] und postulierte, dass die Menge an integrierten Elementen pro Chip sich ca. alle 2 Jahre verdoppelt.[10] Diese empirische Abhängigkeit gilt bis heute[11], maßgeblich ermöglicht durch immer kleinere Strukturgrößen bei höchstem technologischem Aufwand. Daraus folgen immer größere Rechenleistungen bzw. eine immer größere Recheneffizienz (Rechenleistung pro elektrischer Leistung).

Daneben gibt es immer größere Anwendungsgebiete für Elektronik, die andere Anforderungen an den Herstellungsprozess stellen. So sind z.B. niedrigere Herstellungskosten, bedingt durch eine stark verringerte Herstellungskomplexität verbunden mit weniger hohen Qualitätsansprüchen für die verwendeten Materialien, für manche Anwendungsgebiete wichtiger als eine hohe Schaltfrequenz. Auch sind manche Materialien, wie z.B. Stoff, Papier oder Folie, nicht mit Vakuumprozessierung, hohen Temperaturen und/oder den für herkömmliche Lithographie notwendigen Chemikalien kompatibel. Die Herstellungskosten sind für herkömmlich lithographisch hergestellte Halbleiterbauteile sehr hoch, was konträr mit einigen Anwendungsgebieten ohne große Anforderungen an Rechenleistung ist wie z.B. RFID-Tags oder Einwegsensoren für die Kontrolle der Transport-/Kühlkette.

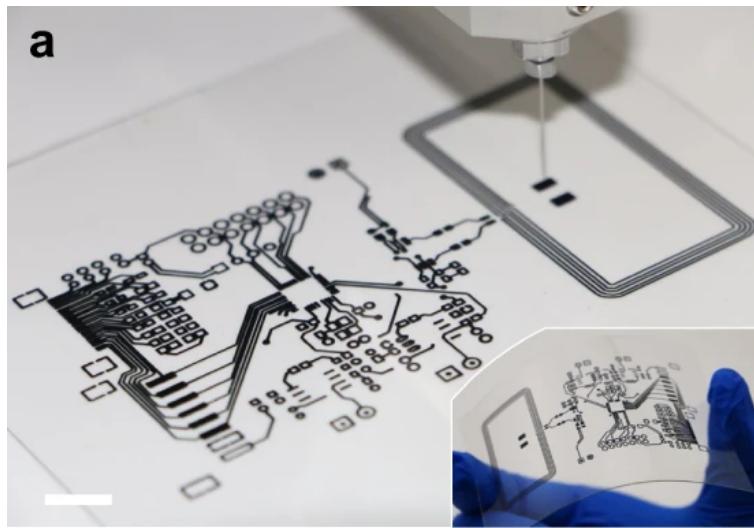

Hier kommt die gedruckte Elektronik[12] ins Spiel. Drucktechniken ermöglichten es in der Geschichte der Menschheit erstmals, Wissen schnell und vergleichsweise einfach massenweise zu kopieren und zu verbreiten. Diese Methoden können auch auf elektronische Schaltkreise angewendet werden. Die Drucktechniken lassen sich heute in viele Teilgebiete unterteilen wie den Tintenstrahl-, Sieb-, Tief- und Hochdruck. Sie haben alle gemeinsam, dass sie ein Substrat additiv kontinuierlich beschichten können. Diese Verfahren erlauben neben herkömmlichen Waver-Substraten auch grundsätzlich andere Substrate, vor allem auch flexible Materialien[13, 14] (Papier, Stoff, Folie), wie in Abb. 1.1 dargestellt. Damit sind sog. *Rolle-zu-Rolle*-Herstellungsprozesse möglich, in denen das Substrat kontinuierlich durch eine Druckmaschine geführt wird.[15, 16] Ein solcher Prozess ermöglicht einen hohen Produktionsdurchsatz, der durch die Breite der gedruckten Bahn und die Geschwindigkeit des Substrats bestimmt wird.

**Abbildung 1.1:** Dargestellt ist ein gedruckter Schaltkreis auf einer flexiblen Folie während des Druckprozesses. Die viskose Tinte aus MXene[18] wurde mit einem pneumatischen Extruder gedruckt. Ausschnitt aus Abbildung von Shao *et al.*[19], lizenziert nach der Creative Commons Attribution 4.0 International-Lizenz (CC BY 4.0)[20].

Als additive Prozesse sind Druckverfahren deutlich materialsparender als herkömmliche Lithographieprozesse, wo für jede Schicht der Photolack und das gewünschte Material auf dem gesamten Substrat aufgebracht werden muss. Zusätzlich entfällt der selektive Belichtungsschritt sowie das chemische Ätzen des Photolacks bei m Lift-Off-Schritt. Dies reduziert die Anzahl der nötigen Prozessschritte, verringert den Materialeinsatz und die Menge des chemisch problematischen Abfall.[17]

Sowohl in der Forschung als auch in der Anwendung sind hybride gedruckte Bauteile bzw. Verfahren[13, 21] beliebt. Mit hybriden Bauteilen oder Schaltungen werden die Vorteile von Druckprozesstechniken wie eine hohe Geschwindigkeit eines Prozessschritts mit Vorteilen der herkömmlichen Lithographie wie der hohen Präzision kombiniert. Bei diesem Verfahren wird nur ein Teil des Bauteils bzw. einer Schaltung gedruckt, während die übrigen Teile bzw. Prozessschritte konventionell durchgeführt werden. Damit sind z.B. Forschungsarbeiten an einzelnen Aspekten von gedruckten Transistoren möglich, z.B. wenn die Halbleitereigenschaften untersucht werden sollen und deshalb der Halbleiter sowie Elektrolyt gedruckt, die Elektroden aber lithographisch hergestellt sind. Nachteil ist, dass die Herstellungskomplexität durch die Kombination von verschiedenen Herstellungsverfahren steigt.

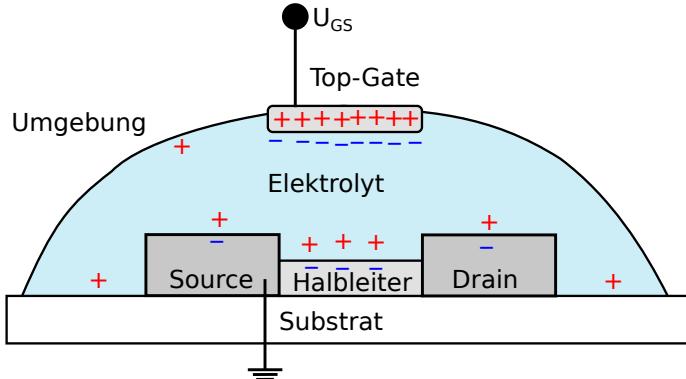

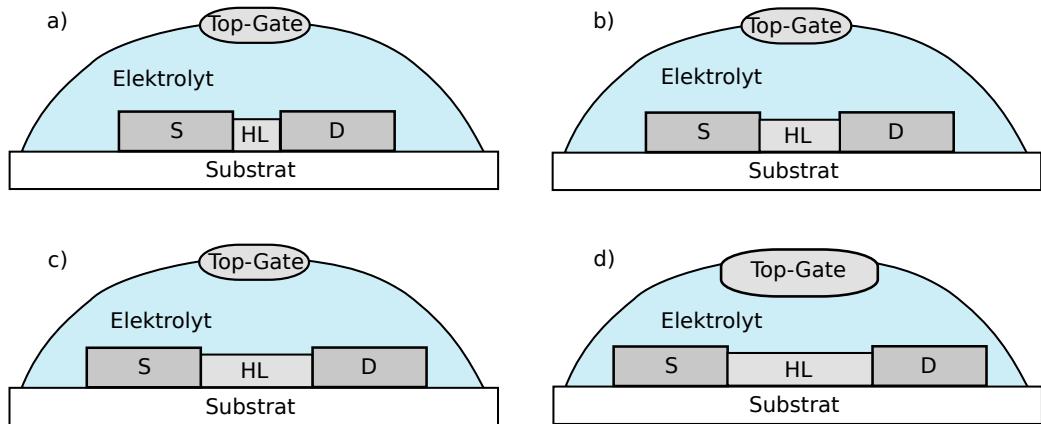

Unabhängig von der Herstellungsweise gibt es in Feldeffekttransistoren (FET) verschiedene Möglichkeiten den Gate-Kontakt auszubilden. In herkömmlich hergestellten Transistoren besteht der Gate-Kontakt aus einem elektrischen Leiter, der durch eine dünne Schicht eines Isolators (bzw. Dielektrikums) vom Halbleiter getrennt ist. Die Permittivität und Dicke des Dielektrikums sind dabei Tuningparameter für den Transistor. Daneben gibt es auch die Möglichkeit, einen Elektrolyt als Gate-Elektrode zu verwenden.[22] Dies ist z.B. in der gedruckten Elektronik beliebt, da Flüssigelektrolyte leichter in Druckverfahren prozessiert werden können als Dielektrika. Zusätzlich weisen

---

Elektrolyt-FETs eine große Gatekapazität auf, was niedrigere Betriebsspannungen im Vergleich zu gedruckten Dielektrikum-FETs ermöglicht.[23] Feldeffekttransistoren auf Elektrolytbasis werden als EGFET (*electrolyte gated field effect transistor*) bezeichnet. Außerdem werden Elektrolyte häufig in chemischen Sensoren als Sensor-Medium verwendet (ISFET, *ion sensitive field effect transistor*)[24, 25].

Das aktive Material in einem Transistor ist ein Halbleiter. Diese lassen sich in organische und anorganische Halbleiter unterteilen, die grundsätzlich beide auch gedruckt werden können. Während anorganische Halbleiter bessere elektronische Eigenschaften aufweisen[23], sind organische Halbleiter besser in Druckprozessen verwendbar[26–28] und werden bereits in Anwendungen wie OLEDs[29] und OPV[30, 31] erfolgreich genutzt. Anorganische Materialien werden erfolgreich in herkömmlich hergestellten Transistoren verwendet, haben im Bereich der gedruckten Elektronik bisher aber wegen Herausforderungen bei der Prozessierbarkeit trotz besserer elektrischer Eigenschaften die organischen Materialien noch nicht abgelöst. Sie zeigen im Forschungsbereich aber bereits vielversprechende Resultate.[23]

Es wäre deshalb von großem Nutzen, anorganische Halbleiter auch in gedruckter Elektronik weiter zu verbreiten. Dazu muss das Verständnis der anorganischen Halbleiter sowie der Funktionsweise eines gedruckten Transistors vertieft werden, um die Ausbeute bei der Herstellung sowie die Eigenschaften verbessern zu können. So sind z.B. die genauen Eigenschaften der Materialien im gedruckten Bauteil nicht zwangsläufig gleich denen des gleichen Materials außerhalb des Transistors. Die inneren Vorgänge wie räumliche Verteilung des elektrischen Stroms sind experimentell nicht zugänglich und deshalb weitgehend unbekannt. Die Schwellspannung (engl. *threshold voltage*, manchmal auch Threshold-Spannung), als charakteristische Größe eines Transistors, ist in gedruckten Elektrolyt-Transistoren im Akkumulationsbetrieb unverstanden. Modellierung und insbesondere die Unterkasse der physikalischen Simulationen ermöglichen es, diese und andere experimentell unzugänglichen Größen zu ermitteln und Informationen zu generieren.

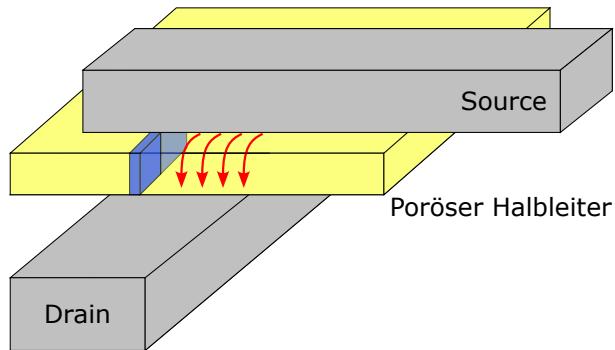

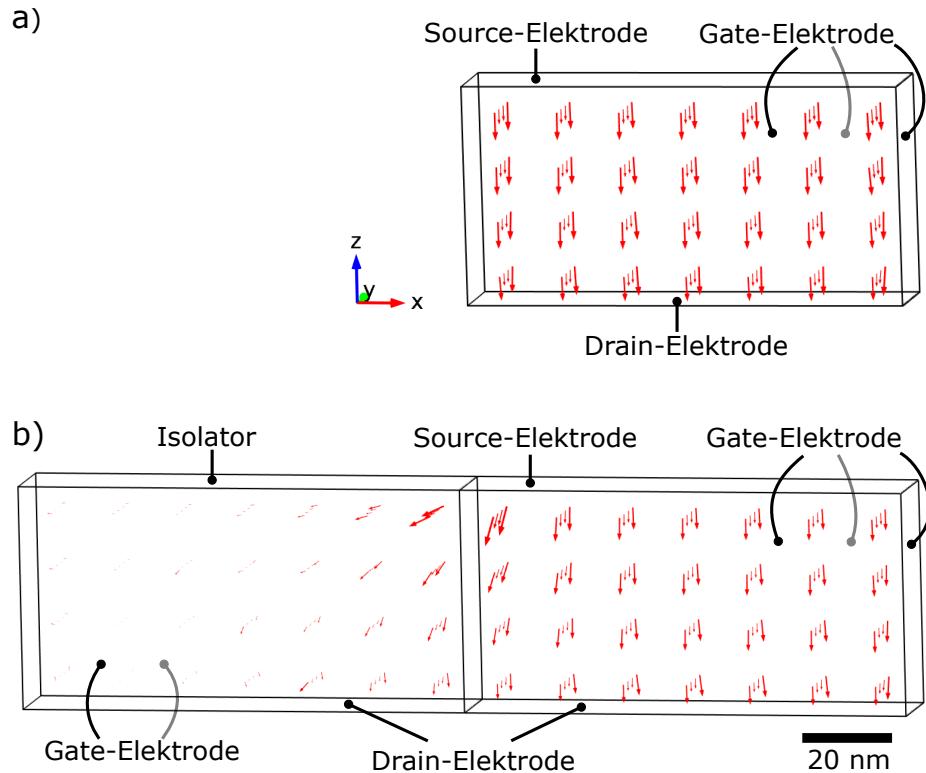

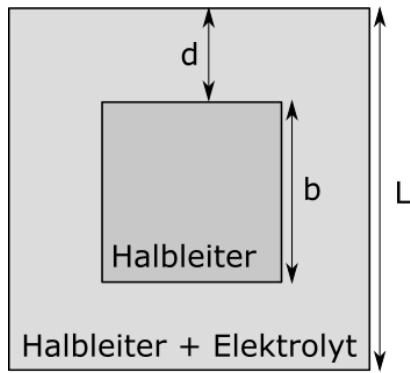

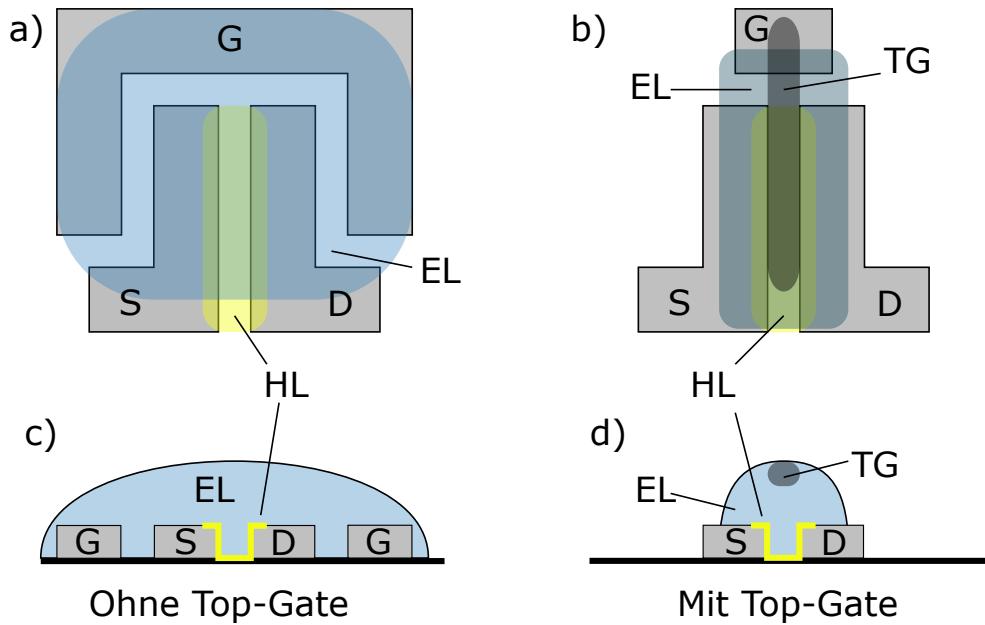

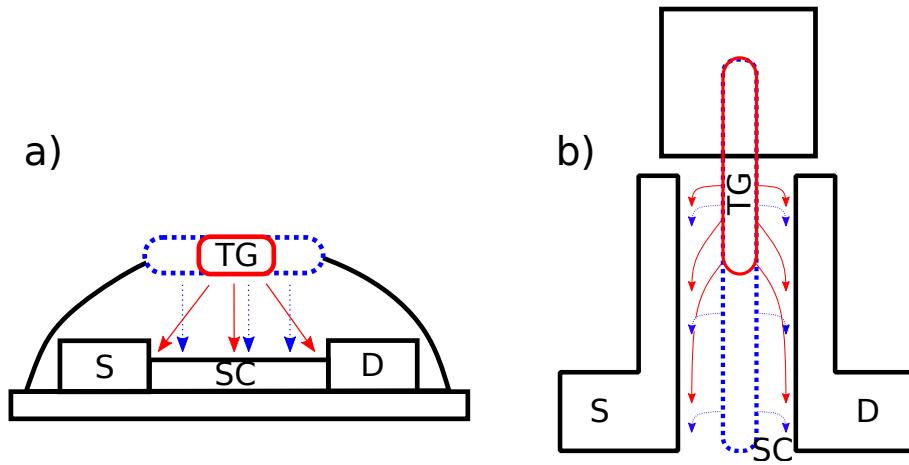

In dieser Arbeit untersuche ich die elektrischen Eigenschaften von gedruckten Transistoren und druckbaren Halbleitermaterialien. Für einen am Institut für Nanotechnologie (INT) von der Arbeitsgruppe Dasgupta/Breitung gedruckten vertikalen Feldeffekttransistor mit Elektrolyt-Gate (vFET, *vertical field effect transistor*) auf SnO<sub>2</sub>-Basis erstelle ich ein physikalisches Simulationsmodell (Top-down). Dieses Modell erlaubt als virtuelles Mikroskop Einblicke in den Ladungstransport und die Ausprägung der Leitungskanäle wie sie in einer mesoporösen Struktur vorherrscht. Darüber hinaus nutze ich das Modell um Vorhersagen der Eigenschaften wie der Schwellspannung bei modifizierten vFET zu erarbeiten und um z.B. den Größenordnung von Randströmen abzuschätzen.

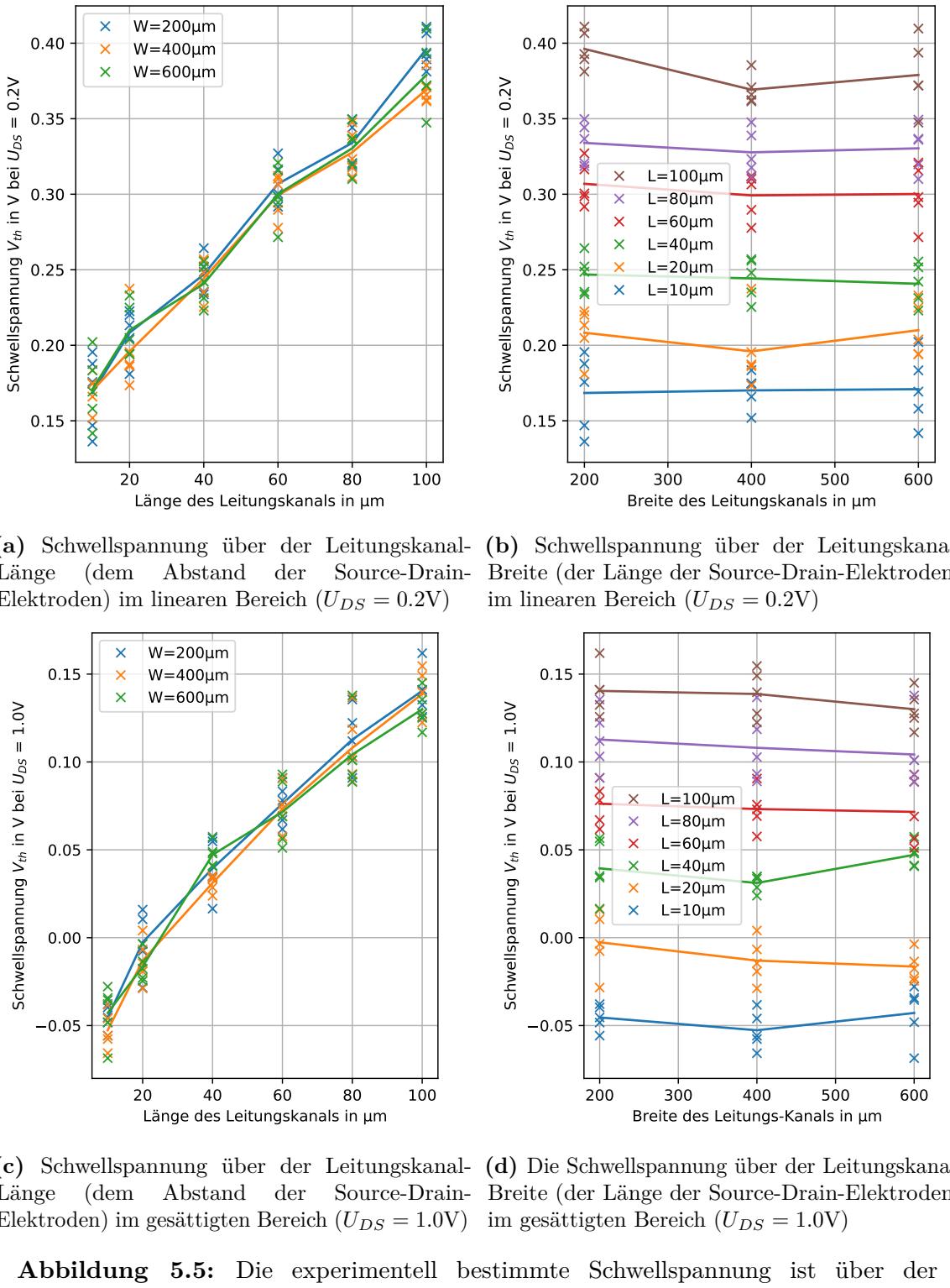

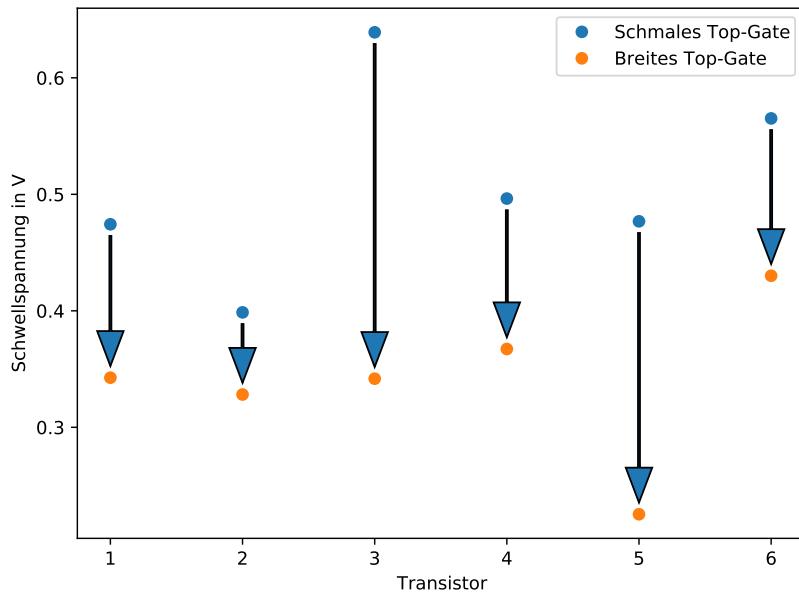

Ein weiterer am INT von der Arbeitsgruppe Aghassi-Hagmann gefertigter EGFET (planar, auf In<sub>2</sub>O<sub>3</sub>-Basis) zeigt im Experiment eine Schwellspannungsabhängigkeit von der Leitungsanallänge, aber nicht von der Leitungsanallänge. Damit lässt sich die Schwellspannung justieren und diese Transistoren für verschiedene Aufgaben in Schaltungen verwenden. Um einen Grund für die beobachtete Abhängigkeit zu ermitteln, entwickle ich in dieser Arbeit ein allgemeines Schwellspannungsmodell für beliebige Elektrolyt-FET. Es erklärt eine Abhängigkeit der Schwellspannung von

## 1 Einleitung

---

den Verhältnissen der Grenzschichtkapazitäten des Elektrolyt. Das Modell verknüpft erstmals physikalische Größen wie die Gatekapazität mit DC-Eigenschaften (zeitlich konstante Signale) eines EGFET statt wie bisher nur mit AC-Eigenschaften von zeitlich abhängigen Signalen. Mit diesem Bottom-up Modell lässt sich qualitativ die beobachtete Schwellspannungsabhängigkeit erklären und erlaubt die Diskussion von weiteren extern erstellten experimentellen Daten.

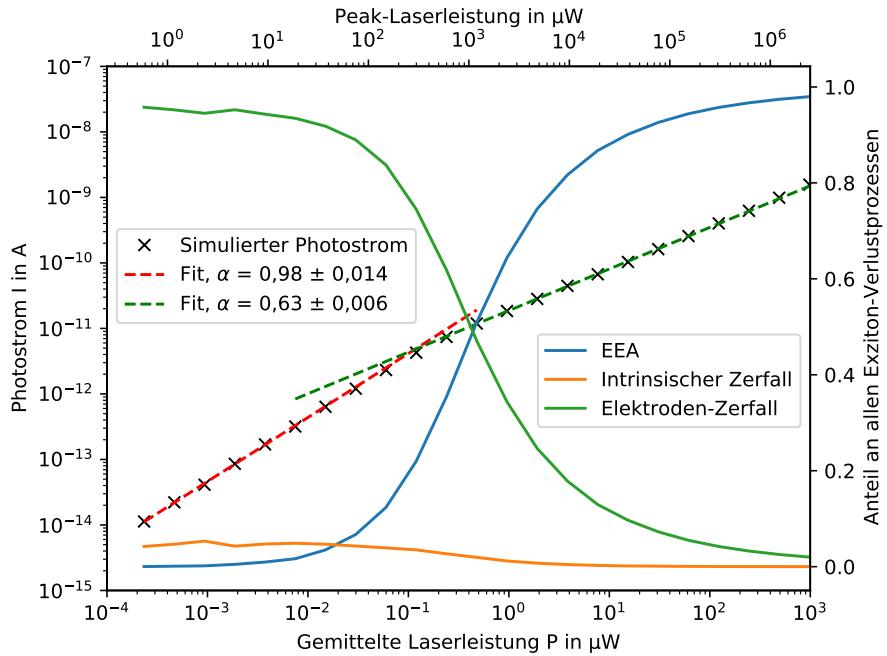

Neben den herkömmlichen druckbaren Materialien sind Kohlenstoffnanoröhrchen (CNT, *carbon nanotubes*) bzw. allgemein reine Kohlenstoffverbindungen eine weitere Klasse druckbarer (halb)leitender Materialien. Dort können Exzitonen den Stromfluss bzw. das Transportregime beeinflussen, was bisher nicht vollständig verstanden ist. In Zusammenarbeit mit der Arbeitsgruppe Krupke habe ich eine Simulationssoftware entwickelt, die die Diffusion und den Zerfall von gepulst erzeugten Photoexzitonen sowie den Stromfluss durch einen CNT simuliert. Durch einen Vergleich der Simulations- und Messergebnissen wird das Simulationsmodell geprüft. Das Simulationsmodell ermöglicht erstmals Einblicke darin, inwiefern eine gepulste Exzitonenerzeugung Einfluss auf die Charakteristik der Transportregimes hat und erlaubt es die relative Häufigkeit der verschiedenen Prozesse sowie den Einfluss der geometrischen Asymmetrie zu bestimmen.

Diese Arbeit ist in folgende Kapitel aufgeteilt. Die Grundlagen der Modelle und Systeme in dieser Arbeit fasse ich im folgenden Kapitel 2 zusammen. Anschließend stelle ich in Kapitel 3 die Simulationsmethoden vor, die in dieser Arbeit verwendet und teilweise entwickelt wurden. In Kapitel 4 diskutiere und präsentiere ich das Top-Down-Simulationsmodell sowie dessen Ergebnisse zum vFET. Ich prüfe und passe das Modell an experimentellen Daten an und nutze es, um die Stromdichte im Halbleiter zu untersuchen. Außerdem nutze ich das Modell um abzuschätzen, welche Eigenschaften vFET mit anderer Halbleitermorphologie und Dotierkonzentration haben. Zusätzlich prüfe ich mit einer gekoppelten Halbleiter-Elektrolyt-Simulation die verwendete Näherung, ob benachbarte Halbleiterdomänen voneinander unabhängig betrachtet werden können. Zuletzt nutze ich das Modell, um die Größenordnung und Wichtigkeit von Randströmen zu untersuchen. In Kapitel 5 entwickle ich ein allgemeines Bottom-up Modell für die effektive Schwellspannung (engl. *threshold voltage*) von Elektrolyt-Transistoren und definiere die makroskopische Schwellspannung als Funktion einer nur materialabhängigen mikroskopischen Schwellspannung sowie aller Grenzschichtkapazitäten des Elektrolyt. Das Modell wird zunächst qualitativ begründet und dann die Schwellspannung mathematisch hergeleitet. Anschließend diskutiere ich das Modell zu verschiedenen extern erstellten Messreihen von planaren gedruckten Elektrolyt-Transistoren. In Kapitel 6 stelle ich die Simulationen des Photostroms in einem gepulst angeregten Kohlenstoffnanoröhrchen vor und vergleiche die Ergebnisse mit dem Experiment, um die Validität des Modells zu prüfen. Anschließend analysiere ich die bereits vorher extern experimentell gefundenen verschiedenen Transportregimes und untersuche die Relevanz eines asymmetrischen Beleuchtungsprofils. Alle Ergebnisse dieser Arbeit fasse ich in Kapitel 7 zusammen und gebe einen Ausblick zu weiteren Forschungsfragen.

## 2 Grundlagen

### 2.1 Gedruckte Transistoren/Elektronik

Elektronik und insbesondere Transistoren zu drucken ist eine komplementäre Herstellungsweise zu herkömmlichen (teuren und aufwändigen) Lithographieverfahren. Gedruckte Transistoren bzw. Elektronik allgemein ist dabei eine Klasse von Bauteilen, bei denen das gesamte Bauteil oder auch nur ein Teil davon mit Druckmethoden hergestellt wird. Druckprozesse sind grundsätzlich additiv, was den Materialeinsatz niedrig hält. Der Druckprozess bietet gegenüber herkömmlicher Lithographie einige Vorteile. Zum einen ist die Auswahl an Substratmaterialien größer und beinhaltet auch flexible Materialien wie Papier[32], Folie[33] oder Textilien[34]. Flexible Substrate sind mit herkömmlicher Silizium-Technik nur sehr aufwändig durch Ausdünnen des Substrats möglich[35]. Zusätzlich bieten Drucktechniken einen Gegenpol zu modernen Lithographie-Verfahren, die einen extremen Material- und Technologieeinsatz erfordern. Herkömmliche Druckverfahren wie Sieb-, Offset-, Hoch- und Tiefdruck sind etablierte Verfahren und erlauben Druckgeschwindigkeiten der Größenordnung m/s[33], was auch die Produktionskosten senkt. Dabei kann ein Rolle-zu-Rolle-Verfahren verwendet werden, wo das Substrat von einer Rolle kontinuierlich abgewickelt, durch die Druck- und Prozessiermaschinen transportiert und als fertiges (Zwischen-) Produkt wieder aufgerollt wird. In gedruckter Elektronik müssen gegenüber modernen DUV- und EUV-Prozessen Abstriche bei der Performance der Transistoren gemacht werden, da die Größe der Bauteile in Lithographieprozessen um Größenordnungen kleiner ist.

Die verwendeten Materialien lassen sich in organisch und anorganisch einteilen. Organische Materialien (insbesondere Halbleiter) sind etabliert in Forschung und Industrie. Die Elektronenmobilität ist in organischen Materialien allerdings wegen des fehlenden Bandtransports und der üblicherweise amorphen Struktur um 1-2 Größenordnungen geringer. Anorganische Materialien wie Metalloxide weisen höhere Mobilitäten von ca.  $200 \frac{\text{cm}^2}{\text{V}\cdot\text{s}}$  auf, was sie vielversprechend für eine neue Generation von gedruckter Elektronik macht. Das Gate kann bei gedruckter Elektronik sowohl über ein Dielektrikum als auch über einen Elektrolyt (flüssig oder fest) verbunden werden.

Bei anorganischen gedruckten Halbleitern gibt es zwei Ansätze, wie das Material zu einem funktionsfähigen Halbleiter prozessiert werden kann. In der direkten Form werden Nanopartikel in der Drucktinte gelöst und gedruckt. Das Lösungsmittel verdampft und die Nanopartikel bleiben als poröse Struktur zurück. Dies ist vor allem bei empfindlichen Substraten relevant, da keine hohen Temperaturen nötig sind. Alternativ kann ein sog. Precursor gedruckt werden. Dies ist ein chemischer Stoff, der als Edukt für eine chemische Reaktion dient. Diese Reaktion wird nach dem Druckprozess durch

Ausheizen des Precursors gestartet. Der Precursor reagiert dabei zum eigentlichen Halbleiter. Vorteil ist, dass die dabei entstehenden polykristallinen Strukturen bessere elektronische Eigenschaften aufweisen, da die Atome beim Ausheizen mobil sind und sich lokal umordnen können. Allerdings ist nicht jedes Substrat beständig für die nötigen Ausheiztemperaturen.

Vollständig gedruckte Transistoren sind bereits realisiert worden.[36] Häufig werden allerdings Druck- und herkömmliche Lithographieprozesse vereint zu teilweise gedruckten bzw. hybriden Transistoren. Sie können Vorteile beider Seiten vereinen.

## 2.2 Feldeffekttransistoren

In diesem Abschnitt wird der Aufbau, die Funktionsweise, Eigenschaften und kurz die Geschichte von Feldeffekttransistoren vorgestellt. Der Inhalt basiert auf dem Buch von Sze und Ng[37], auf das auch für detailliertere und weiterführende Informationen verwiesen wird.

Transistoren sind elektronische Halbleiterbauteile, die es ermöglichen einen Strom durch eine Eingangsspannung oder einen Eingangsstrom zu steuern. Feldeffekttransistoren sind eine Unterkategorie der Transistoren, die einen hochohmigen Eingang besitzen, damit spannungsgesteuert sind und auf dem elektrischen Feldeffekt basieren. Dieser besagt, dass die elektrische Leitfähigkeit eines Halbleiters durch ein äußeres elektrisches Feld gesteuert werden kann.

Feldeffekttransistoren sind Nachfolger bzw. Weiterentwicklungen der Triode bzw. Vakuumröhre. Sie wurden konzeptionell bereits 1925 von Julius Edgar Lilienfeld postuliert. Während zunächst Bardeen, Shockley und Brattain 1956 den Physik-Nobelpreis für den Bipolartransistor erhielten, gelang es Mohamed Atalla und Dawon Kahng 1959 in den Bell Labs den ersten MOSFET zu erstellen. Bis heute ist der MOSFET (bzw. allg. der IGFET, *insulated gate field effect transistor*) das vermutlich am häufigsten von der Menschheit hergestellte Bauteil. Insbesondere in der Digitaltechnik werden MOSFETs z.B. im CMOS-Verfahren bzw. -Schalttechnik als Grundbausteine für Logikgatter verwendet. Der Vorteil ist, dass in der CMOS-Technik (abgesehen von Leckströmen) Strom nur beim Umschalten der Transistoren fließt, da über eine Ladungsveränderung am Gate nur ein elektrisches Feld im Halbleiter verändert werden muss.

Halbleiter erlauben es, über ihre Dotierung mit Elektronenakzeptoren oder -donatoren ihre elektrischen Eigenschaften zu verändern. Die thermische Energie ionisiert dabei die Dotierstellen, die ein freies Loch (p-Dotierung) bzw. Elektron (n-Dotierung) freigeben und eine negative bzw. positive ortsfeste lokalisierte Ladung zurücklassen.

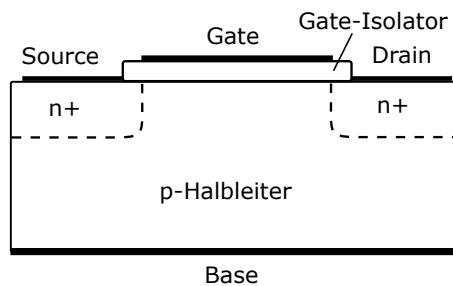

Um das herkömmliche Funktionsprinzip eines Inversions-FET zu erklären, ist in Abb. 2.1 schematisch ein planarer MOSFET dargestellt. Zwischen Source- und Drain-Elektrode ist eine Spannung angelegt. Der Source/Drain-Strom ist dann durch die Leitfähigkeit des Halbleiters definiert. Die Gate-Elektrode ist durch eine Isolator-Schicht (z.B. ein Oxid) vom Halbleiter abgetrennt. Im hier dargestellten Fall ist der Halbleiter p-dotiert mit einer zusätzlichen n-Dotierung um die Source-Drain-Elektroden. Ohne Gatespannung liegt zwischen der Source/Drain-Elektrode ein npn-Übergang vor, der sowohl

**Abbildung 2.1:** Schematische Darstellung eines n-leitenden MOSFET (bzw. allgemein IGFET) mit p-Halbleiter.

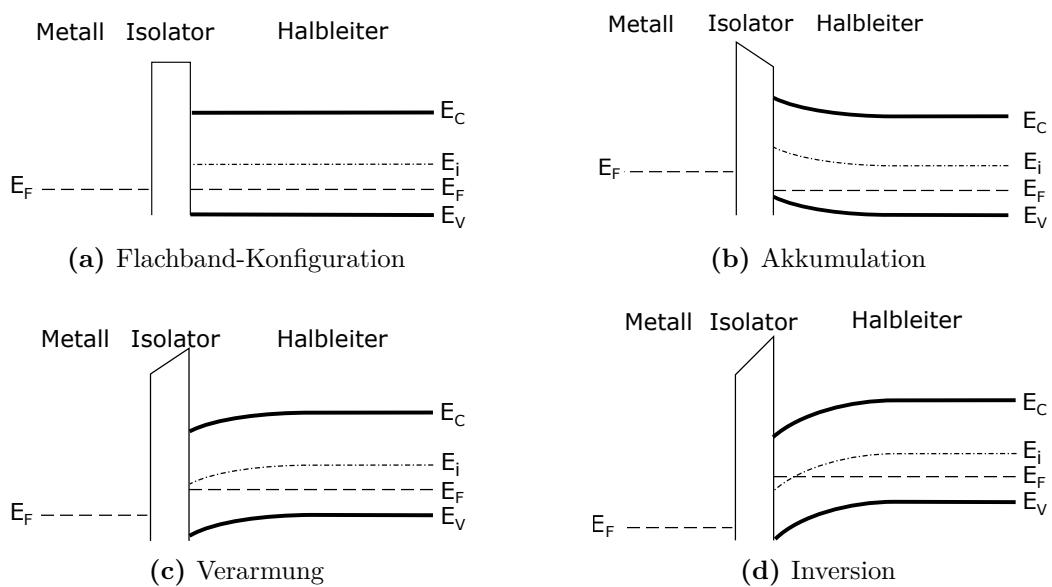

**Abbildung 2.2:** Banddiagramme eines Metall-Isolator-Halbleiters (p-dotiert) für verschiedene Potentialunterschiede zwischen Metall und Halbleiter

bei positiven als auch bei negativen Source/Drain-Spannungen den Strom blockiert. Bei einer positiven Gatespannung lädt sich die Gateelektrode auf und erzeugt ein elektrisches Feld, das die Bänder im Halbleiter verschiebt. Zunächst werden im Halbleiter durch eine kleine positive Gatespannung die Majoritätsladungsträger (Löcher, da p-dotiert) reduziert (engl. depletion). Bei höherer Gatespannung kommt es zur Inversion, es werden vom elektrischen Feld so viele Minoritätsladungsträger (hier Elektronen) erzeugt, dass mehr Minoritäts- statt Majoritätsladungsträger zur Verfügung stehen. Es bildet sich also im Halbleiter an der Gateisolatorschicht eine dünne Schicht an Elektronen aus, der sog. Leitungskanal. Dieser verbindet die n-dotierten Bereiche um die Source/Drain-Elektroden. Damit existiert eine durchgehende Verbindung zwischen den Elektroden mit Elektronenüberschuss ohne pn-Übergänge, sodass der Source-Drain-Strom um Größenordnungen ansteigt.

Die möglichen Betriebszustände eines Inversions-FET lassen sich auch an Hand der Banddiagramme des Halbleiters am Gatekontakt erklären. Dazu sind in Abb. 2.2 Banddiagramme eines p-dotierten Halbleiters für verschiedene Gatespannungen

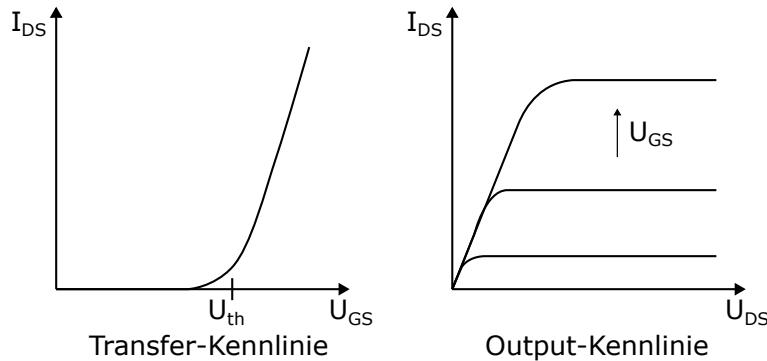

**Abbildung 2.3:** Beispielhafte Transfer- und Outputkennlinien eines n-leitenden MOSFET. Aus Transferkennlinien lässt sich die Schwellspannung  $U_{th}$  ermitteln und zeigt die nichtlineare Abhängigkeit des Source-Drain-Stroms von der Gatespannung. Die Outputkennlinie zeigt verschiedene Regimes. Bei niedrigen Source-Drain-Spannungen steigt der Strom linear mit der Spannung an, erreicht dann einen sublinearen Bereich und endet in einen charakteristischen Sättigungsbereich.

dargestellt.  $E_{C/V}$  bezeichnet die Leitungs- bzw. Valenzbandkante,  $E_F$  das (Quasi-)Ferminiveau und  $E_i$  das intrinsische Niveau, das ein undotierter Halbleiter bei dieser Temperatur hätte. Physikalisch entspricht diese Betrachtung einem Metall-Isolator-Halbleiter-Kondensator, wie er in der Literatur oft als Grundlage für die Diskussion eines FET bei vernachlässigbarer Source-Drain-Spannung herangezogen wird. ([37], Kap. 4) Im einfachsten Fall (Abb. 2.2a) ist die Gatespannung so eingestellt, dass die Bänder im Halbleiter eben sind ( $U_G = U_{fb}$ , flat band). Die Ladungsträgerdichte  $p(x, U_G)$  ist im Halbleiter homogen und entspricht der Dotierung  $p_0$ . Wird eine niedrigere Gatespannung  $U_G < U_{fb}$  angelegt, nähert sich das Fermi-Niveau an das Valenzband, die Lochdichte steigt ( $p > p_0$ ) und die Elektronendichte sinkt. Dies wird der Akkumulationsmodus genannt (Abb. 2.2b), da die Dichte der Dotierungs-Ladungsträger erhöht wird. Bei einer höheren Gatespannung ( $U_G > U_{fb}$ ) (Abb. 2.2c) nähert sich das Fermi-Niveau zunächst dem intrinsischen Energieniveau, sodass die Lochdichte sinkt (Verarmung, engl. depletion). Schneidet das Ferminiveau das intrinsische Niveau, kommt es zur Ladungsträgerinversion (Abb. 2.2d), d.h. die Elektronendichte liegt jetzt über der Lochdichte ( $n > p$ ). Die Inversion lässt sich in zwei Unterbereiche einteilen, die durch die sog. Schwellspannung  $U_{th}$  (engl. threshold voltage) getrennt sind. Bei der Schwellspannung ist die Elektronenkonzentration direkt an der Gateelektrode  $n(0, U_G)$  gleich der Dotierkonzentration  $p_0$ , sie trennt makroskopisch den Aus- vom Ein-Zustand des FET. Gilt  $U_{fb} < U(G) < U_{th}$ , so ist die Elektronendichte niedriger als die Dotierdichte der Löcher ( $n(0, U_G) < p_0$ ) und der Halbleiter in der sog. schwachen Inversion. Ist die Gatespannung höher ( $U_G > U_{th}$ ), befinden sich durch die Inversion mehr Elektronen als Löcher nahe am Gatekontakt und der Halbleiter ist in der starken Inversion. In diesem Fall ist bereits ein Ladungskanal ausgebildet.

Für FET gibt es zwei Arten von charakteristischen Kennlinien. Zum einen kann der Source-Drain-Strom über die Gatespannung bei konstanter Source-Drain-Spannung (Transfer-Kennlinie) und zum anderen der Source-Drain-Strom über die Source-Drain-Spannung bei konstanter Gatespannung (Output-Kennlinie) aufgetragen werden.

Deren schematischer Aufbau ist in Abb. 2.3 dargestellt. In Transferkennlinien ist die Schaltcharakteristik von FET sichtbar. Im Off-Zustand ist der Source-Drain-Strom klein gegenüber dem On-Zustand. Dieser steigt bei Erreichen der Schwellspannung  $U_{th}$  abrupt an. In Outputkennlinien sind drei Regimes zu erkennen. Im linearen Regime bei kleinen Source-Drain-Spannungen steigt der Source-Drain-Strom linear mit der Spannung. Dann fällt die Abhängigkeit sublinear ab und erreicht schließlich den Sättigungsbereich, in dem der Strom konstant ist. Dass der Strom trotz steigender Source-Drain-Spannung nicht weiter ansteigt, liegt am sog. *pinch-off*-Effekt. Der Leitungskanal erstreckt sich dann nicht mehr über die gesamte Source-Drain-Strecke, sondern es gibt einen nur schwach leitenden Bereich mit niedriger Ladungsträgerdichte. Die Länge dieses Bereichs steigt mit der Source-Drain-Spannung, sodass die höhere Source-Drain-Spannung kompensiert wird.

FETs können eine Vielzahl von Kenngrößen zugewiesen werden, die die elektrischen Eigenschaften beschreiben und bei der Auswahl in elektronischen Schaltungen wichtig sind. Im Folgenden werden einige für diese Arbeit relevante Größen beschrieben.

- **Schwellspannung** Wie oben beschrieben trennt diese Spannung den Aus vom An-Zustand. In herkömmlichen Inversions-FET fällt dies mit dem Beginn der starken Inversion zusammen. Diese strenge Definition über mikroskopische Eigenschaften kann verallgemeinert werden auf Akkumulations-FET und andere Transistoren, indem die Nichtlinearität der Transferkurven ausgewertet wird.[38]

- **On-Stromstärke** Diese Größe ist insbesondere für Leistungselektronik wichtig und gibt an, wie groß der maximale Source-Drain-Stromfluss ist. Analog kann auch die Leitfähigkeit statt der Stromstärke als Kenngröße verwendet werden.

- **On/Off-Verhältnis** Das Verhältnis gibt an, wie stark On- und Off-Zustand eines FET voneinander getrennt sind und ist für die Eignung in digitalen Schaltungen bedeutend.

- **Subthreshold slope** Im Off-Zustand verhält sich der Source-Drain-Stromfluss exponentiell mit der Gatespannung. Der dazugehörige Exponent (bzw. Steigung in log. Darstellung) ist ein Maß dafür, wie schnell der Transistor zwischen On- und Off-Zustand schalten kann.

Über die Dotierung des Bulks und der Elektrodenbereiche des Halbleiters können die Eigenschaften des Transistors beeinflusst werden. Damit können insgesamt vier Regimes eingestellt werden, über die sich auch vier Schalteigenschaften definieren lassen. Diese beziehen sich dabei einmal auf den Schaltzustand ohne angelegte Gatespannung, der entweder leitend oder sperrend sein kann (engl. *normally on* und *normally off*). Sperrend sind dabei üblicherweise Transistoren mit unterschiedlicher Dotierungsart des Bulk und der Elektrodengebiete (durch sperrende npn-Übergänge), leitend wenn die Bereiche gleich dotiert sind. Zusätzlich besagt die Dotierung des Bulk, ob der absolute Stromfluss mit der Gatespannung steigt oder fällt. Ist der Halbleiter p-dotiert, steigt seine Leitfähigkeit mit der Gatespannung (n-leitend), bei n-Dotierung sinkt er mit höheren Gate-Spannungen (p-leitend). Die dazugehörigen

**Abbildung 2.4:** Schematische Darstellung von vier Transferkennlinien. Oben sind elektronenleitende FET (wo eine höhere Gatespannung zu mehr Stromfluss führt), unten lochleitende FET mit umgekehrter Charakteristik abgebildet. Links sind die Transistoren normally-off, d.h. der FET sperrt bei einer Gatespannung von 0 V. Rechts sind die FET bei 0 V Gatespannung leitend und können mit einer niedrigeren bzw. höheren Gatespannung gesperrt werden.

Transferkennlinien sind in Abb. 2.4 dargestellt. Auch bei anderen Transistorarten bleiben diese grundsätzlichen Kennlinientypen erhalten. Sie sind universell für die Beschreibung der Eigenschaften eines Transistors.

Es existieren auch vereinfachte Transistoren ohne pn-Übergang. Diese werden im sog. Akkumulations-Modus betrieben. Im Gegensatz zum Inversionsmodus ist der Typ des dominanten Ladungsträgers im Leitungskanal gleich der Hintergrunddotierung. Es entfällt die Notwendigkeit für extra dotierte Bereiche an den Source/Drain-Elektroden, was die Herstellung vereinfacht.

Alle bisher genannten Eigenschaften basieren auf der Annahme von einer hohen Leitungskanallänge, wo Effekte von den Source-Drain-Elektroden vernachlässigt werden können. Wenn sie doch eine Rolle spielen, werden sie engl. *short channel effects* genannt. Z.B. kann das elektrische Feld der Drain-Elektrode auch den Halbleiter an der Source-Elektrode beeinflussen (*drain induced barrier lowering*). In Elektrolyt-FET spielen diese wegen der hohen Gatekapazität keine signifikante Rolle.[39]

## 2.3 Elektrochemische Doppelschicht

Wenn ein (halb-)leitender Festkörper mit einem Elektrolyt in Kontakt kommt, kann sich abhängig von den elektrischen Potentialen am Kontakt eine sog. *elektrochemische Doppelschicht* (auch elektrolytische Doppelschicht oder Doppelschicht) ausbilden. Sie tritt auf, weil eine solche Grenzschicht eine Phasengrenze zwischen elektrischen Leitern unterschiedlicher Klasse ist. Im elektrisch (halb-)leitenden Feststoff findet Stromfluss durch Elektronen statt, sie sind deshalb Leiter 1. Klasse. In einem Elektrolyt bewegen

sich Ionen als ganze geladene Teilchen durch das Medium, ein Elektrolyt ist deshalb ein Leiter 2. Klasse. Die Nettoladungen der Anionen und Kationen heben sich gegenseitig auf.

Die Ladungsseparation in einer Doppelschicht führt zu einer Kapazität, die der Doppelschicht zugewiesen wird. Die Kapazität wird dabei wie in einem herkömmlichen Plattenkondensator durch die Ladungsmenge sowie den Abstand der Ladungen definiert. Es existieren eine Vielzahl von qualitativen und quantitativen Modellen für die Ladungsdichte im Elektrolyt abhängig vom Abstand zur Grenzfläche, von denen einige nun vorgestellt werden sollen. Für genauere Diskussionen wird auf die Literatur[40] verwiesen, auf der auch dieser Abschnitt basiert.

Als **Helmholtz-Doppelschicht** wird das Modell bezeichnet, das Hermann von Helmholtz 1879 erstellte.[41] Dort wird im Elektrolyt eine Monolage von Ionen an der Grenzschicht angenommen, die alle den gleichen Abstand zur Grenzschicht haben. Das elektrische Potential fällt zwischen den Gegenladungen in der Elektrode und der Monolage der Ionen im Elektrolyt ab und ist ansonsten konstant. Unberücksichtigt bleiben thermische Bewegungen der Ionen, Abschirmeffekte sowie Multilagen der Ionen.

Eine andere Beschreibung ermöglicht das **Gouy-Chapman-Modell**. Dort sind die Ionen als rein diffuse Ladungsschicht nahe der Grenzschicht Boltzmann-verteilt, nehmen also exponentiell mit dem Abstand zur Grenzschicht ab. Unberücksichtigt bleiben z.B. die tatsächliche Größe der (hydratisierten) Ionen, sodass das das Gouy-Chapman-Modell nur bei sehr kleinen Ionendichten und Potentialdifferenzen gilt. Mit diesem Modell verwandt ist die **Poisson-Boltzmann-Gleichung**, in die Ladungsträgerdichten einfließen. Sie verknüpft das elektrische Potential  $\Phi$  mit der Elementarladung  $q$ , der Permittivität  $\epsilon\epsilon_0$ , der Boltzmannkonstante  $k_B$ , Temperatur  $T$ , Ionenladungszahl  $z_i$  und der Bulk-Ionendichte  $n_{i,0}$

$$\nabla^2 \Phi(\vec{r}) = -\frac{e}{\epsilon\epsilon_0} \sum_i z_i n_{i,0} \exp\left(-\frac{ez_i\Phi(\vec{r})}{k_B T}\right) \quad (2.1)$$

Die Lösung dieser Differentialgleichung ist das elektrische Potential abhängig vom Ort. Weitere Parameter sind die Temperatur und die Ionenkonzentrationen und -ladungen.

Eine Kombination der beiden Modelle beschreibt das Stern-Modell[42] von 1924. In ihm weisen Ionen eine endliche Größe auf, sodass die Ladung nicht beliebig nah an die Grenzschicht gelangen kann. Unmittelbar an der Grenzschicht entspricht das Modell demnach dem Helmholtz-Modell. Weiter im Elektrolyt fällt die Nettoladungsdichte wie im Gouy-Chapman-Modell exponentiell ab.

Eine weitere Möglichkeit ist, mittels der Newtonschen Bewegungsgleichungen die Trajektorien der Ionen in einem kleinen Voxel zu simulieren (Molekulardynamik-Simulation, MD) und dabei die mittlere Ionendichten für An- und Kationen zu bestimmen. Dabei sind drei Schichten zu erkennen[43, 44], wo zwischen einem inneren Helmholtz-Layer (IHL, Lösungsmittelmoleküle), einem äußeren Helmholtz-Layer (OHL, Ionen mit Hydrathülle) und einer diffusiven Schicht unterschieden wird. Die Helmholtz-Schichten basieren dabei auf adsorbierten Ionen [45] Es existieren auch Modelle, die speziell auf bestimmte Systeme wie z.B. ionensensitive Transistoren abgestimmt sind. [46]

## 2.4 Elektrolyt als Gatekontakt

Bereits 1947 hatten Gibney und Brattain die Idee, einen Elektrolyt als Gatekontakt zu verwenden um Oberflächenzustände und -oxidierung zu verhindern.[47] Wegen der einfacheren Prozessierbarkeit, Reproduzierbarkeit und Langlebigkeit setzten sich später allerdings FET mit Dielektrikum als Gateisolator durch.

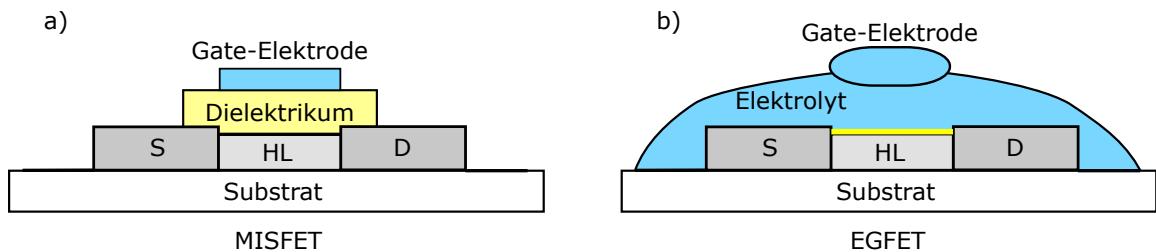

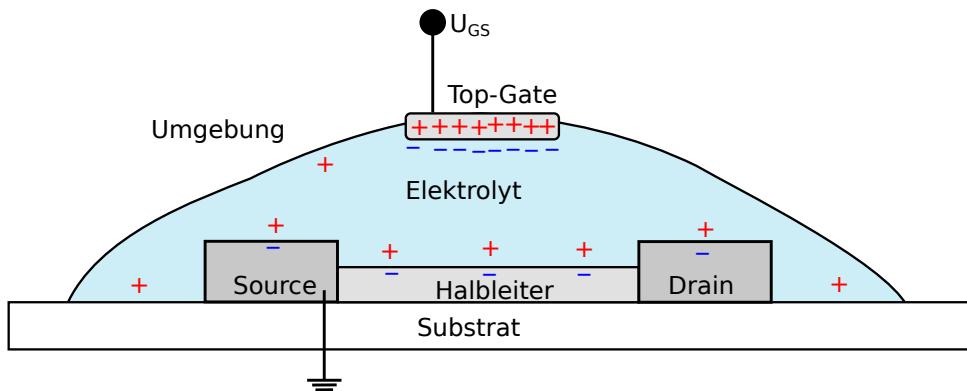

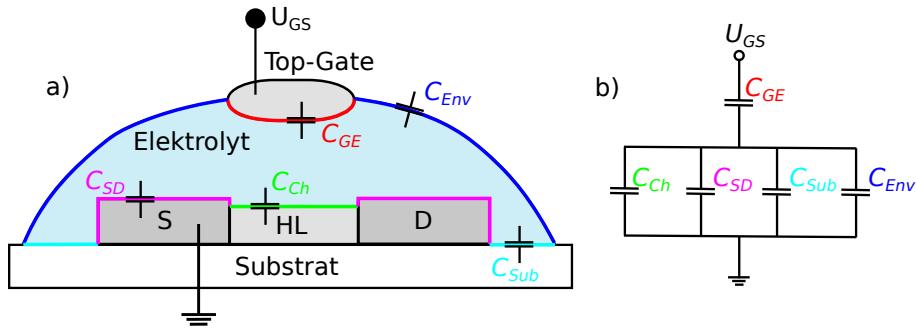

Allerdings hat ein mit einem Elektrolyt verschaltetes Gate bei FETs auch einige Vorteile. Zum einen werden Elektrolyttransistoren für chemische Sensoren verwendet (ISFET, *Ion sensitive field effect transistor*).[48] Außerdem weist ein Elektrolyt-Gate gegenüber einem Metall-Isolator-Gate eine größere Gate-Kapazität auf, was die erforderlichen Gatespannungen verringert.[49, 50] Der Grund für die größere Kapazität ist in Abb. 2.5 dargestellt, wo ein MISFET (*metal insulator semiconductor FET*, verallgemeinerter MOSFET) und ein EGFET (*electrolyte gated FET*) verglichen werden. In einem MISFET (2.5a) isoliert ein Dielektrikum die Gate-Elektrode vom Halbleiter. Die Gate-Spannung erzeugt ein elektrisches Feld, das im Halbleiter zum Feldeffekt führt. Die Dicke des Dielektrikums bestimmt die Gatekapazität (wie im Plattenkondensator der Plattenabstand) und die Stärke des elektrischen Felds. Im EGFET (2.5b) wird geometrisch das Dielektrikum durch einen Elektrolyt getauscht. Durch diese Änderung ändert sich die Gate-Verschaltung des EGFET fundamental. Der Elektrolyt ist im Gegensatz zum Dielektrikum kein Isolator, sondern ein elektrischer Leiter (Ionenleitung). Dieser ist über die Gate-Elektrode/Elektrolyt-Grenzschicht kapazitiv (sofern keine bzw. vernachlässigbar wenige Redox-Reaktionen stattfinden) an die Gatespannung gekoppelt und ist im inneren (im Gleichgewicht) feldfrei. Mathematisch ist die elektrische Permittivität im Dielektrikum endlich, im Elektrolyt (im Falle eines idealen elektrischen Leiters) unendlich groß. Die Rolle des Gate-Isolators übernimmt im Elektrolyt-FET nun kein geometrisches Element, sondern intrinsisch der isolierende Übergang von Ionenleitung im Elektrolyt zu Elektronenleitung im Halbleiter. Ist der Spannungsabfall an der Grenzschicht klein, finden keine chemischen Reaktionen und damit kein Ladungsübertritt statt und die Grenzschicht isoliert. Der Abstand der Ladungen an dieser Grenzschicht ist minimal, da es sich um einen Grenzflächeneffekt ist. Die Gatekapazität ist damit groß (z.B.  $4,33 \mu\text{F}/\text{cm}^2$  von Garlapati *et al.*[51]), was die erforderlichen Gatespannungen in den Bereich  $\leq 1 \text{ V}$  verringert. Dies ist 1-2 Größenordnungen niedriger als für gedruckte Dielektrikum-FET.[52]

In der Realität ist ein Elektrolyt und insbesondere ein Festkörperelektrolyt kein perfekter elektrischer Leiter, es ist denkbar dass sich voneinander isolierte Domänen im Elektrolyt ausbilden. Die Größe der elektrisch leitfähigen Domänen beschreibt dann, ob der reale Elektrolyt sich wie ein idealer Elektrolyt (große Domänen) oder wie ein Dielektrikum verhält (Extremfall Domänengröße gleich Atomdurchmesser, sodass es nur zur elektrischen Verschiebung kommt). Die oben genannte Gatekapazität in der Größenordnung von einigen  $\mu\text{F}/\text{cm}^2$  deutet auf ein Verhalten nahe eines idealen Elektrolyt hin.[53]

Neben der hohen Gatekapazität hat ein Elektrolyt weitere Vorteile. Im Gegensatz zum Dielektrikum spielt die Ausrichtung der Elektrodenflächen zueinander beim Elektrolyt keine Rolle. Eine Gatespannung an einem Elektrolyten überträgt sich homogen auf sämtliche Gegenflächen unabhängig von ihrer Orientierung, da das

**Abbildung 2.5:** Schematische Schnittabbildungen eines FET mit Dielektrikum und eines FET mit Elektrolyt statt Dielektrikum. Die Farben zeigen jeweils identische funktionelle Einheiten. a) zeigt einen MISFET (*metal-insulator-semiconductor FET*), in dem ein Dielektrikum die Gate-Elektrode vom Halbleiter isoliert und die Spannungsschaltung des FET ermöglicht. Die Dicke des Dielektrikums beeinflusst wie in einem Plattenkondensator das von der Gatespannung erzeugte elektrische Feld im Halbleiter. b) zeigt den analogen Aufbau eines EGFET (*electrolyte gated FET*), in dem das Dielektrikum durch einen Elektrolyt ersetzt wurde. Physikalisch ist der Elektrolyt (als elektrischer Leiter) eine kapazitiv gekoppelte Verlängerung der Gate-Elektrode. Die eigentliche Rolle des Gate-Isolators übernimmt intrinsisch der Übergang von Ionen- zu Elektronenleitung an der Elektrolyt-Halbleiter-Grenzschicht. Die Dicke dieser elektrochemischen Doppelschicht übernimmt die Rolle der Dicke des Dielektrikums im MISFET und liegt im Bereich von einigen Atomradien bis wenigen nm, was niedrige Betriebsspannungen von EGFET ermöglicht.

Innere des Elektrolyt im Gleichgewicht feldfrei ist. Raue bzw. poröse Oberflächen lassen sich durch flüssig prozessierte Elektrolyte gut benetzen und verschalten.

## 2.5 Metalloxide

Metalloxide sind chemische Verbindungen von Metallen mit Sauerstoff und im Überfluss in der Erdkruste verfügbar.[54, 55]. Der Sauerstoff hat dabei immer die Oxidationsstufe -2. In der Praxis werden Metalloxide (wegen der vielfältigen Kombinationsmöglichkeiten der Elemente) als elektrische Leiter, Halbleiter und Isolatoren verwendet. Insbesondere optisch transparente (Halb)leiter sind in der Technik von großem Interesse für Bildschirme und Solarzellen.[56]

Charakteristisch für Metalloxide sind die elektronischen Eigenschaften der Materialien, die zusammen mit einer großen Bandlücke allgemein eine höhere Elektronenmobilität im Vergleich zur Lochmobilität aufweisen.[56, 57] Die p-Orbitale des Sauerstoffs sind wegen ihrer räumlichen Anisotropie empfindlich gegen Verschiebungen (z.B. durch Kristallfehler, Fehlstellen, Korngrenzen), da die keulenförmigen Orbitale räumlich überlappen müssen um wechselwirken zu können. Das bedeutet, dass die p-Orbitale des Sauerstoffs im Festkörper abhängig von der Anordnung der Atome nicht in jedem Fall so gut delokalisieren wie die radialsymmetrischen s-Orbitale der Metalle, die wegen ihrer Symmetrie robuster gegenüber Kristallfehlern sind. Das Valenzband wird elektronisch von den p-Orbitalen des Sauerstoffs dominiert, weshalb die Lochmobilität durch Kristallfehler stärker sinkt als die Elektronenmobilität. Das Leitungsband ist deshalb gegenüber dem Valenzband durch eine höhere Elektronenmobilität charakterisiert.

siert, da dort die stärker delokalisierten (und weniger von Fehlstellen beeinflussten) s-Orbitale des Metallatoms eine Rolle spielen.

Dass Metalloxide im allgemeinen bessere Elektronen- als Lochleiter sind, stellt eine Herausforderung für die Konzeption von elektrischen Schaltungen dar, da z.B. komplementäre Transistoren für CMOS-Schaltungen nötig sind. Es gibt allerdings bereits erste Ansätze für Schaltungen mit Metalloid-FETs in CMOS-Technik.[58]

Viele Metalloxide weisen große Bandlücken von ca. 1-4 eV[23, 56, 59], was sie zunächst zu Isolatoren machen würde. Metalloxide und insbesondere die in dieser Arbeit verwendeten Halbleiter weisen in der Realität stets eine unbeachtete Dotierung (engl. *unintentional doping*, UID) auf.[60–62] Dabei wird im Experiment beobachtet, dass eigentlich halbleitende Metalloxide auch ohne absichtliche Dotierung auch unter Reinbedingungen eine hohe Ladungsträgerdichte aufweisen (z.B. für  $\text{In}_2\text{O}_3$  von  $10^{17} \text{ cm}^{-3}$ [60] bis  $10^{19} \text{ cm}^{-3}$ [63]). Die genaue Ursache(n) dafür sind noch nicht eindeutig geklärt.[61] Zum einen wurde im Experiment gezeigt, dass der Sauerstoffpartialdruck[64] bzw. eine chemisch oxidierende[65] oder reduzierende[66] Atmosphäre die Ladungsträgerdichte beeinflusst. Dies kann theoretisch durch Sauerstofffehlstellen erklärt werden, die in DFT-Rechnungen zu schwach gebundenen Elektronen (nahe dem Leitungsband) führen.[67, 68] Zum anderen zeigen weitere DFT-Berechnungen einen ähnlichen Effekt für ein Wasserstoffatom auf einem Zwischengitterplatz[69]. Wasserstoff ist im Experiment so gut wie überall auch unter Reinbedingungen vorhanden[61]. Auch Wasser kann einen Einfluss auf die Leitfähigkeit von  $\text{In}_2\text{O}_3$  haben. [70, 71] Es ist auch denkbar, dass sowohl Sauerstofffehlstellen als auch Wasserstoffinterstitials eine Rolle für UID spielen.

In gewissem Rahmen können die Effekte, die zu UID führen, auch genutzt werden um die elektrischen Eigenschaften von Metalloxiden gezielt zu beeinflussen, indem die Metalloxide einer chemisch reduzierenden bzw. oxidierenden Umgebung ausgesetzt werden.[65, 66] Poröse Metalloxide werden auch als chemische Sensoren verwendet, da die elektronischen Eigenschaften empfindlich gegenüber Stoffen aus der Umgebung sind, die z.B. in Fehlstellen im Kristallgitter diffundieren können.[72, 73]

In dieser Arbeit werden sowohl halbleitende ( $\text{SnO}_2$ ,  $\text{In}_2\text{O}_3$ , IGZO) als auch leitende (ITO) Metalloxide untersucht und verwendet. ITO ist eine ternäre Verbindung aus Indium, Zinn und Sauerstoff. Es wird manchmal als mit Zinn dotiertes Indiumoxid bezeichnet, allerdings ist der Anteil an Zinn mit einigen Prozent um Größenordnungen höher als es für herkömmliche Dotierung typisch ist. ITO ist ein optisch durchsichtiger elektrischer Leiter und hat in der Industrie bereits eine Vielzahl von Anwendungen, z.B. zur Beheizung von Glasscheiben[74] oder als Elektrode von Displays oder Solarzellen[75]. Dabei bewirkt die hohe Bandlücke des Indiumoxid, dass sichtbares Licht nicht absorbiert wird. Die Beimischung von Zinn bzw.  $\text{SnO}_2$  ermöglicht aber die elektrische Leitfähigkeit durch Energieniveaus nahe des Fermi-Niveaus. ITO ist damit undurchlässig für Infrarotstrahlung. Zusätzlich weist die Bandstruktur optisch verbotene Übergänge auf, weshalb die optische Bandlücke größer als die tatsächliche Bandlücke ist.[76] ITO wird in den Transistoren in dieser Arbeit als Elektrodenmaterial verwendet.

Von den halbleitenden Metalloxiden soll  $\text{SnO}_2$  und  $\text{In}_2\text{O}_3$  genauer betrachtet werden, die als Halbleitermaterial in den meisten gedruckten Transistoren dieser Arbeit

verwendet werden. Sie weisen Bandlücken von 3,6 ( $\text{SnO}_2$ ) [77–79] und 2,9 eV bzw. 3,75 eV ( $\text{In}_2\text{O}_3$  fundamental bzw. optisch) [76] auf und sind beide durch den Sauerstoffpartialdruck dotierbar[66, 80]. Sie weisen üblicherweise die rutil/tetragonale bzw. bixbyit/kubische-Kristallstruktur auf. Je nach Kristallinität, stöchiometrischem Gleichgewicht und Reinheit weisen sie Elektronenmobilitäten von  $5 \text{ cm}^2\text{V}^{-1}\text{s}^{-1}$  ( $\text{SnO}_2$ , Nanopartikel)[81] bis  $200 \text{ cm}^2\text{V}^{-1}\text{s}^{-1}$  ( $\text{SnO}_2$ , kristallin)[82] bzw.  $0,44 \text{ cm}^2\text{V}^{-1}\text{s}^{-1}$  ( $\text{InO}_2$ , gedruckt über precursor bei  $250^\circ\text{C}$ )[83] bis  $225 \text{ cm}^2\text{V}^{-1}\text{s}^{-1}$  ( $\text{InO}_2$ , MBE, kristallin)[84] auf. Die Ladungsträgerdichte ohne beabsichtigte Dotierung wird in der Literatur für  $\text{SnO}_2$  im Bereich von  $10^{17}\text{--}10^{19} \text{ cm}^{-3}$ [81, 82] und bei  $\text{In}_2\text{O}_3$  von  $7 \cdot 10^{16} \text{ cm}^{-3}$ [84] bis  $10^{19} \text{ cm}^{-3}$  [85] angegeben.

Eine wichtige Rolle in Metalloxiden wie  $\text{SnO}_2$  und  $\text{In}_2\text{O}_3$  spielt der sog. *surface electron accumulation layer* (SEAL)[61, 86, 87]. In dieser Schicht an der Oberfläche ist die Elektronendichte erhöht, was erneut mit Sauerstofffehlstellen (bzw. Wasserstoff-Interstitials, siehe oben) erklärt wird. Dies führt zu abgesenkten Bändern an der Oberfläche, was das Leitungsband füllt. Im Experiment kann der SEAL chemisch eingestellt werden.[88] Der SEAL erschwert (als Oberflächeneffekt) die Bestimmung der bulk-Elektronendichten und -mobilitäten.

## 2.6 Kohlenstoff-Nanoröhrchen

Kohlenstoff-Nanoröhrchen[89, 90] (engl. *carbon nanotubes* oder abgekürzt *CNT*) sind eine Modifikation bzw. ein Allotrop des Kohlenstoffs. Sie bestehen aus reinem Kohlenstoff, der  $\text{sp}^2$ -hybridisiert in einer hexagonalen Struktur als Zylindermantel-Fläche bzw. Röhre angeordnet ist. Ähnliche Modifikationen des Kohlenstoffs mit anderer Topologie sind z.B. Graphen[91] und Fullerene[92]. Kohlenstoff-Nanoröhrchen können aus einer einzelnen, zwei oder mehr Schichten aus Kohlenstoff-Atomen bestehen (SW-CNT, DWCNT, MWCNT, *single/double/multi walled carbon nanotube*). CNTs haben (ähnlich wie Graphen) außergewöhnliche mechanische Eigenschaften, es wurde z.B. bei MWCNT axial eine Zugfestigkeit von 11 bis 63 Gigapascal beobachtet[93]. Geometrisch zeichnen sich CNT durch ihre Zylinderform aus und können große Aspektverhältnisse aufweisen. Ihr Durchmesser liegt in der Größenordnung von Nanometern[89], die Länge aber reicht von Nanometern bis hin zu Zentimetern[94]. Die Gitterkonstante  $a$  beträgt  $0,246 \text{ nm}$ [89].

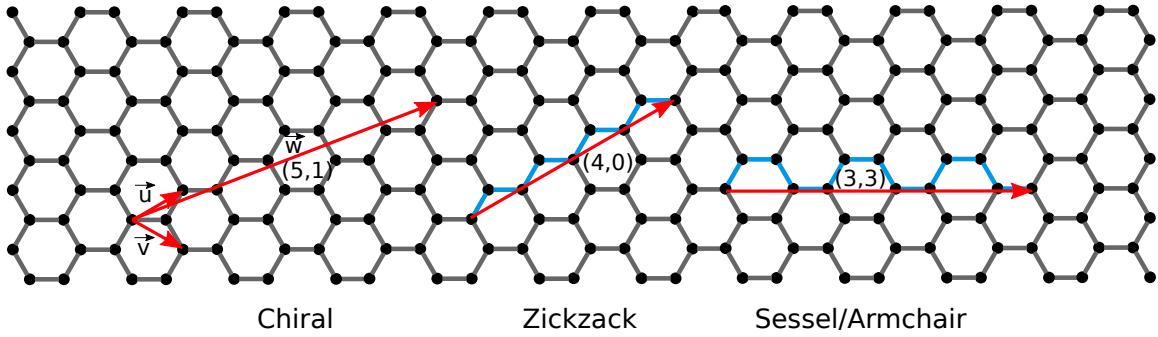

Neben diesen geometrischen Eigenschaften zeichnet sich ein CNT durch die Orientierung der Atomgitters in Relation zur CNT-Achse aus, auch Chiralität genannt. Dazu geht man zunächst von der Graphen-Struktur aus und definiert die Gittervektoren  $\vec{u}$  und  $\vec{v}$  (siehe Abb. 2.6). Aus den Gittervektoren kann man einen Verbindungsvektor  $\vec{w}$  zwischen zwei Atomen definieren:  $\vec{w}(n,m) = n \cdot \vec{u} + m \cdot \vec{v}$ , wobei  $n$  und  $m$  ganze Zahlen sind. Rollt man imaginär das Graphen so auf, dass zwei bestimmte Atome (mit Verbindungsvektor  $\vec{w}(n,m)$ ) gerade aufeinander liegen, ergibt sich ein CNT, dessen Chiralität bzw. Typ und Durchmesser mit dem Tupel  $(n,m)$  eindeutig definiert ist. Symmetriebedingt gibt es unendlich viele  $(n,m)$  für einen bestimmten CNT-Typ. Es ist Konvention,  $n \geq m \geq 0$  zu wählen [89]. In Abb. 2.6 ist  $\vec{w}$  für die Typen (5,1), (4,0) und (3,3) als roter Pfeil dargestellt.

**Abbildung 2.6:** Darstellung von Graphen als ausgerolltes Kohlenstoffnanoröhrchen (CNT).  $\vec{u}$  und  $\vec{v}$  bezeichnen die Einheitsvektoren.  $\vec{w}$  definiert den Umfang eines CNT, der entsteht wenn Graphen so aufgerollt werden würde, dass Start- und Endpunkt von  $\vec{w}$  aufeinander liegen. Links ist  $\vec{w}$  für den chiralen Typ  $(5,1)$ , in der Mitte für den Zickzack-Typ  $(4,0)$  und rechts für den Sessel- bzw. armchair-Typ  $(3,3)$  dargestellt. Die gedachten Umfangslinien, die den Zickzack- bzw Sessel-Typ ergeben, sind blau eingefärbt.

Der CNT-Typ  $(n,0)$  wird auch als „Zickzack“-Typ bezeichnet, da bei diesem Typ eine geschlossene Kette aus nächsten Nachbarn um den CNT gebildet werden kann, die wechselweise einen Winkel von  $\pm 60^\circ$  aufweisen (blau dargestellt in der Mitte von Abb. 2.6). Der Typ  $(n,n)$  wird als „Sessel“-Typ (engl. „armchair“) bezeichnet, da die geschlossene Kette um den CNT eine Form ergibt, die zweimal  $60^\circ$  in die eine und dann zweimal in die andere Richtung weist, was an einen Sessel erinnern kann (blau dargestellt in Abb. 2.6, rechts). Alle anderen Typen sind (im Gegensatz zum „Zickzack“- und „Sessel“-Typ) asymmetrisch und werden als chiral bezeichnet.

Je nach Typ haben CNT unterschiedliche elektrische Eigenschaften[95], die in erster Näherung die von Graphen mit periodischen Randbedingungen sind (*zone-folding-approximation*)[96, 97]. Die 1D-Dispersionsrelation ergibt sich aus einem Schnitt durch die (zweidimensionale) Dispersionrelation des Graphens. Durchläuft der Schnitt den Dirac-Punkt, ist ein CNT metallisch (bzw. die Bandlücke beträgt 0 eV), sonst halbleitend. CNT des Typs  $(n,m)$ , Ist  $n - m$  ein ganzzahliges Vielfaches von 3, ist ein CNT metallisch. Das schließt alle Sessel-CNT wegen  $n = m$  ein. Alle anderen sind halbleitend. Je kleiner der Durchmesser eines CNT ist, desto mehr scheitert die Näherung als Graphen mit periodischen Randbedingungen und die Bandstruktur hängt zusätzlich vom CNT-Durchmesser ab[98].

Um den Durchmesser  $d_{CNT}$  eines CNT zu berechnen, wird zunächst der Umfang  $u_{CNT}$  eines CNT aus geometrischen Überlegungen mit der Gitterkonstanten  $a$  und dem Typ  $(n,m)$  des CNT berechnet zu  $u_{CNT} = a \cdot \sqrt{n^2 + m^2 + n \cdot m}$ . Daraus ergibt sich der Durchmesser  $d_{CNT} = \frac{u_{CNT}}{\pi}:[89]$

$$d_{CNT} = \frac{a}{\pi} \cdot \sqrt{n^2 + m^2 + n \cdot m} \quad (2.2)$$

Ein  $(7,6)$ -CNT hat beispielsweise einen Durchmesser von 0,88 nm.

Daraus lässt sich auch die Liniendichte der Kohlenstoffatome bestimmen [99]:

$$n_c = \frac{4\pi d_{CNT}}{a^2 \sqrt{3}} \quad (2.3)$$

Sie beträgt beispielsweise in einem (7,6)-CNT  $102,9 \frac{1}{\text{nm}}$ .

## 2.7 Markov-Chain-Monte-Carlo

Monte-Carlo-Verfahren (MC) sind nach dem für sein Glücksspielcasino bekannten Bezirk von Monaco benannt und sind nicht-deterministisch, sie basieren auf dem Zufall. Sie haben vielfältige Anwendungen in der Mathematik, Physik, Informatik und Wirtschaft. Mit ihnen ist es möglich, gute Näherungen zu Fragestellungen zu erhalten, die analytisch gar nicht oder nur sehr aufwändig lösbar sind. Im Folgenden sollen die Grundzüge sowie die algorithmische Anwendung dargestellt werden. Der Abschnitt basiert auf [100].

In der Physik kann das Markov-Chain-Monte-Carlo-Verfahren (MCMC) genutzt werden, um thermodynamische Größen eines Systems zu bestimmen. Es ermöglicht eine Näherung der Zustandssumme, aus der die thermodynamischen Zustandsgrößen berechnet werden können. Dazu muss eine Markov-Kette der Zustände des Systems erstellt werden. Jeder Zustand hängt dabei ausschließlich vom vorigen Zustand ab. Wird die Karkov-Kette gemäß dem detaillierten Gleichgewicht erstellt, so ist nach einer unendlich großen (real: sehr großen) Anzahl von Simulationsschritten die Besetzungswahrscheinlichkeit bzw. Häufigkeit für alle Zustände boltzmannverteilt.

Im thermodynamischen Gleichgewicht ist das detaillierte Gleichgewicht (engl. detailed balance) erfüllt. Es besagt, dass für die Wahrscheinlichkeit  $P$  für einen Wechsel von einem beliebigen Zustand  $z_a$  zu Zustand  $z_b$  und für den umgekehrten Prozess sowie für die Energiedifferenz  $\Delta E$  der Zustände gelten muss:

$$\frac{P(z_a \rightarrow z_b)}{P(z_b \rightarrow z_a)} = \exp\left(\frac{1}{k_B T} \cdot \Delta E\right) \quad (2.4)$$

Das detaillierte Gleichgewicht folgt daraus, dass im thermodynamischen Gleichgewicht die Rate  $\Gamma(z_a \rightarrow z_b)$  für alle Übergang vom Zustand  $z_a$  zu Zustand  $z_b$  gleich sein muss wie für den umgekehrten Prozess ( $\Gamma(z_a \rightarrow z_b) = \Gamma(z_b \rightarrow z_a)$ ). Die Rate kann über die Wahrscheinlichkeit  $P$  und die Zustandssumme  $Z$  definiert werden:

$$\Gamma(z_a \rightarrow z_b) = P(z_a \rightarrow z_b) \cdot \frac{1}{Z} \cdot \exp\left(-\frac{1}{k_B T} \cdot E(z_a)\right) \quad (2.5)$$

Daraus folgt das detaillierte Gleichgewicht.

Ein MCMC-Simulationsalgorithmus erzeugt ein kanonisches Ensemble von Zuständen und minimiert im thermodynamischen Gleichgewicht die freie Energie  $F = U - TS$ , wobei für  $U$  für die innere Energie und  $S$  für die Entropie steht. In einer MCMC-Simulation wird eine Kette aus Zuständen gebildet, indem für den letzten Zustand eine (möglicherweise) zufällige Änderung gesucht wird und anhand eines Akzeptanzkriteriums entschieden wird, ob der geänderte Zustand oder der unveränderte Zustand an das Ende der Kette gesetzt wird.

## 2 Grundlagen

---

Eine Variante der MCMC ist der Metropolis-Monte-Carlo-Algorithmus[101], der folgendermaßen abläuft[100]:

1. Das System wird auf einen beliebigen (z.B. zufälligen) Startzustand  $z_0$  gesetzt

2. Eine Modifikation  $z_m$  am System  $z_n$  wird durchgeführt und aus der Energie vor ( $E_n$ ) und nach ( $E_m$ ) der Änderung die dazugehörige Energiedifferenz  $\Delta E = E_m - E_n$  bestimmt.

3. Der modifizierte Zustand  $z_m$  wird mit der Wahrscheinlichkeit

$$p = \min \left( 1, \exp \left( \frac{E_m - E_n}{k_B T} \right) \right) \quad (2.6)$$

akzeptiert und das nächste Element  $z_{n+1}$  der Markov-Kette entsprechend entweder mit  $z_m$  (Akzeptanz) oder  $z_n$  (keine Akzeptanz) gefüllt. Ist der modifizierte Zustand  $z_m$  demnach energetisch günstiger ( $\Delta E < 0$ ), wird die Änderung angenommen ( $p = 1$ ). Ist der Zustand energetisch ungünstiger, ist die Wahrscheinlichkeit für die Akzeptanz der Änderung der Boltzmannfaktor  $p = \exp(-\Delta E/(k_B T))$  mit der Temperatur  $T$  und dem Boltzmann-Konstanten  $k_B$ .

4. Wiederhole die Schritte 2 und 3.

Das Metropolis-Markov-Chain-Monte-Carlo wird häufig angewendet, da es wegen der zufälligen Systemänderungen einfach zu implementieren ist. Ein Nachteil ist, dass je nach Systemtemperatur  $T$  energetisch ungünstige Schritte nur sehr selten durchgeführt werden und eine Gruppe von Zuständen deshalb korreliert sind, auch wenn über alle Zustände hinweg das Ensemble einem thermodynamischen Gleichgewicht entspricht. Dann sind eine hohe Anzahl von Simulationsschritten nötig, um den Zustandsraum ausreichend abzutasten. Bei einer ungünstigen Wahl der Modifikation am System kann es ebenfalls zu vielen nötigen Simulationsschritten kommen.

Neben dem hier vorgestellten Metropolis-Kriterium existieren auch andere Akzeptanzkriterien wie z.B. das Glauber-Akzeptanzkriterium[102].

Eine MCMC-Simulation kann mit dem Verfahren der *simulierten Abkühlung* (*simulated annealing*) modifiziert werden, um das globale Optimum einer Funktion oder eines Problems zu approximieren[103]. Dabei wird die Temperatur  $T$  während der Simulation variiert. Das detaillierte Gleichgewicht ist damit streng genommen nicht mehr gültig, bei ausreichend langsamen Abkühlgeschwindigkeiten aber in sehr guter Näherung anwendbar. Physikalisch muss das System trotz sinkender Temperatur  $T$  stets sehr nahe dem Gleichgewichtszustand sein. Das Absenken der Temperatur entspricht einer immer weiteren Einschränkung des Zustandsraums, was das System immer stärker zu seinem globalen Extremum führt (oder einem der ähnlichen Extrema, falls es Extrema mit sehr ähnlicher Energie gibt).

Der Vorteil des Verfahrens ist, dass es auf sämtlichen Optimierungsproblemen anwendbar ist, für die eine Kenngröße analog der Energie definiert werden kann. Im Gegensatz zu gradientenbasierten Verfahren kann dieses Verfahren auch energetisch ungünstigere Änderungen am System durchführen und verharrt auf diese Weise nicht in lokalen Optima, findet also besser ein tatsächliches globales Optimum.

## 2.8 Drift-Diffusionsmodell, Halbleitergleichungen

Die Halbleitergleichungen sind Differenzialgleichungen, die ortsaufgelöst das elektrische Potential sowie die Elektronen- und Lochdichte beschreiben. Sie können verwendet werden, um in numerischen Simulationen den Stromfluss sowie die elektrischen Felder in einem elektronischen Bauteil zu bestimmen. Die Halbleitergleichungen bestehen aus zwei Teilen, dem Gaußschen Gesetz bzw. der Poisson-Gleichung und den Kontinuitätsgleichungen. Die Halbleiter-Gleichungen können z.B. über die Maxwell-Gleichungen oder auch die Boltzmann-Transportgleichung hergeleitet werden. Hier soll die Herleitung über die Maxwell-Gleichungen beschrieben werden, sie basiert auf [104]. Danach wird kurz auf die Boltzmann-Transportgleichung eingegangen.

Ausgangspunkt sind die Maxwell-Gleichungen in Materie:

$$\nabla \times \vec{H} = \vec{J} + \frac{\partial \vec{D}}{\partial t} \Leftrightarrow \oint_{\partial A} \vec{H} \cdot d\vec{s} = \int_A \vec{J} \cdot d\vec{A} + \int_A \frac{\partial \vec{D}}{\partial t} \cdot d\vec{A} \quad (2.7)$$

$$\nabla \times \vec{E} = -\frac{\partial \vec{B}}{\partial t} \Leftrightarrow \oint_{\partial A} \vec{E} \cdot d\vec{s} = -\int_A \frac{\partial \vec{B}}{\partial t} \cdot d\vec{A} \quad (2.8)$$

$$\nabla \cdot \vec{D} = \rho \Leftrightarrow \oint_{\partial V} \vec{D} \cdot d\vec{A} = Q(V) \quad (2.9)$$

$$\nabla \cdot \vec{B} = 0 \Leftrightarrow \oint_{\partial V} \vec{B} \cdot d\vec{A} = 0 \quad (2.10)$$

Sie können sowohl differziell (links) als auch integral (rechts) dargestellt werden, im Folgenden wird ausschließlich die differenzielle Darstellung verwendet. Im Falle eines Halbleiter ist die Ladungsdichte  $\rho$  über die Dichte von Elektronen ( $n$ ), Löchern ( $p$ ) und eingebrachten fixen Ladungen bestehend aus Donatoren ( $N_D$ ) und Akzeptoren ( $N_A$ ) definiert:

$$\rho = q(p - n + N_D - N_A) \quad (2.11)$$

$q$  beschreibt die Elementarladung mit positivem Vorzeichen.

Für die elektrische Verschiebungsdichte  $\vec{D}$ , das elektrische Feld  $\vec{E}$  die Permittivität  $\varepsilon$  und das elektrische Potential  $\Phi$  gilt:

$$\vec{D} = \varepsilon \vec{E} = -\varepsilon \nabla \Phi, \quad (2.12)$$

Setzt man dies mit Gleichung 2.11 in Gleichung 2.9 ein und nimmt eine isotrope (skalare) Permittivität  $\varepsilon$  an, ergibt sich:

$$\Delta \Phi = \frac{q}{\varepsilon} (n - p - N_D + N_A) \quad (2.13)$$

Dies ist die Poisson-Gleichung in einem Halbleiter mit dem elektrischen Potential  $\Phi$  und den Ladungsträgerdichten  $n$ ,  $p$  und  $N_D$  und  $N_A$ .

Für die Herleitung der Kontinuitätsgleichungen wendet man die Divergenz auf Gleichung 2.7 an. Da die Divergenz einer Rotation gleich Null ist, erhält man:

$$0 = \nabla \cdot \vec{J} + \nabla \cdot \frac{\partial \vec{D}}{\partial t} \quad (2.14)$$

Auf den rechten Summanden kann Gleichung 2.9 angewendet werden, da die zeitliche und räumliche Ableitung vertauschbar sind. Dies ergibt die Kontinuitätsgleichung

$$0 = \nabla \cdot \vec{J} + \frac{\partial \rho}{\partial t} \quad (2.15)$$

Aus der Gleichung folgt, dass das Vektorfeld der Stromdichte quellenlos ist, sich die Ladungsdichte also zeitlich nicht ändert wenn ein- und ausfließender Strom gleich groß sind.

Setzt man den Ausdruck 2.11 für die Ladungsdichte in die Kontinuitätsgleichung 2.15 ein, erhält man:

$$0 = \nabla \cdot \vec{J} + q \frac{\partial}{\partial t} (p - n + N_D - N_A) \quad (2.16)$$

Nimmt man die Dotierkonzentrationen als vollständig ionisiert und damit nicht zeitabhängig an, sind die beiden letzten Summanden aus dieser Gleichung gleich 0. Die Gleichung kann in einen Elektronen- und einen Lochteil separiert werden:

$$\hat{U} = \nabla \cdot \vec{J}_p + q \frac{\partial}{\partial t} p \quad (2.17)$$

$$-\hat{U} = \nabla \cdot \vec{J}_n - q \frac{\partial}{\partial t} n \quad (2.18)$$

Bei der Separation entsteht ein Freiheitsgrad, da ein Summand  $\pm \hat{U}$  beim Addieren der Gleichungen eliminiert wird. Physikalisch ist  $\hat{U}$  die Rate für die Generierung und Rekombination von Elektronen und Löchern bzw. allgemein von erzeugten Paaren von positiven und negativen Ladungen.

Die in Gl. 2.17 und 2.18 enthaltene Stromdichten kann im Halbleiter in den Elektronen- und Lochstrom  $\vec{J} = \vec{J}_p + \vec{J}_n$  aufgeteilt und als Summe aus einem Drift- und Diffusionsterm geschrieben werden:

$$\vec{J}_p = qp\mu_p \vec{E} - qD_p \nabla p \quad (2.19)$$

$$\vec{J}_n = qn\mu_n \vec{E} + qD_n \nabla n \quad (2.20)$$

Mit der Nernst-Einstein-Beziehung  $D = \mu \frac{k_B T}{q}$ , die den mikroskopischen Diffusionskoeffizienten  $D$  mit der makroskopischen Mobilität  $\mu$  verknüpft [105], ergibt sich zusammen mit Gl. 2.12:

$$\vec{J}_p = -qp\mu_p \nabla \Phi - \mu_p k_B T \nabla p \quad (2.21)$$

$$\vec{J}_n = -qn\mu_n \nabla \Phi + \mu_n k_B T \nabla n \quad (2.22)$$

Diese Formeln beschreiben den Driftstrom (erster Summand) als Funktion des Gradienten des elektrischen Potentials sowie den Diffusionsstrom (zweiter Summand) als Funktion vom Gradienten der Teilchendichte.

In die Gleichungen 2.17 und 2.18 können nun die Stromdichten 2.21 und 2.22 eingesetzt werden, was zu folgenden Gleichungen führt:

$$\nabla \left( p\mu_p \nabla \Phi + \frac{k_B T}{q} \mu_p \nabla p \right) + U = \frac{\partial}{\partial t} p \quad (2.23)$$

$$\nabla \left( n\mu_n \nabla \Phi - \frac{k_B T}{q} \mu_n \nabla n \right) - U = \frac{\partial}{\partial t} n \quad (2.24)$$

$\hat{U}/q$  wurde dabei durch  $U$  ersetzt. Die Gleichungen 2.13, 2.23 und 2.24 werden zusammen als Halbleitergleichungen bezeichnet. Sie beschreiben ein Set aus drei gekoppelten Differenzialgleichungen für das elektrische Potential  $\Phi(\vec{r})$ , die Elektronendichte  $n(\vec{r})$  und die Lochdichte  $p(\vec{r})$ . Aus diesen Größen kann leicht das elektrische Feld  $\vec{E}(\vec{r})$ , die Elektronenstromdichte  $\vec{J}_n(\vec{r})$  und die Lochstromdichte  $\vec{J}_p(\vec{r})$  berechnet werden. Diese Größen sind wichtig für das Verständnis von elektronischen Bauteilen. Werden die Halbleitergleichungen räumlich diskretisiert, können damit Halbleiterbauteile simuliert werden [106, 107].

Quantenmechanische Effekte werden in diesem Modell vernachlässigt. Kommerzielle Simulationssoftware für die Chipindustrie koppelt die Halbleitergleichungen noch mit der Schrödingergleichung, um auch quantenmechanische Effekte zu berücksichtigen.[108] Ein weiteres Problem sind z.B. thermionische Ströme, um die das Drift-Diffusions-Modell zwar leicht erweitert werden kann, die allerdings nicht streng aus den Maxwellgleichungen hergeleitet werden können.

Neben der eben beschriebenen Herleitung der Halbleitergleichungen über die Maxwell-Gleichungen können die Halbleitergleichungen auch aus der Boltzmann-Transportgleichung hergeleitet werden.[109–112] Diese Herleitung ist allgemeiner, da der Kollisionsterm auf viele physikalische Effekte angewendet werden kann. Die Boltzmann-Transportgleichung lautet

$$\left( \frac{\partial}{\partial t} + \vec{v} \cdot \nabla_{\vec{x}} + \frac{\vec{F}}{m} \cdot \nabla_{\vec{v}} \right) f(\vec{x}, \vec{v}, t) = \left( \frac{\partial}{\partial t} \right)_{coll} \quad (2.25)$$

Auf der linken Seite steht die totale Zeitableitung der Verteilungsdichte, auf der rechten Seite ein Kollisionsterm.  $\vec{v}$  steht für die Geschwindigkeit eines Teilchens,  $\vec{x}$  für den Ort,  $m$  für dessen Masse und  $\vec{F}$  für eine äußere Kraft.  $f(\vec{x}, \vec{v}, t)$  steht für die Verteilungsdichte der Teilchen. Für den stationären Fall lassen sich aus Gleichung 2.25 mit einem phänomenologischen Kollisionsterm wie  $\frac{f_{eq} - f(\vec{x}, \vec{v}, t)}{\tau}$  (mit der Relaxationszeit  $\tau$ ) die Drift-Diffusionsgleichungen herleiten. Für eine selbstkonsistente Lösung müssen diese noch mit der Poisson-Gleichung gekoppelt werden, um die Halbleitergleichungen zu erhalten. Alternativ zu den Halbleitergleichungen kann die Boltzmann-Transportgleichung auch direkt gelöst werden, dazu wurde die Lattice-Boltzmann-Methode entwickelt.[113]

## 2.9 Numerische Lösungsmethoden partieller Differenzialgleichungen

Die Halbleitergleichungen können nicht im Allgemeinen geschlossen analytisch gelöst werden. Es existieren aber numerische Verfahren zum Lösen der Halbleitergleichungen auf realitätsnahen Systemen. In diesem Abschnitt wird zunächst das in dieser Arbeit hauptsächlich verwendete Finite-Volumen-Verfahren (FVM) erklärt und anschließend das Finite-Elemente-Verfahren (FEM) kurz vorgestellt.

Ziel ist, eine partielle Differenzialgleichung der Form

$$\frac{\partial q(\vec{r}, t)}{\partial t} + \nabla \cdot \vec{f}(q(\vec{r}, t)) = 0. \quad (2.26)$$

zu Lösen. Sie beschreibt die Erhaltungsgröße  $q$  mit dem dazugehörigen Fluss  $\vec{f}(q)$ .

**Finite-Volumen-Verfahren** Im Finite-Volumen-Verfahren (FVM) werden Geometrieeinheiten als Voxel mit definierten Randflächen modelliert. Die Volumenintegrale der Ladungsträgerdichten werden über den gaußschen Integralsatz in Oberflächenintegrale der Ströme durch die Grenzflächen umgewandelt. Da der ausgehende Fluss aus einem Voxel gleich dem eingehenden Fluss des benachbarten Voxels an der selben Grenzfläche ist, ist die Menge an Ladungsträgern (von expliziten Injektions- und Erzeugungstermen abgesehen) intrinsisch erhalten.

Ein Vorteil des Finite-Volumen-Verfahrens ist deshalb, dass im Falle der Halbleitergleichungen die Stromdichte der Elektronen und Löcher an den Grenzflächen und damit die Dichte der Elektronen und Löcher erhalten sind. In diesem Abschnitt soll nur ein kurzer Überblick über das Verfahren gegeben und für eine tiefere Diskussion auf Literatur wie [114, 115] verwiesen werden, die auch Grundlage für diesen Abschnitt sind.

Für das FVM muss das System in Volumenelemente  $V_i$  (analog in 2D in Flächen- bzw. in 1D Linienelemente) diskretisiert werden. Integriert man Gleichung 2.26 über ein Volumenelement, erhält man die integrale Darstellung des Erhaltungssatzes für ein Voxel  $V_i$ :

$$\frac{\partial}{\partial t} \int_{V_i} q(\vec{r}, t) dV = - \int_{V_i} \nabla \cdot \vec{f}(q(\vec{r}, t)) dV \quad (2.27)$$

Die linke Seite ist die zeitliche Ableitung des Integrals über  $q$  über ein Volumen  $V_i$ . Das Integral kann umgeschrieben werden zu einem Produkt aus  $V_i$  und dem Mittelwert  $\bar{q}_i$  der Größe  $q$  in diesem Volumen. Auf der rechten Seite wird der Gaußsche Integralsatz angewendet, der das Volumenintegral über  $V_i$  durch ein geschlossenes Oberflächenintegral über die geschlossene Grenzfläche  $S_i$  um  $V_i$  ersetzt:

$$V_i \frac{\partial}{\partial t} \bar{q}_i = - \oint_{S_i} \vec{f}(q(\vec{r}, t)) \cdot \vec{n} \cdot dS \quad (2.28)$$

$\vec{n}$  beschreibt den normierten Einheitsvektor senkrecht auf  $S_i$ . Aus der Formel folgt die physikalisch intuitive Aussage, dass eine Änderung der Erhaltungsgröße nur durch einen Netto-Fluss durch die Oberfläche gegeben ist. Für die Simulationen kann die

diskretisierte gemittelte Simulationsgröße  $\bar{q}_i$  unterschiedlich modelliert werden. Im einfachsten Fall wird sie konstant über das gesamte Volumenelement angenommen. Der Fluss (und damit die zeitliche Änderung der Erhaltungsgröße) entsteht ausschließlich durch unterschiedliche Werte von  $q$  in verschiedenen Volumenelementen. Aufwändiger Verfahren ersetzen den konstanten Mittelwert durch das Integral bzw. eine Mittelung einer linearen oder quadratischen Funktion.

Um die Konvergenz und numerische Stabilität zu verbessern, können Informationen über die Richtung der Ausbreitung von Änderungen verwendet werden.. Änderungen im System propagieren als Störungen oder Wellen. Der Fluss durch eine Grenzfläche kann dann bei bekannter Richtung des Fluxes aus den benachbarten Voxeln aus Richtung des Fluxes berechnet werden. Dies wird „Upwind-Schema“ genannt.

**Finite-Elemente-Verfahren** Die FEM-Gleichungen für die Halbleitergleichungen wurden bereits 1977 von Barnes und Lomax[106] beschrieben. Für das Finite-Elemente-Verfahren ist es notwendig, die PDE in eine sog. schwache Form umzuwandeln. Dazu wird die gesamte Gleichung mit einem sog. glatten kompakten Träger (Testfunktion) multipliziert. Der glatte kompakte Träger ist eine Funktion, die beliebig oft differenzierbar und nur in einem endlichen Intervall um einen Punkt  $x$  ungleich 0 ist. Bei der Umwandlung aus der differenziellen Form in die integrale Form ist es über geschickte partielle Integration möglich, eine Darstellung ohne Ableitungen der gesuchten Größe/Funktion zu finden. Dies hat den Vorteil, dass auch nicht (ausreichend oft) differenzierbare Lösungen möglich sind. Bei der Diskretisierung wird die Gesamtlösung genähert als Summe über die einzelnen Netzpunkte, wobei jeder Punkt über die Testfunktion nur von seiner unmittelbaren Umgebung abhängt. Sowohl über die Form und Weite der Testfunktion als auch über die Dichte der Netzpunkte kann die Stärke der Näherung eingestellt werden.

Auf eine genauere Beschreibung der FEM-Methode wird hier verzichtet, da sie in dieser Arbeit nur am Rande (Abschnitt 8.3) verwendet wurde. Für weitere Informationen und genauere Definitionen wird auf die Literatur[116, 117] verwiesen.

# 3 Methoden

## 3.1 Monte-Carlo-Simulation der Mikrostruktur

Markov-Chain-Monte-Carlo-Simulationen sind vielseitig in der Physik anwendbar[100] und können z.B. für grundlegende Entmischungssimulationen verwendet werden [118, 119]. Häufig werden diese mit einer simulierten Abkühlung kombiniert. Die dabei entstehenden kinetisch eingefrorenen Strukturen entsprechen dabei streng genommen keinem Gleichgewichtszustand, was aber der Realität näher kommt. Die Verringerung der Temperatur pro MC-Schritt („Annealing-Geschwindigkeit“) bestimmt dabei die Struktur(größe), die entsteht. Dieser Effekt ist in den Materialwissenschaften gut bekannt und wird z.B. beim Härteln von Stahl angewendet, der erhitzt und dann schlagartig abgekühlt wird [120].

Der im Rahmen dieser Arbeit implementierte Simulationscode wendet den Metropolis-Algorithmus auf einem 2D-Gitter mit periodischen Randbedingungen und zwei Phasen an. Als MC-Schritt werden zwei zufällige nächste Nachbarn ausgewählt und dem Metropolis-Kriterium entsprechend getauscht. Die Gesamtzahl von Pixeln von Phase A und B bleibt also die Simulation über konstant, das Verhältnis der Phasen zueinander in der Startbedingung ist also ein Simulationsparameter. Jede Phase entspricht dabei einem Material im realen System. Die Energie  $E$  im System ist die Summe der Energieterme  $E_{i,j}$  aller nächster Nachbarn  $i,j$ :

$$E = \frac{1}{2} \sum_{i,j} E_{i,j} \quad (3.1)$$

Der Faktor  $\frac{1}{2}$  korrigiert die doppelte Summierung über benachbarte Paare. Der Energieterm  $E_{i,j}$  hängt von den aneinander grenzenden Phasen ab und kann sinnvollerweise als Grenzflächenspannung interpretiert werden, sodass zwei gleiche benachbarte Gitterpunkte energetisch bevorzugt sind im Vergleich zu unterschiedlichen Gitterpunkten. (Dies ist vergleichbar mit einem 2D-Ising-Modell bei konstanter Magnetisierung.)

Die simulierte Abkühlung wird über eine lineare Absenkung der Temperatur durchgeführt. Die Temperatur  $T(n)$  berechnet sich dabei aus der Zahl der bereits beendeten MC-Schritte  $n$ , der Start- und Endtemperatur  $T_{Start,End}$  sowie der Gesamtzahl  $N$  der Schritte der Simulation:

$$T(n) = \left(1 - \frac{n}{N}\right) \cdot T_{Start} + \frac{n}{N} \cdot T_{End} \quad (3.2)$$

$T_{Start}$  muss dabei größer als die Übergangstemperatur bzw. die Glastemperatur gewählt werden,  $T_{End}$  muss kleiner sein.

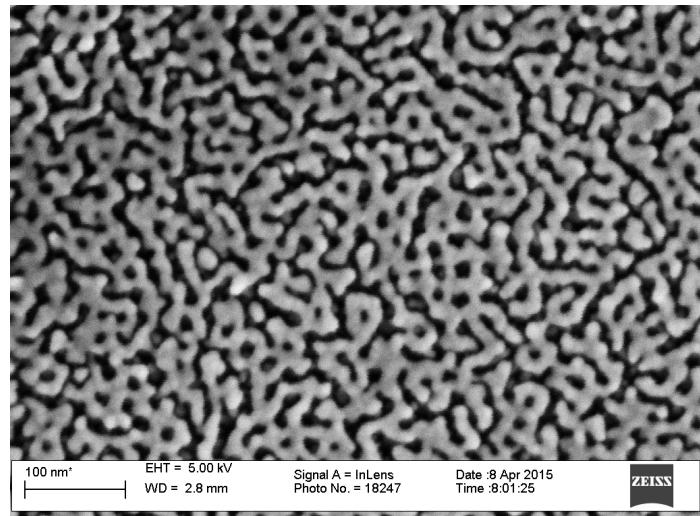

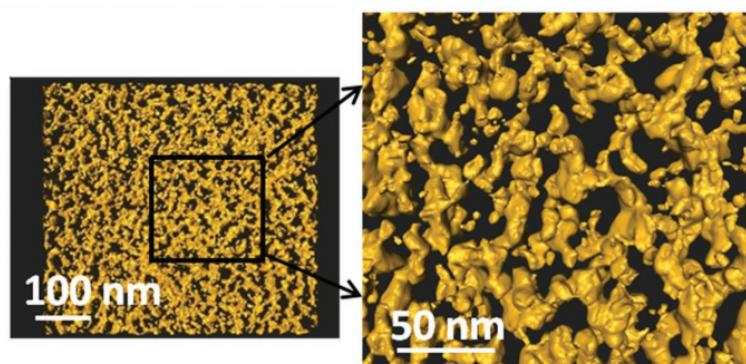

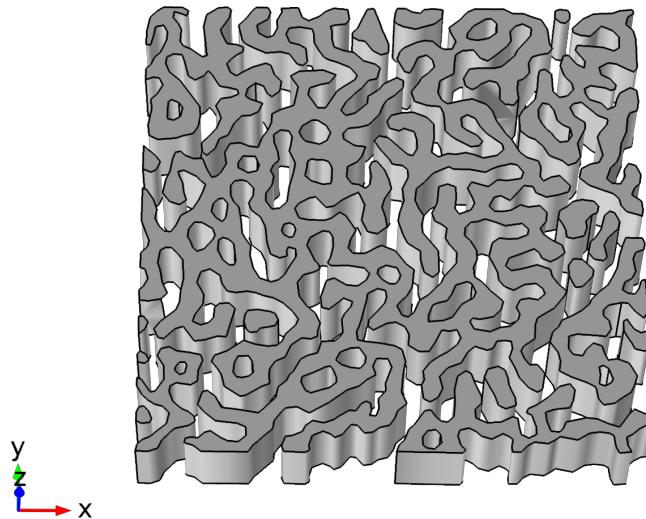

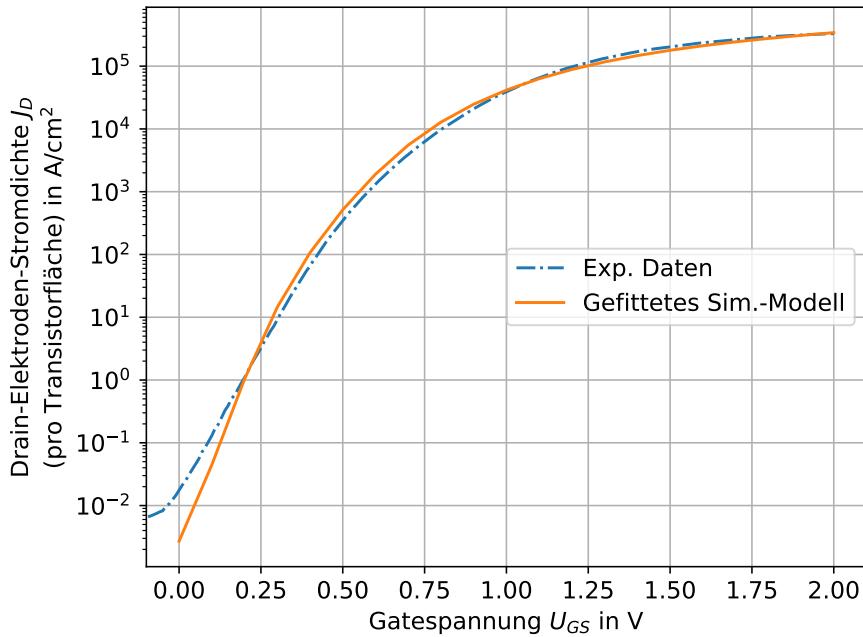

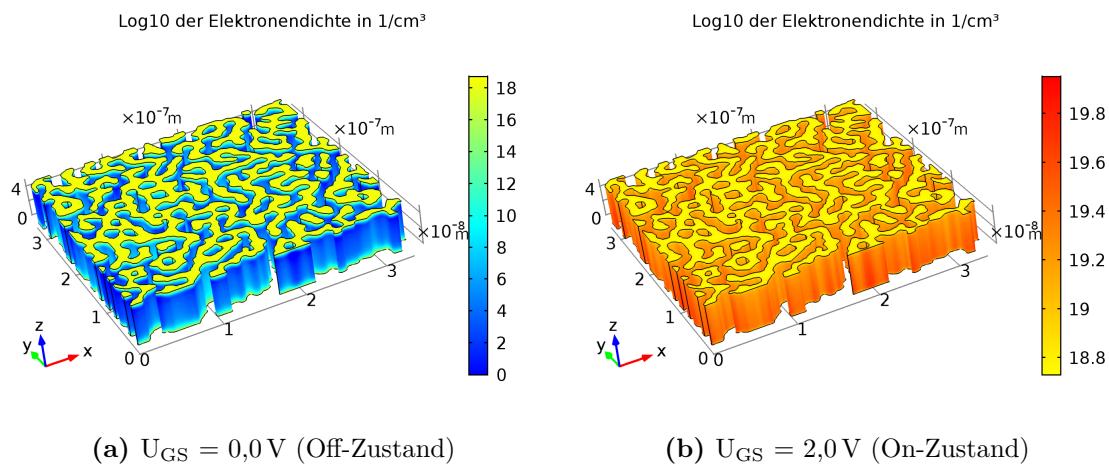

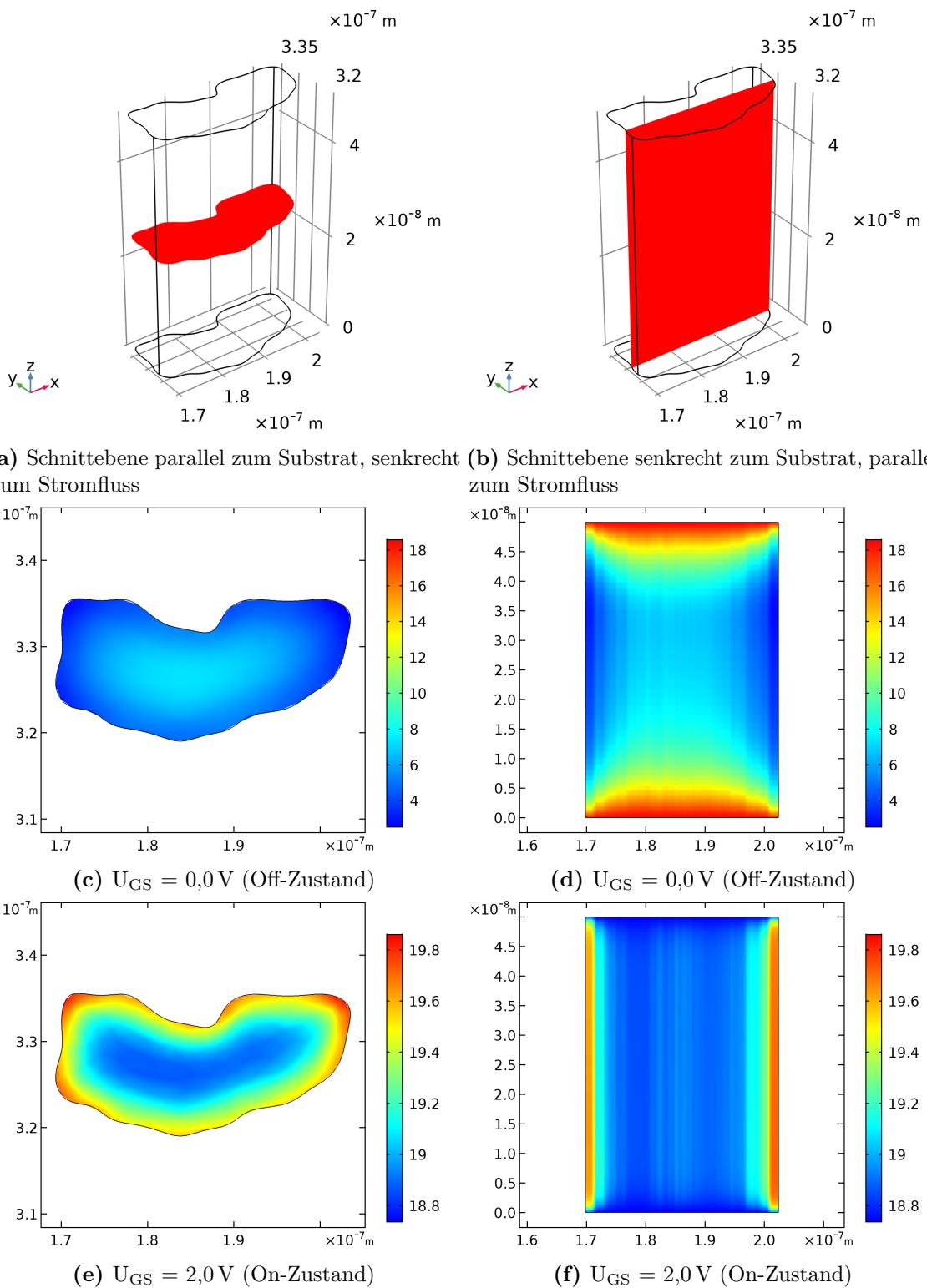

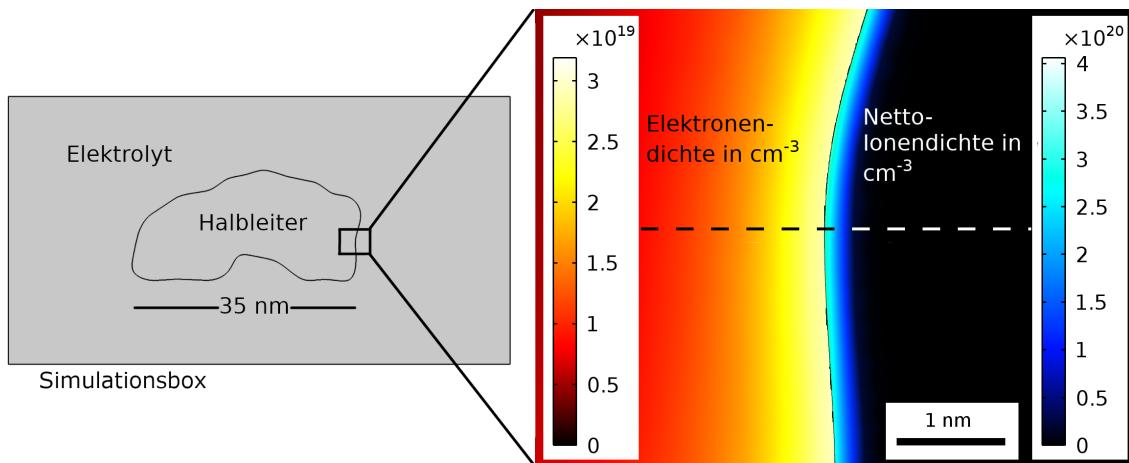

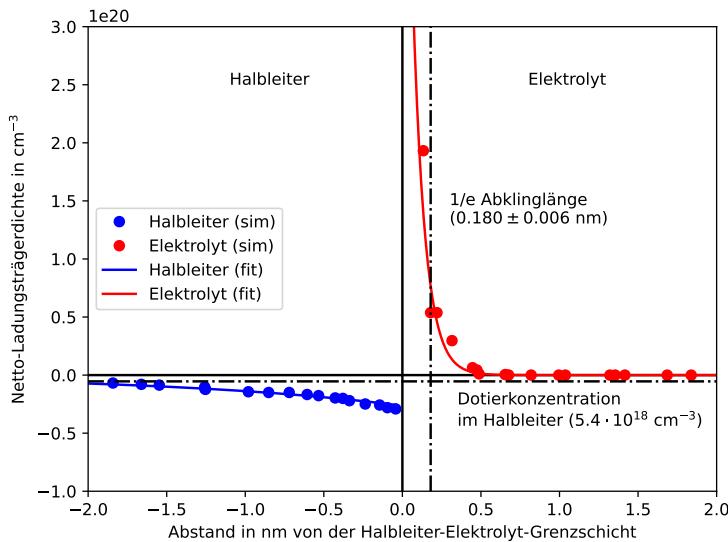

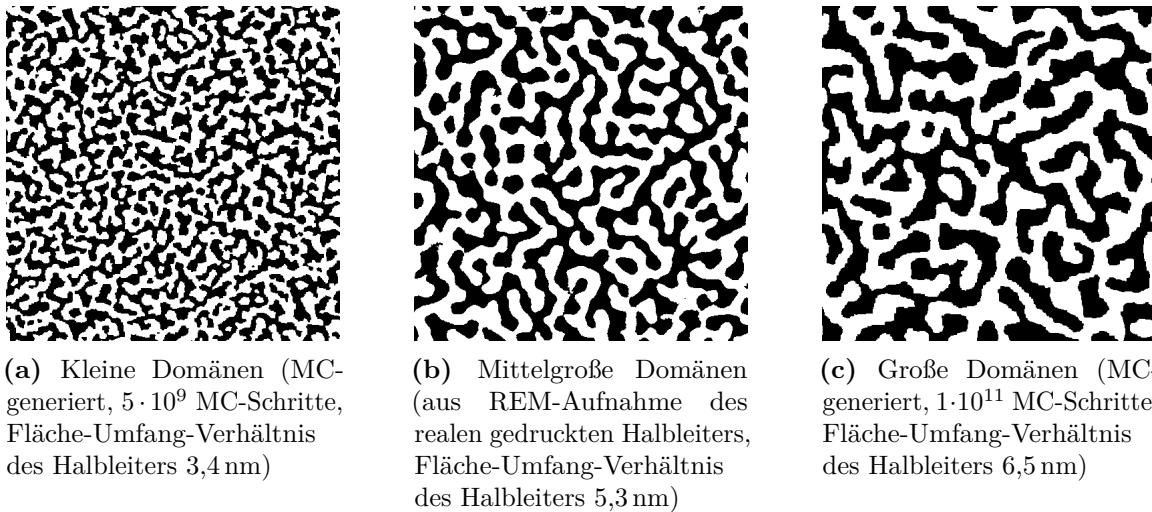

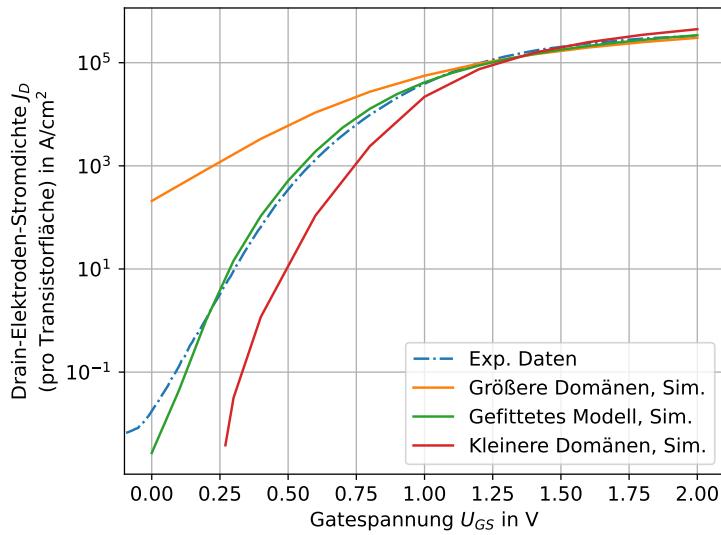

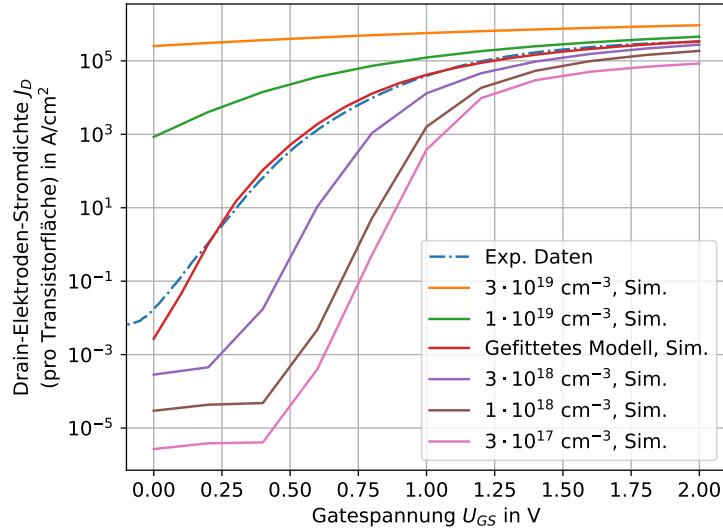

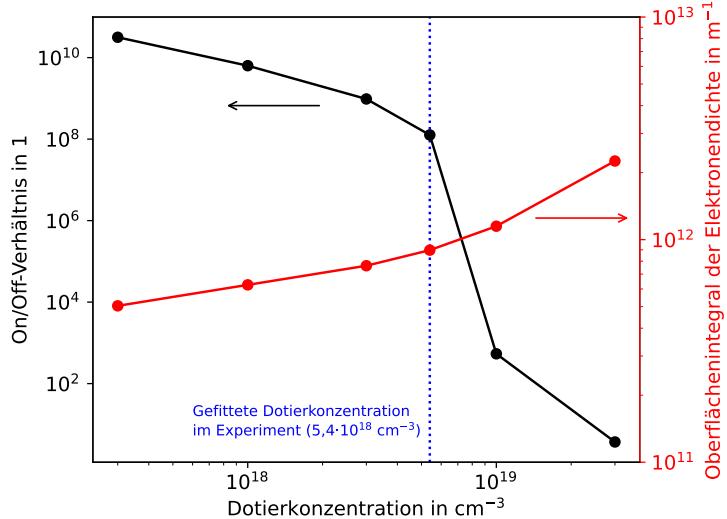

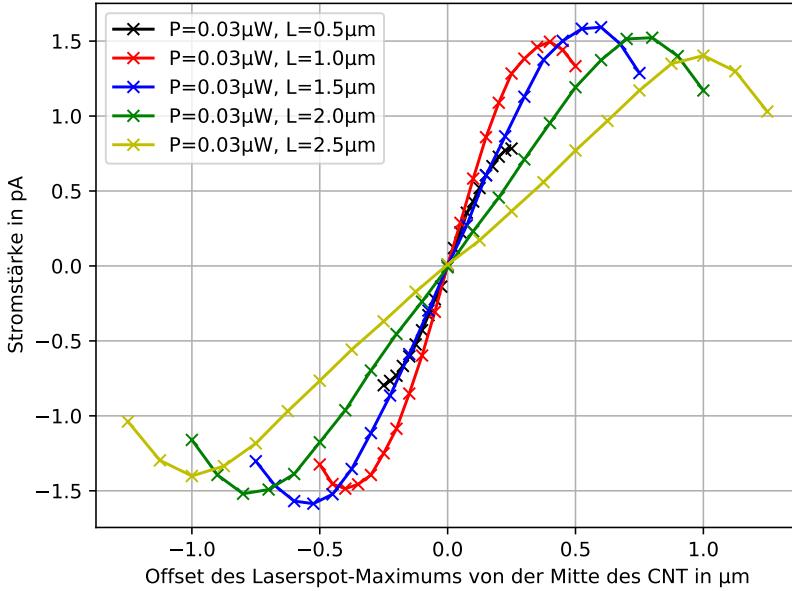

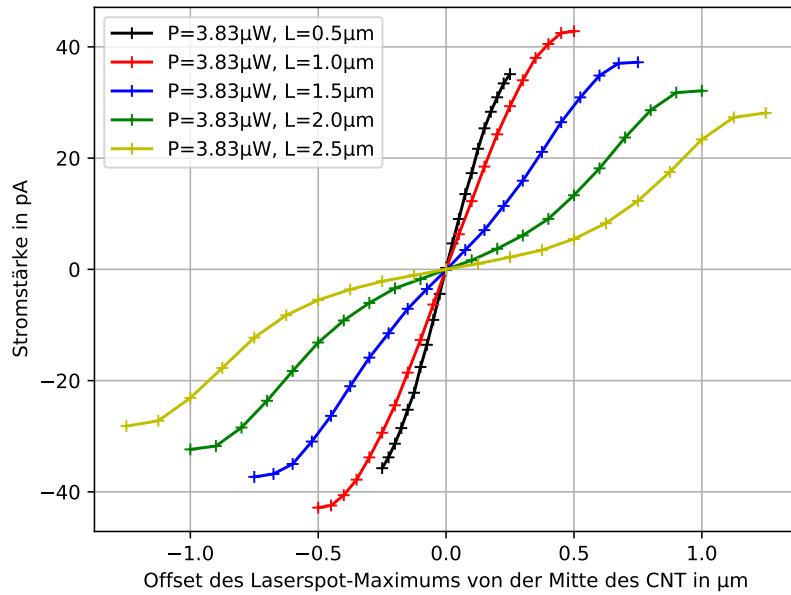

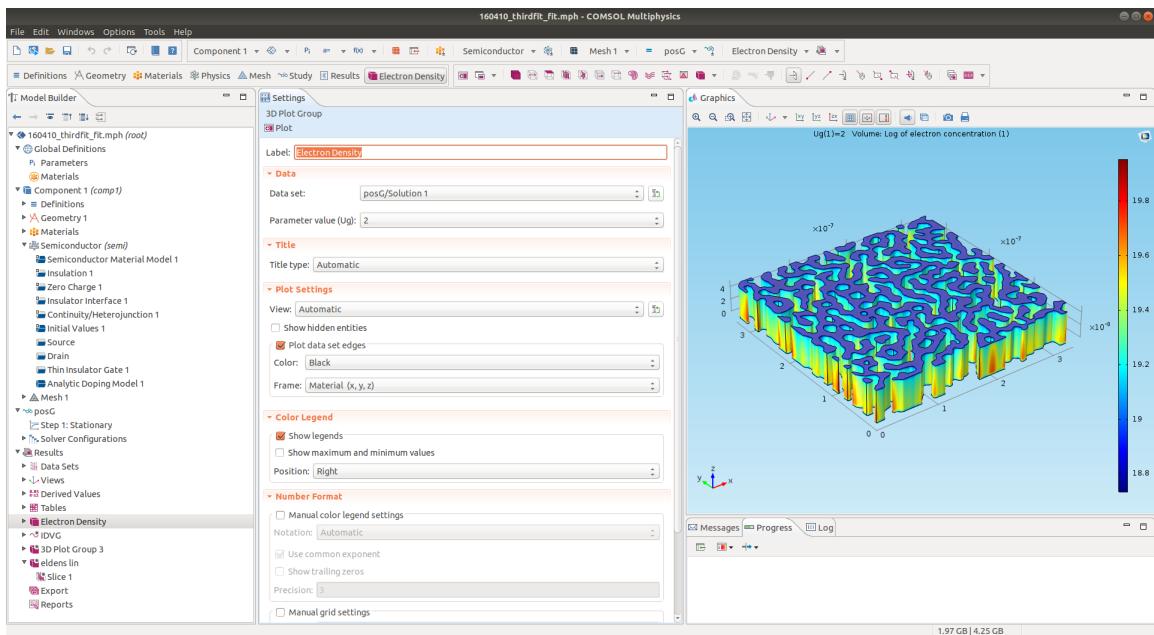

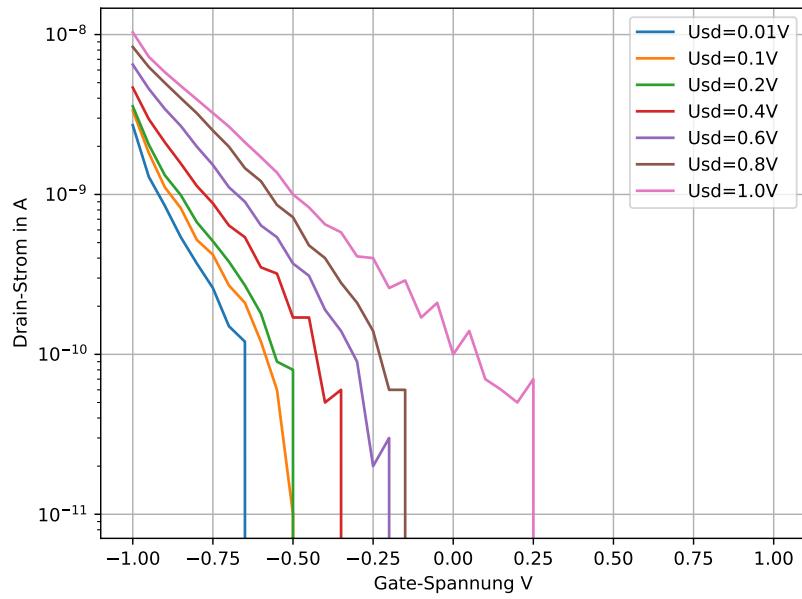

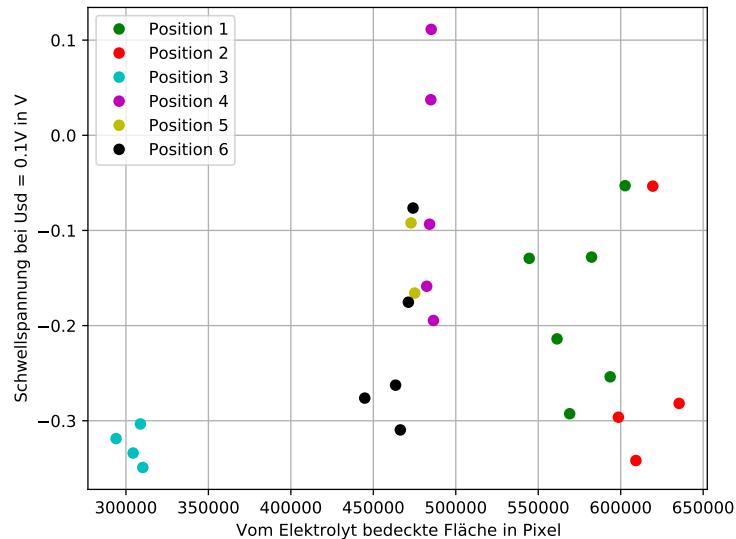

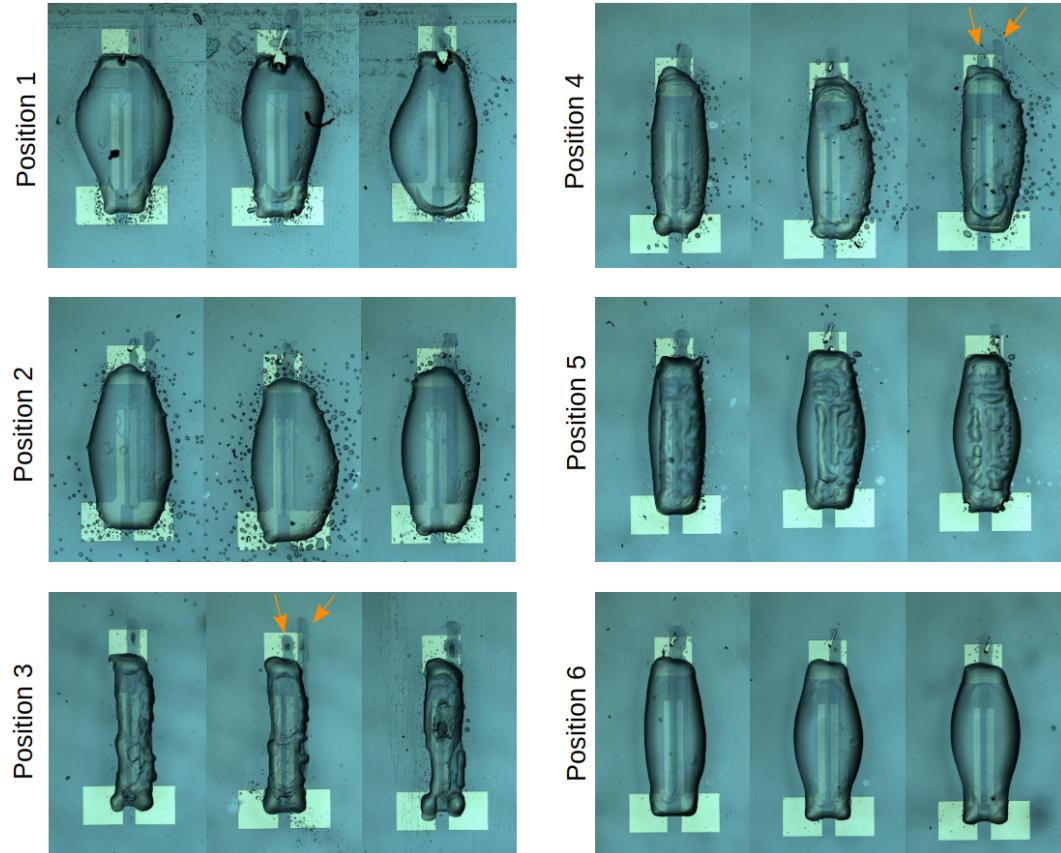

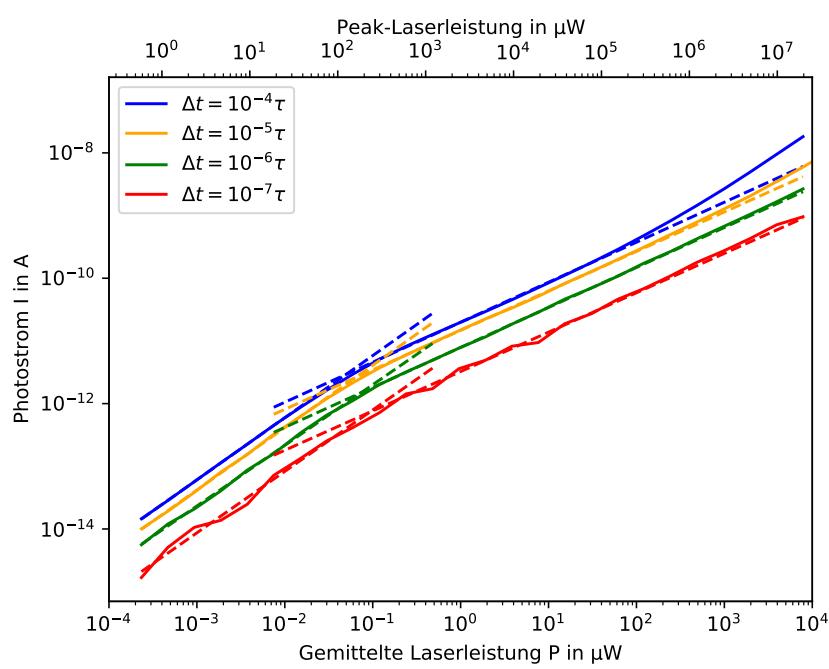

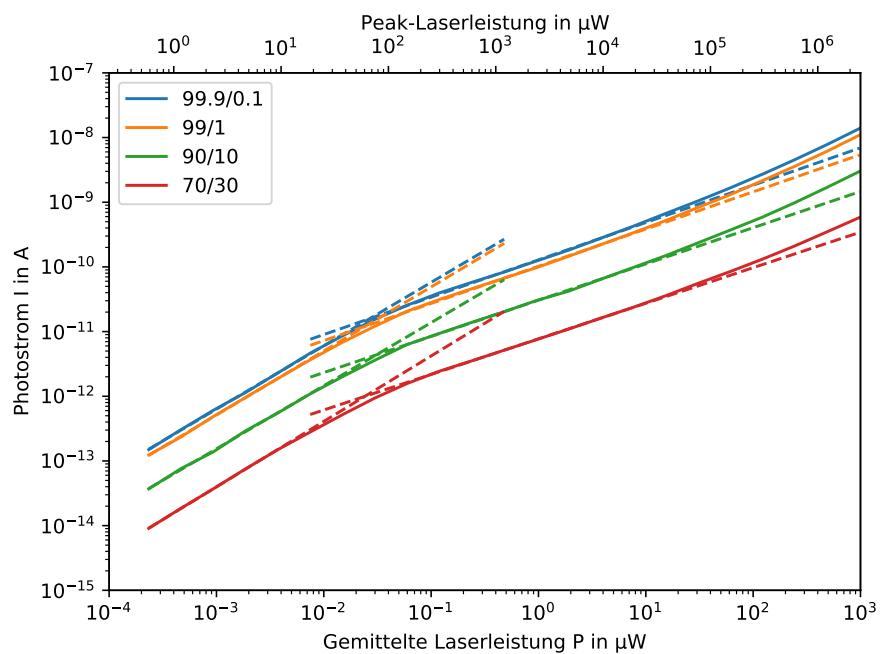

Implementiert wurde das Programm zur Strukturbildung des gedruckten Halbleitermaterials in Python. Das Skript vertauscht in einem MC-Schritt zufällige nächste Nachbarn im 2D-Gitter und akzeptiert die Vertauschung basierend auf dem Metropolis-Akzeptanzkriterium (Gl. 2.6) mit der Temperatur nach Gl. 3.2. Die Datenstrukturen der Simulation verwenden die optimierte numerische Bibliothek numpy[121]. Teile des Codes basieren lose auf einem MC-Code von Pascal Friederich, der realistische 3D-Strukturen von Solarzellen aus 2D-TEM-Aufnahmen erstellt[118].