# Ultra-fast Data Acquisition System for Coherent Synchrotron Radiation with Terahertz Detectors

M. Caselle, S. Cilingaryan, M. Hofherr, V. Judin, A. Kopmann, A.-S. Müller, M. Siegel, N. J. Smale, P. Thoma, M. Weber, S. Wuensch

Karlsruhe Institute of Technology – author email: michele.caselle@kit.edu

# Fast detector systems with picosecond time resolution

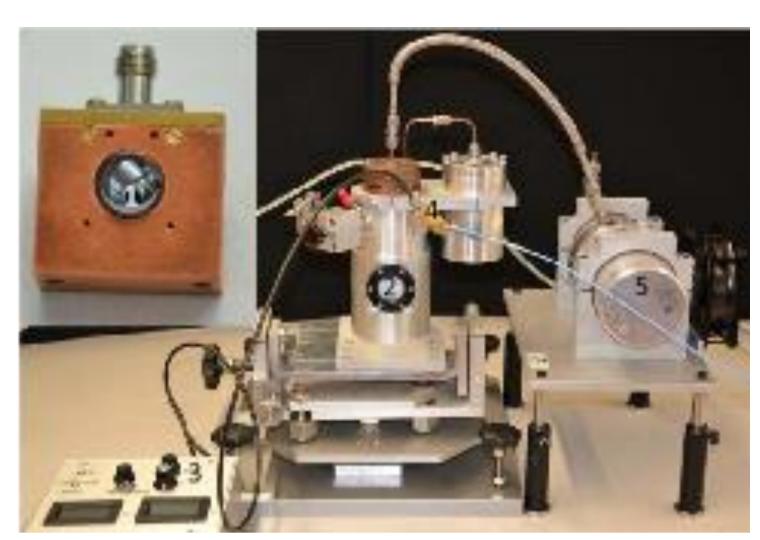

### The HEB detector system

- joint development of IMS (Karlsruhe) & DLR (Berlin)

- SC niobium nitride detector

- response time < 165 ps

- spectral range 150 GHz 1.5 THz

- study of single and multiple bunches

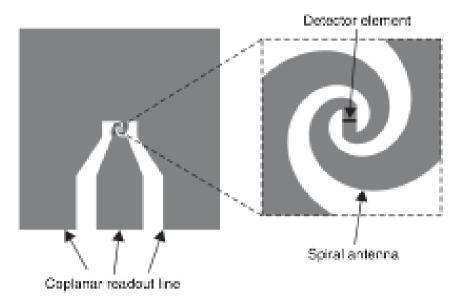

## YBCO-THz Detector System

- Yttrium-Barium-Copper-Oxid detector

- based on: YBa<sub>2</sub>Cu<sub>3</sub>O<sub>7-δ</sub> high-T SC

- response time: down to 1 ps spectral range: depends on antenna

Probst et al.

PHYSICAL

REVIEW B

85, 174511

(2012)

P. Thoma et al., IEEE Trans. on App. Supercond. 2012 DOI: 10.1109/TTHZ.2012.223420

# Ultra-fast FPGA digitizer board for ANKA

P. Thoma et al., Appl. Phys. Lett. 101, 2012

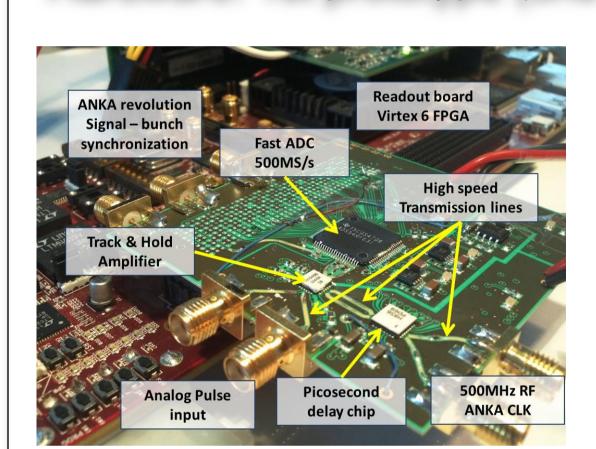

### Hardware: 1st prototype (one channel sampling board)

The time characterization has been

achieved by a sequential equivalent time

sampling method where one sample per

pulse is taken after a very short but well

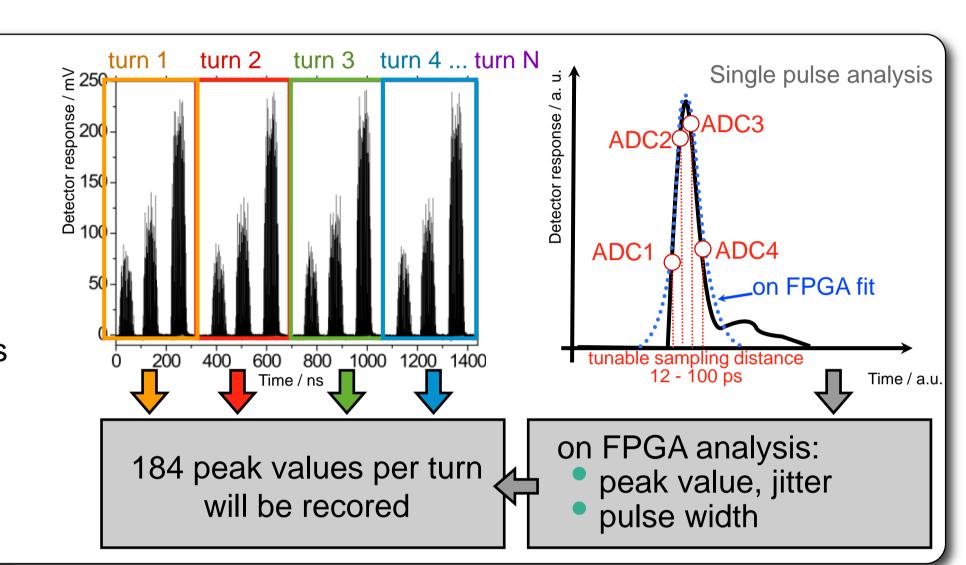

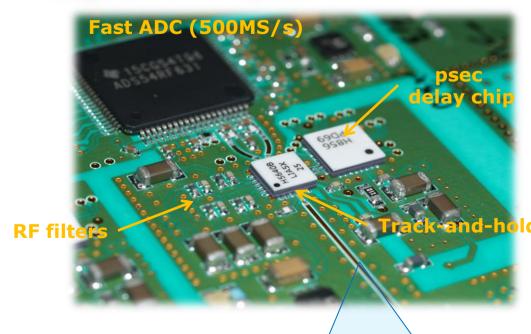

The first prototype contains a single sampling channel operating at 500 MS/s. The track-and-hold amplifier receives the analog pulse and acquires one sample in the peaking time region of each THz pulse (resp. CSR bunch emission).

Pulse shape vs Samples

Pulse shape

(width about 200ps)

Pulse measured

with oscilloscope

(Bandwidth 2.5GHz - 20GS/s)

Due to limited bandwidth

(Sampling board)

90 ps

Time in (sec)

x 10<sup>-10</sup>

# Design goals

- simultaneous monitoring of all 184 buckets

- turn-by-turn acquisition

- continuous acquisition up to ~3·10<sup>5</sup> turns

- fixed reference bucket for all measurements

- online analysis on FPGA/GPU

- control system Graphic User Interface

- Real-time data analysis

defined delay.

A.S: Müller, M. Caselle et al., proceeding of 4<sup>th</sup> International Particle Accelerator Conference, 12-17 May. MOPEA019

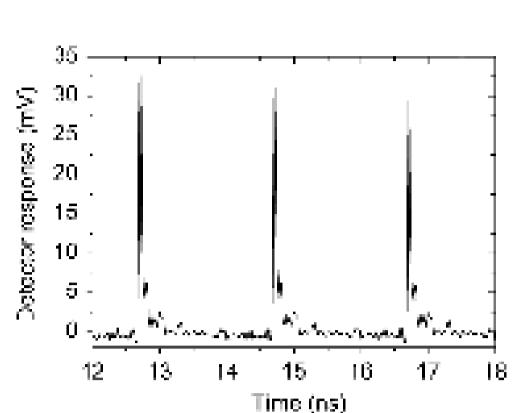

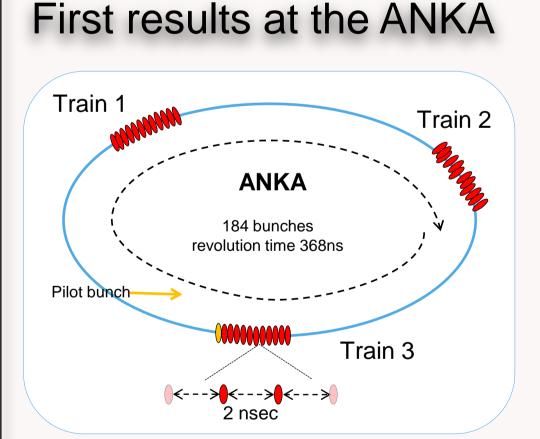

At the synchrotron light source, ANKA, up to 184 RF buckets can be filled with electrons with the distance between two adjacent buckets of 2 ns corresponding to the 500 MHz frequency of the RF system.

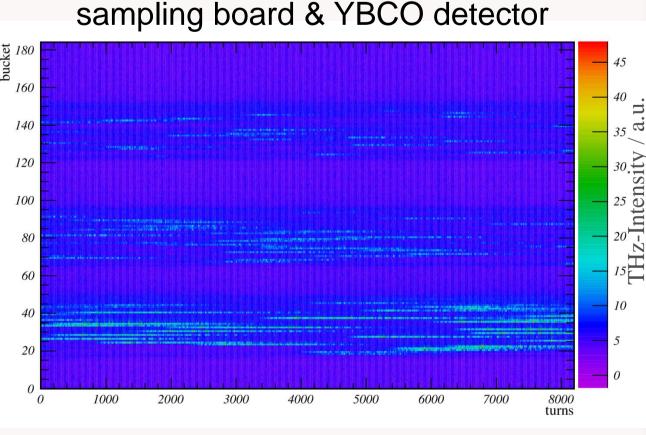

ANKA CSR measured with one channel sampling board & YBCO detector

This shows the typical filling pattern of the ANKA storage ring, consisting of three trains separated by a several ns gap. The prototype system is able to resolve single bunch fluctuation in a multi-bunch filling pattern.

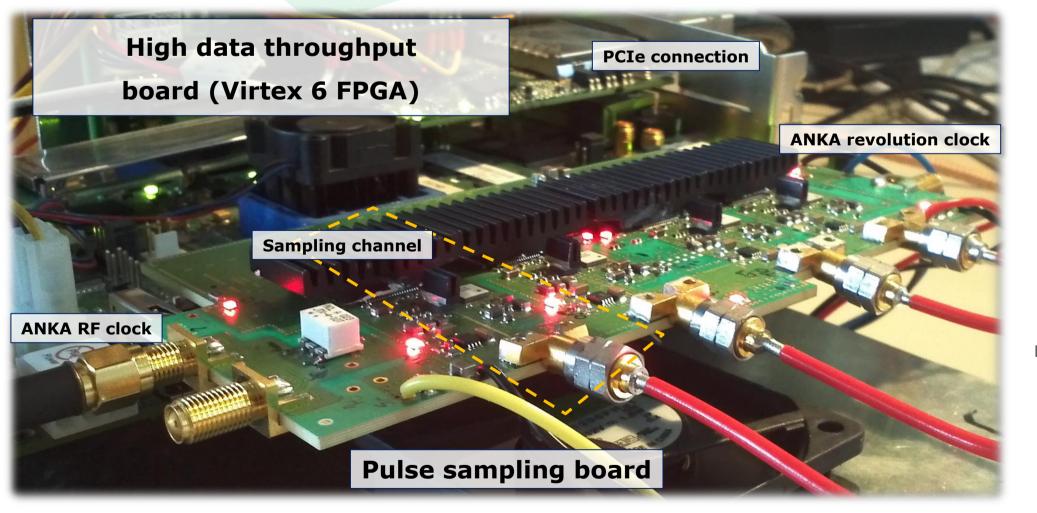

# Four sampling channels board

M. Caselle et al., proceeding of 4th International Particle Accelerator Conference, 12-17 May. WEOBB202

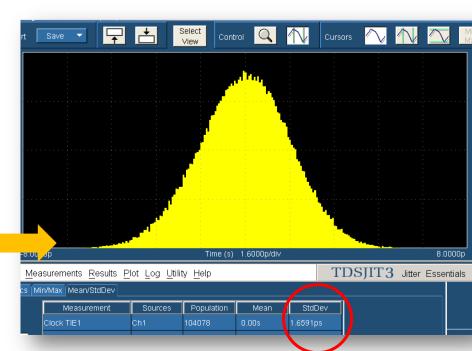

- A clean jitter phase locked loop (PLL) used to generate a clock signal with high temporal accuracy.

- 2. Clock is distributed to the picoseconds delay chips by a low skew and jitter clock fanout.

- 3. The track-and-holds receive a time controlled sampling signals synchronized with the ANKA RF-clock (resp. bunches time distribution).

- 4. Each delay chip is individually programmable from 3 to 100 ps.

- 5. 12 bits ADC resolution

A high data throughput readout based on a bus master DMA architecture connected to PCI Express. Data throughput of up 4 GByte/s.

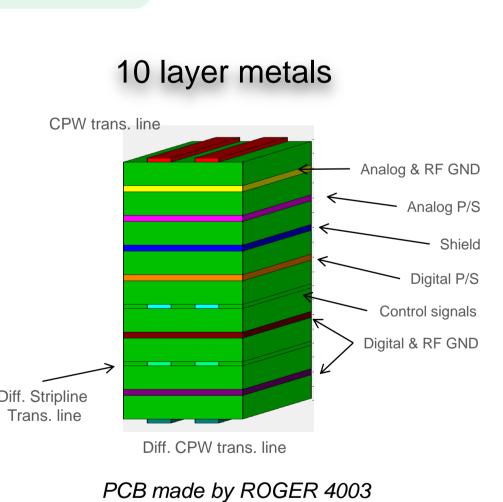

### Layout techniques ..

Separation of analog and digital grounds

Ad-hoc RF filters located closer to critical components

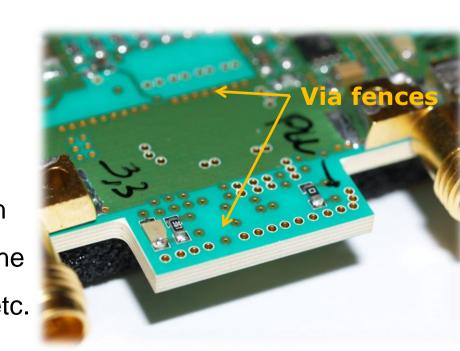

Via fences and guard ring techniques have been

employed in the PCB layout in order to reduce the cross-talk, electromagnetic interference (EMI), etc.

laminate for microwave/RF

applications

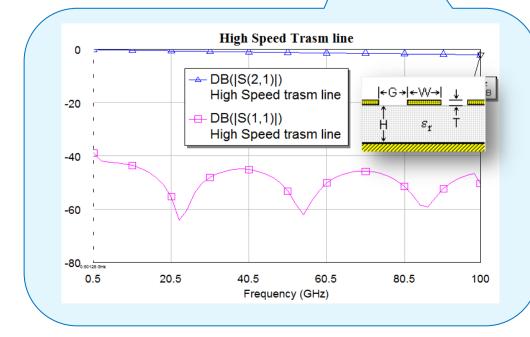

### CPW transmission line

### Board performances ..

| Dynamic range                 | ± 800mV  |

|-------------------------------|----------|

| Incoming pulse frequency      | 500 MHz  |

| Minimum sampling time         | 3 ps     |

| Number of samples (per pulse) | 4        |

| Total RMS period jitter       | < 1.7 ps |

| Noise RMS                     | 2 mV     |

# Summary and Outlook:

- Measurements using 1st prototype of FPGA board successful

- Open up new possibilities in the CSR diagnostics

- Test beam with the 4-channel board scheduled for October 2013

- Final aim: studies of correlations on the bursting pattern and interactions of very short pulses in the synchrotron storage rings