# Automatische Einstellung des Parallelitätsgrades von Programmen

Zur Erlangung des akademischen Grades eines

#### Doktors der Ingenieurwissenschaften

der Fakultät für Informatik der Universität Karlsruhe (Technische Hochschule) genehmigte

### Dissertation

von

Otilia Werner-Kytölä

aus São Sebastião do Caí, Brasilien

Tag der mündlichen Prüfung: 19. Oktober 1999

Erster Gutachter: Prof. Dr. Walter F. Tichy Zweiter Gutachter: Prof. Dr. Theo Ungerer

## Danksagung

Herr Prof. Tichy, vielen Dank für die Übernahme des Hauptreferats und für die Gelegenheit, an Ihrem Lehrstuhl meine Doktorarbeit durchführen zu dürfen. Ferner möchte ich mich bei Ihnen für die zahlreichen fruchtbaren Diskussionen in allen Phasen meiner Arbeit und für die kritische Durchsicht meiner Dissertation bedanken.

Herr Prof. Ungerer, vielen Dank für die Übernahme des Korreferats, für das Interesse an meiner Arbeit sowie für die wertvollen Verbesserungsvorschläge.

Michael, vielen Dank für das kritische Durchlesen in der früheren Phase des Zusammenschreibens.

Matthias, vielen Dank für die vielen fachlichen Diskussionen und für die gemeinsame Zeit auf der "Welt der Cray T3E".

Timo, vielen, vielen Dank für alles.

Barbara, vielen Dank für das Zusammenhalten in allen diesen Jahren und auch für alle die "Wie-sagt-man-das-auf-Deutsch"-Stunden.

Pai, muito obrigada pelo incentivo em todos estes anos e pela regra do " não te mixa".

Olga, muito obrigada pelo apoio desde o início da minha chegada à Alemanha e pela eterna torcida para que tudo desse certo!

Diana, Soraia, Sonc, Schultz, Val, Lu, Rafa, valeu pela forca!

CNPq, muito obrigada pelo auxílio financeiro durante quatro anos do meu doutorado no exterior.

Otilia Werner-Kytölä

Karlsruhe, im Oktober 1999.

# Inhaltsverzeichnis

| $\mathbf{D}$ | anks         | agung                                                      | I  |

|--------------|--------------|------------------------------------------------------------|----|

| Zι           | ısam         | menfassung                                                 | VI |

| 1            |              | führung                                                    | 1  |

|              | 1.1          | Motivation                                                 | 1  |

|              | 1.2          | Ziel der Dissertation                                      | 3  |

|              | 1.3          | Beiträge dieser Arbeit                                     | 3  |

|              | 1.4          | Aufbau der Arbeit                                          | 5  |

| 2            | Gru          | ındlagen                                                   | 7  |

|              | 2.1          | Parallelrechner                                            | 7  |

|              | 2.2          | Architekturmodelle                                         | 7  |

|              | 2.3          | Parallele Programmiermodelle                               | 9  |

|              | 2.4          | Charakterisierung paralleler Programme                     | 11 |

|              | 2.5          | Modellierung der Leistung paralleler Programme             | 15 |

|              |              | 2.5.1 Das Amdahl'sche Gesetz                               | 15 |

|              |              | 2.5.2 Asymptotische Analyse                                | 16 |

|              |              | 2.5.3 Planbare Algorithmen                                 | 17 |

|              |              | 2.5.4 Methode nach Foster                                  | 17 |

|              | 2.6          | Entwurf paralleler Software                                | 18 |

| 3            | Star         | nd der Forschung                                           | 21 |

|              | 3.1          | Verbesserung der Auslastung von Parallelrechnern           | 21 |

|              | 3.2          | Verbesserung der Leistung paralleler Programme             | 25 |

|              | 3.3          | Kombinierte Verbesserung der Auslastung und Leistung       | 26 |

|              | 3.4          | Einordnung und Vergleich der Arbeiten                      | 27 |

| 4            | $Th\epsilon$ | eoretische Modellbildung                                   | 29 |

|              | 4.1          | Methode                                                    | 29 |

|              | 4.2          | Klassifizierung von Programmen                             | 32 |

|              | 4.3          | Analyse von Programmklassen                                | 32 |

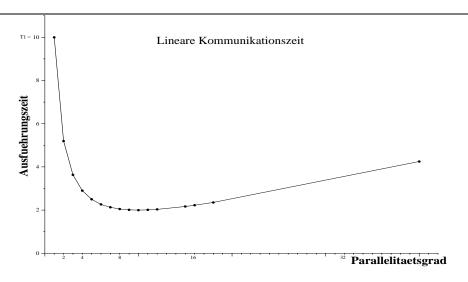

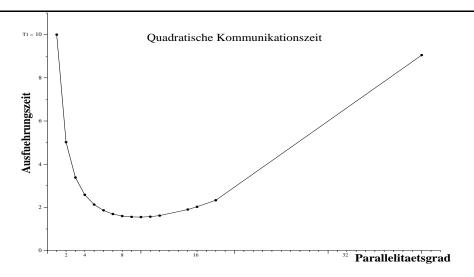

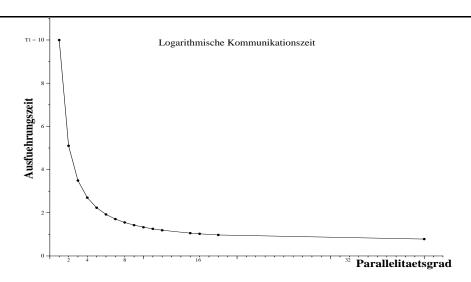

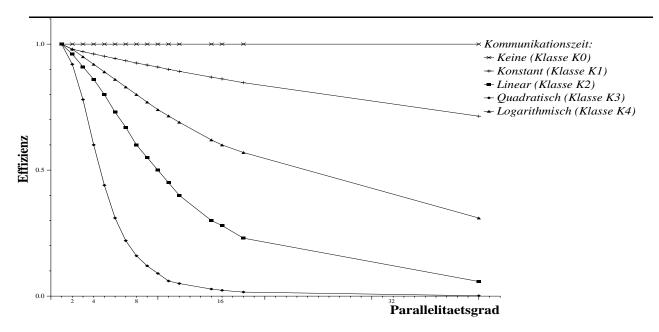

|              |              | 4.3.1 Analyse in Hinblick auf die Ausführungszeit          | 33 |

|              |              | 4.3.2 Analyse in Hinblick auf die Effizienz                | 35 |

|              |              | 4.3.3 Analyse in Hinblick auf das Nutzen-Kosten-Verhältnis | 37 |

|              | 4.4          | Das Amdahl'sche Gesetz im Nutzen-Kosten-Verhältnis         | 41 |

|              | 4.5          | Diskussion der theoretischen Modellbildung                 | 42 |

| 5 | $\mathbf{Aut}$ | omatische Bestimmung des Parallelitätsgrades                                                                                                     | 45 |

|---|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | 5.1            | Randbedingungen und Aufgaben                                                                                                                     | 45 |

|   | 5.2            | Szenario der Einstellung des Parallelitätsgrades                                                                                                 | 48 |

|   | 5.3            | Festlegung der Stellen für die Einstellung                                                                                                       | 49 |

|   | 5.4            | Suchverfahren zur Parallelitätsgradbestimmung                                                                                                    | 50 |

|   | 5.5            | Strategien für die Einstellung des Parallelitätsgrades                                                                                           | 50 |

|   | 0.0            | 5.5.1 Lokale Strategien                                                                                                                          | 51 |

|   |                | 5.5.2 Globale Strategien                                                                                                                         | 54 |

|   |                | 5.5.3 Übersicht über die Strategien                                                                                                              | 55 |

|   | 5.6            | Laufzeitinformationen und Messungen                                                                                                              | 55 |

|   | 5.7            |                                                                                                                                                  | 56 |

|   | 5.7            | Datenumverteilung                                                                                                                                |    |

|   |                | 5.7.1 Grundidee                                                                                                                                  | 56 |

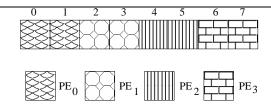

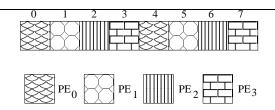

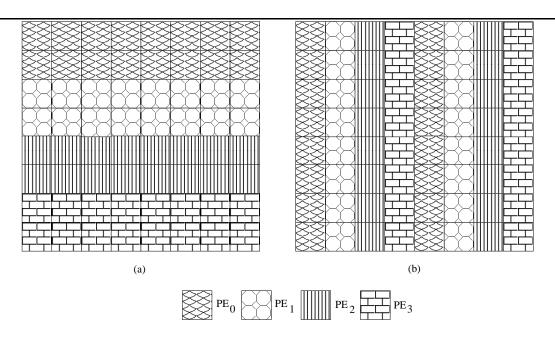

|   |                | 5.7.2 Arten der Datenverteilung                                                                                                                  | 57 |

|   |                | 5.7.3 Unterstützte Datenstrukturen                                                                                                               | 58 |

|   | 5.8            | Arten der Einstellung                                                                                                                            | 59 |

|   | 5.9            | Parallelitätsgrad-Datenbank                                                                                                                      | 61 |

| 6 | Doo            | licionuna                                                                                                                                        | 63 |

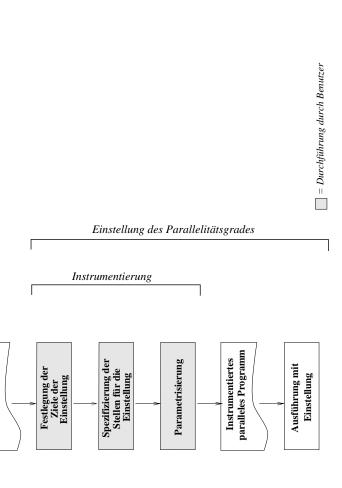

| U | 6.1            | lisierung<br>Szenario der Einstellung des Parallelitätsgrades                                                                                    | 63 |

|   | 6.2            |                                                                                                                                                  | 63 |

|   |                | Einschränkungen                                                                                                                                  | 64 |

|   | 6.3            | Verwendete Werkzeuge                                                                                                                             |    |

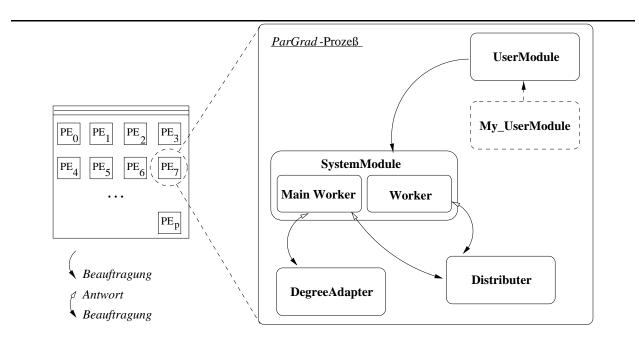

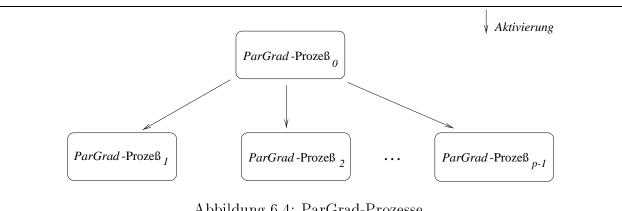

|   | 6.4            | Prozeßarchitektur                                                                                                                                | 65 |

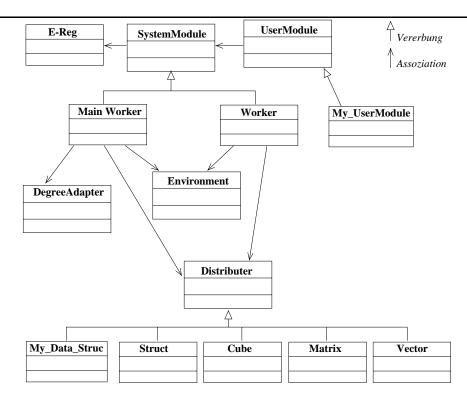

|   | 6.5            | Klassendiagramm                                                                                                                                  | 66 |

|   | 6.6            | Schnittstelle zwischen Benutzer und System                                                                                                       | 68 |

|   | 6.7            | Instrumentierung                                                                                                                                 | 68 |

|   |                | 6.7.1 Spezifizierung der Stellen für die Einstellung                                                                                             | 69 |

|   |                | 6.7.2 Spezifizierung der Parameter                                                                                                               | 70 |

|   |                | 6.7.3 Änderungen im Programm                                                                                                                     | 72 |

|   | 6.8            | Verwaltung der Einstellung des Parallelitätsgrades                                                                                               | 73 |

|   |                | 6.8.1 Grundidee                                                                                                                                  | 73 |

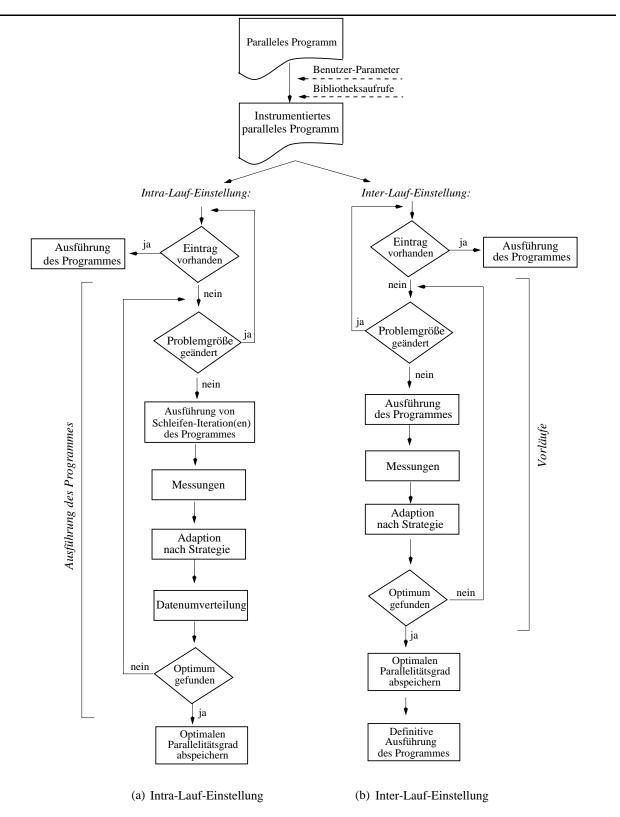

|   |                | 6.8.2 Intra-Lauf-Einstellung                                                                                                                     | 74 |

|   |                | 6.8.3 Inter-Lauf-Einstellung                                                                                                                     | 75 |

|   | 6.9            | Einstellung des Parallelitätsgrades                                                                                                              | 77 |

|   |                | 6.9.1 Grundidee                                                                                                                                  | 77 |

|   |                | 6.9.2 Algorithmen                                                                                                                                | 77 |

|   | 6.10           | Datenumverteilung                                                                                                                                | 78 |

|   |                | 6.10.1 Grundidee                                                                                                                                 | 78 |

|   |                | 6.10.2 Datenaustausch zwischen Worker                                                                                                            | 79 |

|   |                | 6.10.2.1 Export-Operation                                                                                                                        | 80 |

|   |                | 6.10.2.2 Import-Operation                                                                                                                        | 81 |

|   | 6 11           | Ausgabe der Einstellung                                                                                                                          | 82 |

|   | 0.11           | Ausgabe der Einstehung                                                                                                                           | 02 |

| 7 | Erge           | ebnisse                                                                                                                                          | 87 |

|   | 7.1            | Benchmark-Sammlung                                                                                                                               | 87 |

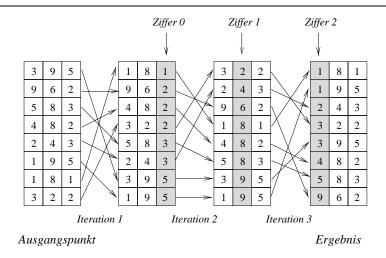

|   |                | 7.1.1 Radix-Sortieralgorithmus                                                                                                                   | 87 |

|   |                | 7.1.2 Livermore Loop 1 (LL1)                                                                                                                     | 89 |

|   |                | 7.1.3 Livermore Loop 3 (LL3) $\dots \dots \dots$ | 90 |

|   |                | 7.1.4 Livermore Loop 13 (LL13)                                                                                                                   | 90 |

|   |                | · · · · · ·                                                                                                                                      | -  |

|                   |               | 7.1.5   | Veltran-Operator                            | 91  |

|-------------------|---------------|---------|---------------------------------------------|-----|

|                   |               | 7.1.6   | TLM-Verfahren                               | 92  |

|                   | 7.0           | 7.1.7   | PDE-Löser                                   | 93  |

|                   | 7.2           |         | llung über das mathematische Modell         | 94  |

|                   |               | 7.2.1   | Validierungstechnik                         | 95  |

|                   |               | 7.2.2   | Programmklassen der Benchmark-Sammlung      | 95  |

|                   |               | 7.2.3   | Diskussion der Ergebnisse                   | 96  |

|                   |               |         | 7.2.3.1 LL1                                 | 97  |

|                   |               |         | 7.2.3.2 Radix-Sortieralgorithmus            | 98  |

|                   |               |         | 7.2.3.3 LL13                                | 99  |

|                   |               |         | 7.2.3.4 TLM-Verfahren                       | 100 |

|                   |               |         | 7.2.3.5 PDE-Löser                           | 101 |

|                   |               |         | 7.2.3.6 LL3                                 | 102 |

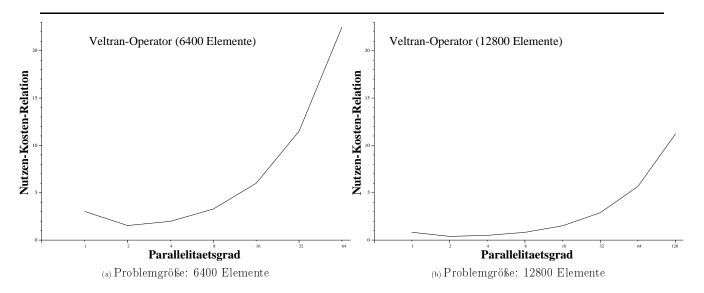

|                   |               |         | 7.2.3.7 Veltran-Operator                    | 103 |

|                   |               | 7.2.4   | Genauigkeit des mathematischen Modells      | 104 |

|                   |               | 7.2.5   | Extrapolation aus den erzielten Ergebnissen | 105 |

|                   | 7.3           | Einstel | llung über Suchverfahren                    | 106 |

|                   |               | 7.3.1   | Validierungstechnik                         | 106 |

|                   |               | 7.3.2   | Mehraufwand der Instrumentierung            | 106 |

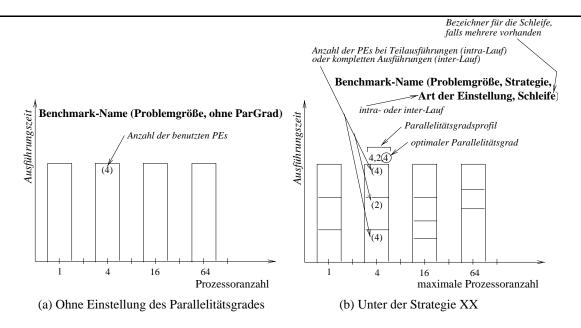

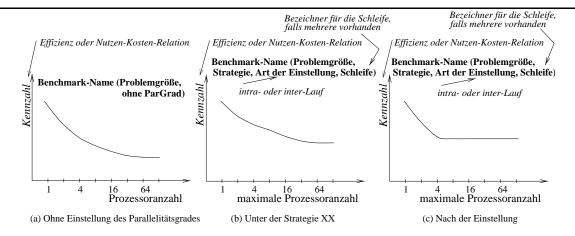

|                   |               | 7.3.3   | Zur Präsentation der Ergebnisse             | 107 |

|                   |               | 7.3.4   | Diskussion der Ergebnisse                   | 108 |

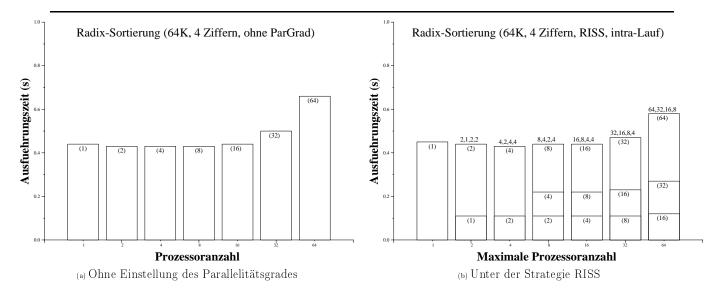

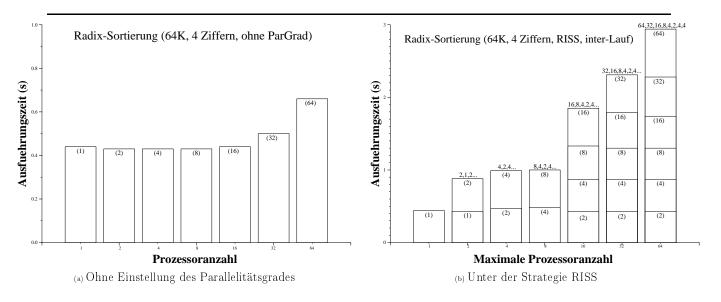

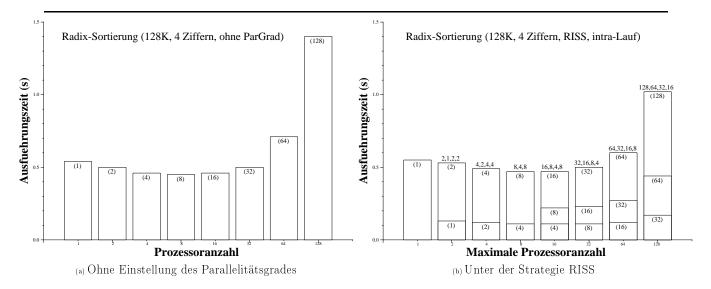

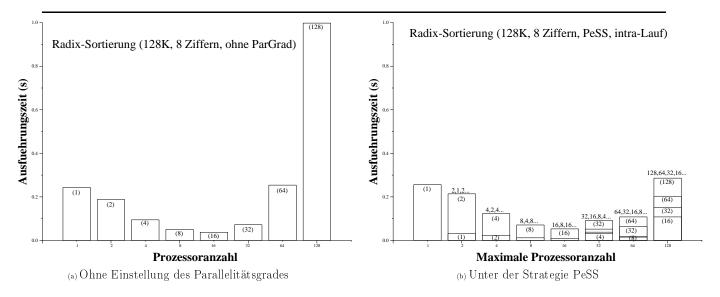

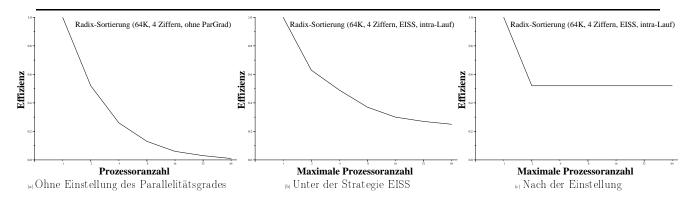

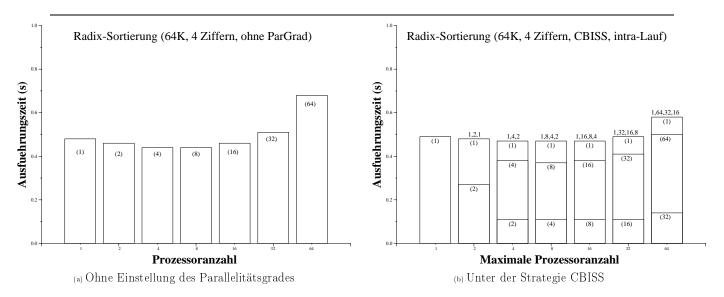

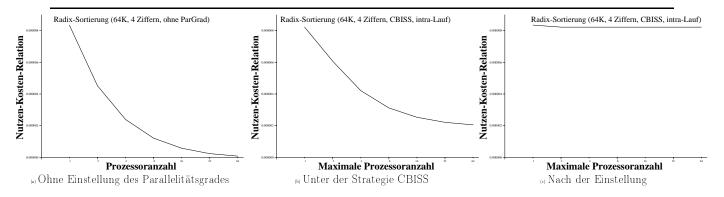

|                   |               |         | 7.3.4.1 Radix-Sortieralgorithmus            | 110 |

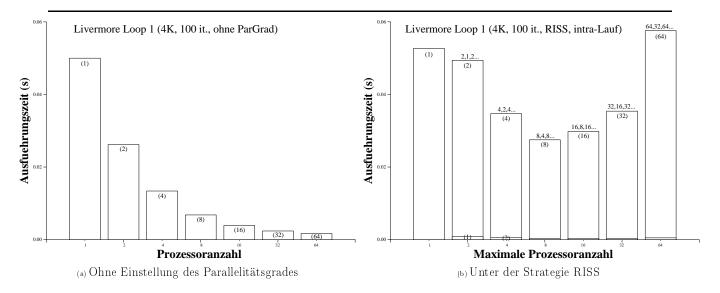

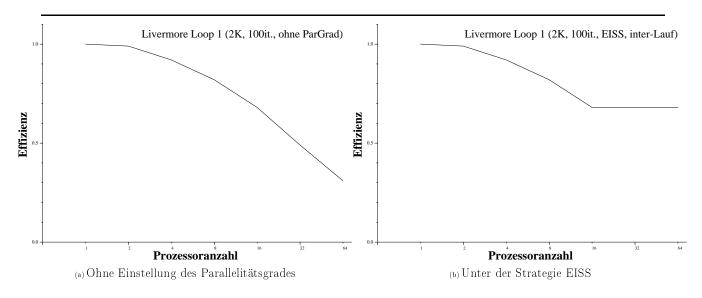

|                   |               |         | 7.3.4.2 Livermore Loop 1 (LL1)              | 114 |

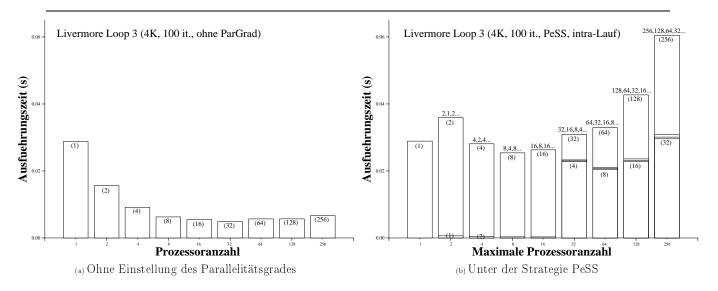

|                   |               |         | 7.3.4.3 Livermore Loop 3 (LL3)              | 115 |

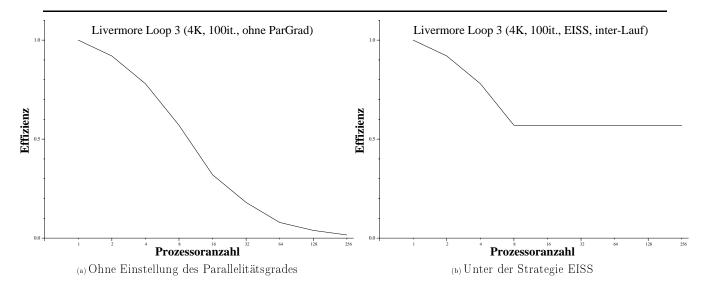

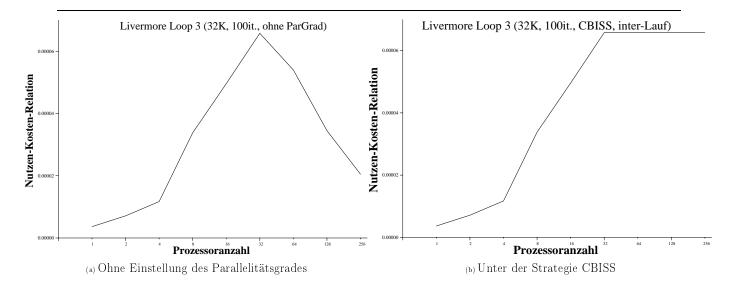

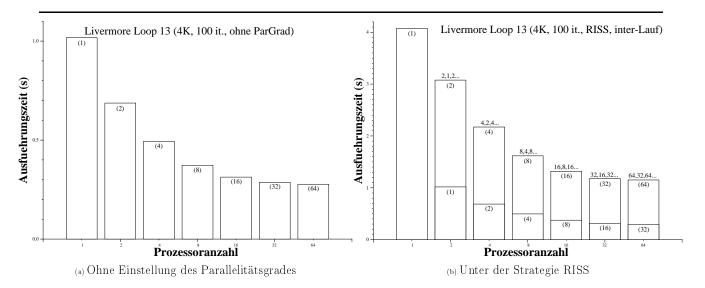

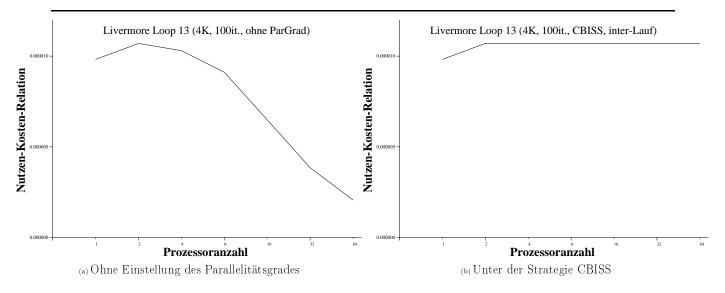

|                   |               |         | 7.3.4.4 Livermore Loop 13 (LL13)            | 118 |

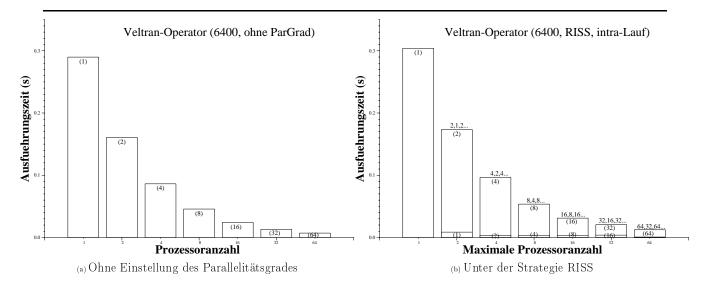

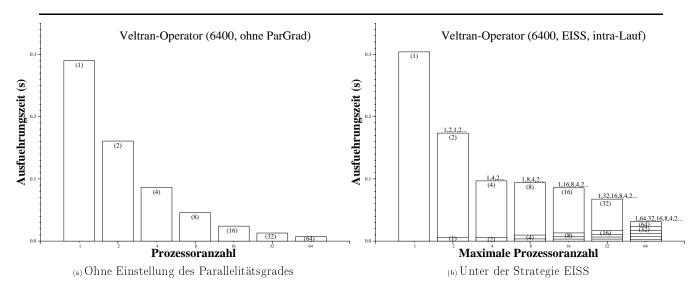

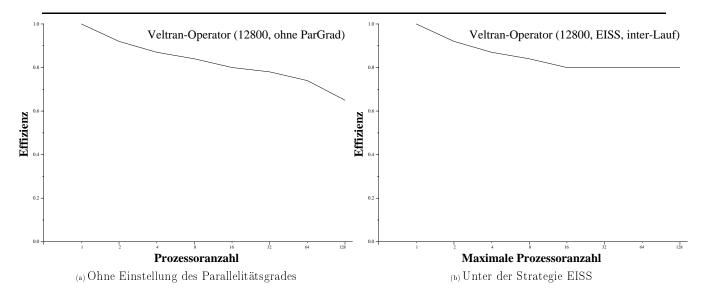

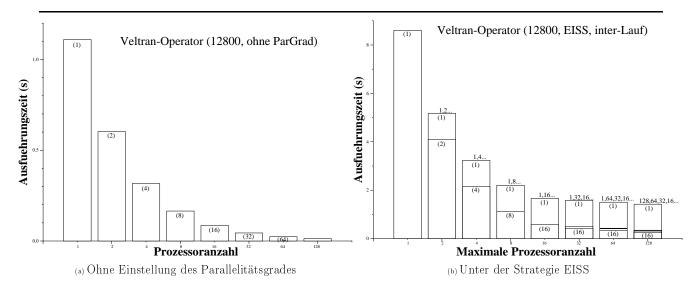

|                   |               |         | 7.3.4.5 Veltran-Operator                    | 120 |

|                   |               |         | 7.3.4.6 TLM-Verfahren                       | 124 |

|                   |               |         | 7.3.4.7 PDE-Löser                           | 127 |

|                   |               | 7.3.5   | Genauigkeit des Suchverfahrens              | 132 |

|                   |               | 7.3.6   | Extrapolation aus den erzielten Ergebnissen | 133 |

|                   | 7.4           | Verglei | ich der zwei Methoden                       | 134 |

| 8                 | Zusa          | ammer   | nfassung und Ausblick                       | 139 |

|                   | 8.1           | Beiträg | ge dieser Arbeit                            | 139 |

|                   | 8.2           | Ausbli  | ck auf zukünftige Forschung                 | 140 |

| $\mathbf{A}$      |               |         |                                             | 143 |

| Aı                | nhan          | g       |                                             | 143 |

| $\mathbf{Li}_{1}$ | $	ext{terat}$ | urverz  | eichnis                                     | 145 |

## Zusammenfassung

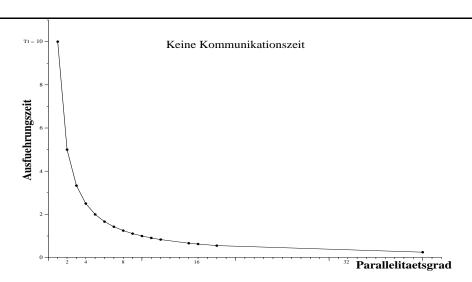

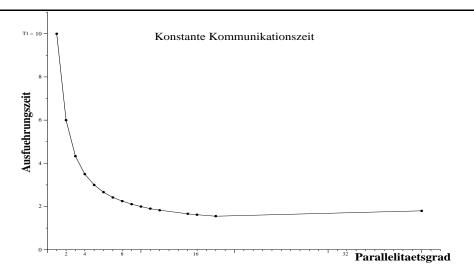

Einem parallelen Programm werden oft alle zur Verfügung stehenden Prozessoren eines Multiprozessorrechners zugeteilt. Diese Technik kann aber zu schlechten Ergebnissen führen, weil sie davon ausgeht, daß alle Prozessoren ausgenutzt werden können, was der Realität nicht unbedingt entspricht. Der Benutzer läßt auf dieser Weise seine Programme u.U. auf einer zu hohen Anzahl von Prozessoren laufen, wodurch sich die Ausführungszeit des Programmes durch die zusätzlichen Kommunikationskosten verlängert oder eine schlechte Auslastung des Rechners resultiert.

Diese Arbeit beschäftigt sich mit der automatischen Einstellung des Parallelitätsgrades von Programmen, wobei die optimale Anzahl von Prozessoren für ein paralleles Programm gesucht wird. Die Einstellung des Parallelitätsgrades verfolgt zwei Ziele:

- 1. Das Laufzeitverhalten, nämlich die Ausführungszeit, die Effizienz oder die Kosten-Nutzen-Relation von parallelen Programmen, die für ein mit verteiltem Speicher realisiertes Mehrprozessorsystem entwickelt wurden, soll verbessert werden. Die Verbesserung des Laufzeitverhaltens wird gegenüber der Ausführung des Programmes ohne Einstellung des Parallelitätsgrades gemessen, d.h. der Ausgangspunkt ist die Ausführung mit der vom Benutzer oder vom Betriebssystem ausgewählten Anzahl von Prozessoren.

- 2. Die Auslastung des Gesamtrechners soll verbessert werden. Einem parallelen Programm wird durch die Einstellung des Parallelitätsgrades eine maximale Prozessoranzahl zugeteilt, bei der die Effizienz nicht unterhalb einer vorgegebenen Schranke abfällt, oder so viele Prozessoren, daß die Kosten-Nutzen-Relation ihren minimalen Wert erreicht. Folge daraus ist, daß so viele Prozessoren wie möglich für die Ausführung weiterer, in das Mehrprozessorsystem kommender Programme freibleiben, was dem Benutzer letztendlich zugute kommt, da er dadurch z.B. mehrere Programme gleichzeitig laufen lassen kann.

In dieser Arbeit wurden zwei Methoden zur Bestimmung des optimalen Parallelitätsgrades entwickelt. Bei der ersten wird der Parallelitätsgrad durch ein mathematisches Modell ermittelt, während er bei der zweiten automatisch anhand eines Optimierungsverfahrens bestimmt wird.

Über das mathematische Modell wird der optimale Parallelitätsgrad anhand der Ausführungszeit, Effizienzschranke sowie Nutzen-Kosten-Relation approximiert, vorausgesetzt, der Kommunikations- und der Berechnungsaufwand der Programme sind bekannt. Diese Methode wurde auf sieben parallele Programme angewendet, wobei der Fehler im Durchschnitt ca. 13% betrug.

Bei der automatischen Einstellung des Parallelitätsgrades wird die Anzahl der in der Ausführung eines parallelen Programmes beteiligten Prozessoren solange nach einer gezielten Strategie verändert, bis das Programm nach angegebenen Kriterien optimal läuft. Die Einstellung wird entweder intra-Lauf oder inter-Lauf durchgeführt. Die erste findet innerhalb einer Ausführung des Programmes statt, während die zweite zwischen mehreren Ausführungen erfolgt. Bei den beiden Arten der Einstellung wird der Parallelitätsgrad anhand von Informationen eingestellt, die während der Laufzeit des Programmes aufgenommen werden.

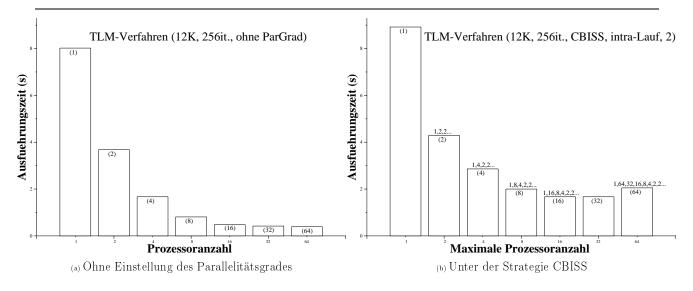

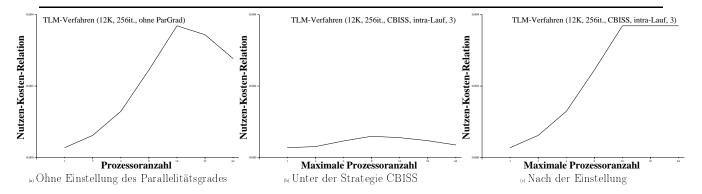

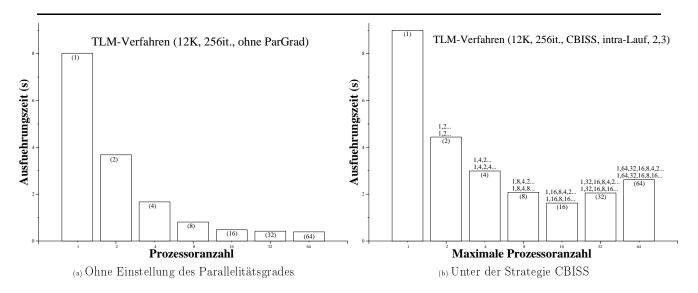

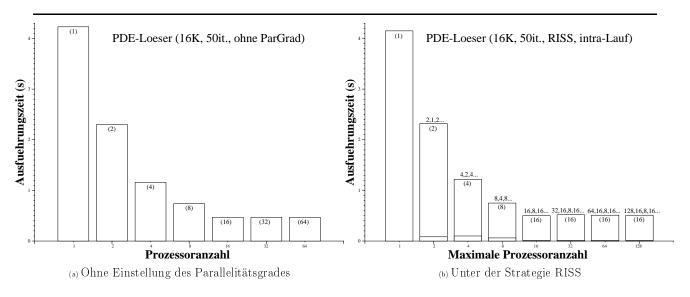

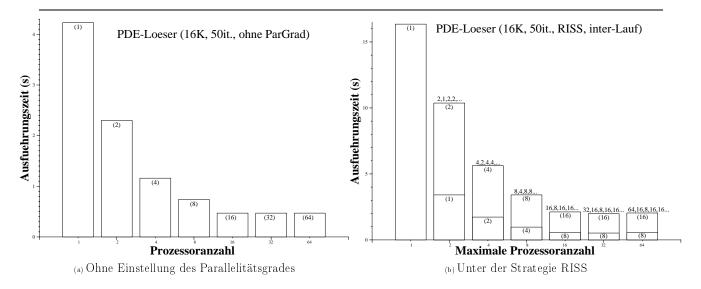

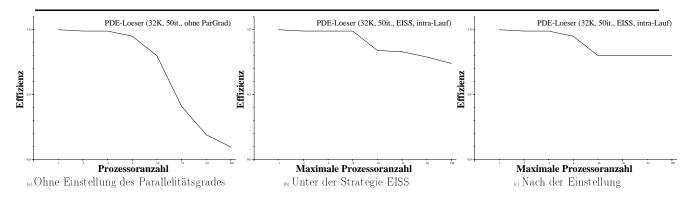

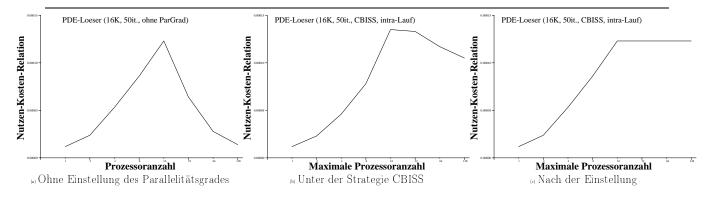

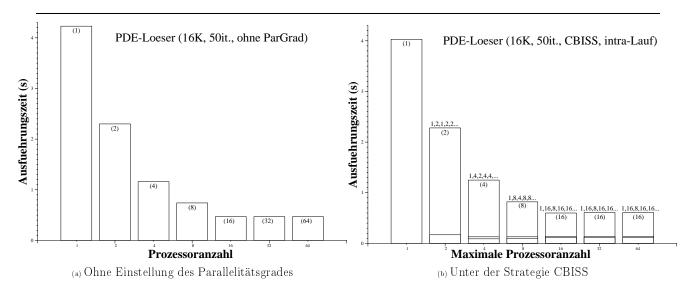

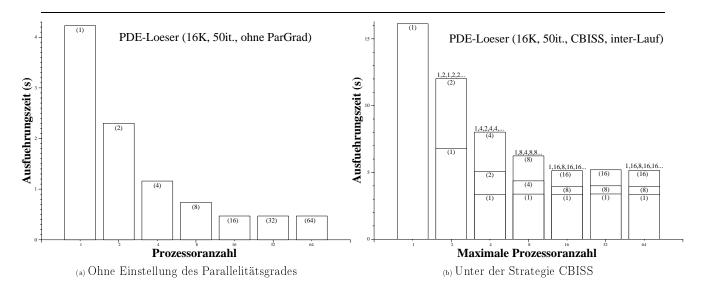

Die Methode zur automatischen Einstellung des Parallelitätsgrades wurde für die Cray T3E implementiert und an drei realen Anwendungen, drei der Livermore Loops sowie an einem Sortieralgorithmus bewertet. Die drei realen Anwendungen sind ein Operator aus der Geophysik, das TLM(Transmission Line Matrix)-Verfahren aus der Elektrotechnik und ein Löser partieller Differentialgleichungen (PDE). Als Ergebnis stieg die Effizienz bei dem geophysikalischen Operator um bis zu 24% bei einer vorgegebenen Effizienzschranke von 80%. Die Kosten-Nutzen-Relation hat ihr Minimum für das TLM-Verfahren erreicht, wobei sie um Faktor 2 bei der Einstellung des Parallelitätsgrades erniedrigt wurde. Bei der PDE-Anwendung wurde der Parallelitätsgrad, bei dem das Kosten-Nutzen-Verhältnis aufs Minimum gesetzt wurde, auf 16 Prozessoren eingestellt, wobei eine Inter-Lauf-Einstellung benutzt wurde. Bei dem Sortieralgorithmus wurde eine Reduktion der Ausführungszeit um bis zum Faktor 3,5 erzielt.

# Kapitel 1

# Einführung

Die Parallelrechnerei etabliert sich mehr und mehr als die effektive Lösung, wenn nach Rechenleistung gefragt wird. Seitens der Hardware bedeutet es, über eine Architektur zu verfügen, die aus vielen, gleichzeitig zu benutzenden Prozessoren besteht. Seitens der Software bedeutet es, ein Programm so zu strukturieren, daß es aus einer Menge unabhängiger Aktivitäten besteht.

Wenn man sich von der sequentiellen zu der parallelen "Welt" bewegt, ist eine Verbesserung der Leistung von Programmen bzw. die nicht-Verschlechterung der Auslastung des Gesamtsystems sowohl wegen der Hardware- als auch wegen der Software-Domäne nicht selbstverständlich. Beeinträchtigende Faktoren sind die Konkurrenz um gemeinsame Betriebsmittel, die zusätzlichen Kosten, die durch die Kommunikation zwischen Prozessoren entstehen, und die begrenzte Anzahl paralleler Aktivitäten, die das Programm anzubieten hat. Das Gewicht aller dieser Faktoren kann aber drastisch reduziert werden, wenn einem Programm nur so viele Prozessoren zugeordnet werden, wie es sinnvollerweise beschäftigen kann. Damit befaßt sich die vorliegende Arbeit.

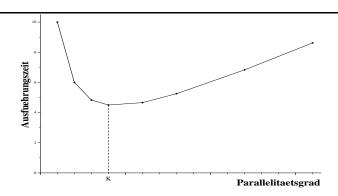

### 1.1 Motivation

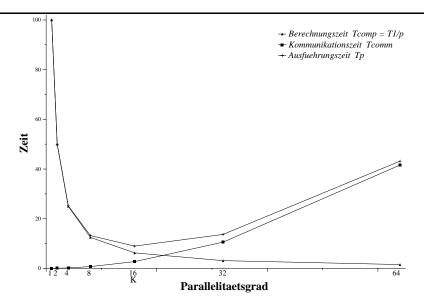

Sequentielle Programme werden parallelisiert, um ihre Ausführungszeiten zu verkürzen. Dieses Ziel wird jedoch oft nicht erreicht, weil der Parallelitätsgrad überdimensioniert wird. Es gibt immer einen Punkt, ab dem jeder zusätzliche, einem Programm zugeordnete Prozessor nicht mehr zu einer Verbesserung der Leistung beiträgt bzw. sogar zu einer Verschlechterung derselben führen kann. Gründe dafür sind einerseits die steigenden Kommunikationskosten, andererseits der Mangel an parallelen Aktivitäten seitens des Programmes. Daher ist die Bestimmung des Sättigungspunktes bzw. des optimalen Parallelitätsgrades des Programmes ein erstrebenswertes Ziel.

Ohne Unterstützung seitens des Systems nimmt der Benutzer normalerweise an, daß sein Programm besser parallelisierbar sei als es tatsächlich ist, und belegt dafür zu viele Prozessoren. Genauso belegt das Betriebssystem eines Mehrprozessorsystems häufig alle noch zur Verfügung stehenden Prozessoren für die Ausführung eines Programmes, ohne zu berücksichtigen, ob sich das überhaupt lohnt. Aus diesen Gründen ist eine automatische Bestimmung des optimalen Parallelitätsgrades eines Programmes sinnvoll.

Die Parallelisierung von Programmen geschieht immer häufiger automatisch. Systeme, die solche Programme instrumentieren bzw. umschreiben, liefern aber keinerlei Information über die Anzahl der zu belegenden Prozessoren, die z.B. zu einer erwünschten Beschleunigung führen würde. Diese Systeme können erfolgreich die parallelisierbaren Aktivitäten

in einem Programm identifizieren, sind aber mangelhaft in der Bestimmung des optimalen Parallelitätsgrades für ein Programm.

Ein weiteres zu berücksichtigendes Phänomen ist, daß der Parallelitätsgrad eines Programmes normalerweise in der Zeit variiert [28]. Die Folge daraus ist, daß auch, wenn z.B. das Programm mit einer geeigneten Anzahl von Prozessoren gestartet wurde, diese während der Ausführung des Programmes suboptimal werden kann. Dies geschieht dann, wenn das Programm in einer bestimmten Ausführungsphase weniger Parallelismus anzubieten hat oder wenn das Verhältnis zwischen Kommunikations- und Berechnungsaufwand zu hoch wird. Die Einstellung des Parallelitätsgrades ist auch daher während der Ausführung des Programmes anhand von Laufzeitinformationen notwendig.

Die Anpassung des Parallelitätsgrades ist nicht nur für das jeweils betrachtete Programm sehr wichtig, sondern auch für den Gesamtrechner. Es ist immer wünschenswert, daß das System gut ausgelastet bleibt. Wenn einige Prozessoren, die der Ausführung eines parallelen Programmes zugeordnet wurden, nicht mehr gut ausgelastet sind, sollten sie für die Ausführung anderer, in das Mehrprozessorsystem kommender Programme freigestellt werden. Das Erreichen einer guten Auslastung des Mehrprozessorsystems kommt auch dem Benutzer zugute. Im besten Fall wird die Ausführungszeit seines Programmes durch die Reduzierung der Anzahl von Prozessoren wegen der daraus entstandenen Erniedrigung der Kommunikationskosten verkürzt. Wenn das aber nicht der Fall ist, kann die Verbesserung der Auslastung dem Benutzer immer noch von Vorteil sein, indem die Gesamtausführungszeit mehrerer von ihm gleichzeitig gestarteter Programme reduziert wird.

Als Beispiel betrachten wir ein fiktives Programm A, das auf einem Parallelrechner ausgeführt wird, der insgesamt über 8 Prozessoren verfügt. Die Ausführungszeit des Programmes auf 4 Prozessoren (33s) ist 32% höher als auf 8 Prozessoren (25s), seine Effizienz steigt aber um 50%, wenn der Parallelitätsgrad von 8 auf 4 reduziert wird. Jedoch ist die benötigte Zeit für zwei aufeinanderfolgende Ausführungen dieses Programmes auf 4 Prozessoren 51% kleiner als wenn 8 Prozessoren eingesetzt werden, wie aus der Tabelle 1.1 unter Gesamtzeit herauszulesen ist. Dies liegt daran, daß beim Parallelitätsgrad 4 die zwei Ausführungen gleichzeitig erfolgen können, und beim Parallelitätsgrad 8 zwei aufeinanderfolgende Ausführungen benötigt werden. Bei 8 Läufen des Programmes liefert sogar ein Parallelitätsgrad von 1 die minimale Ausführungszeit, wobei sie 32% bzw. um Faktor 4 niedriger ist als beim Parallelitätsgrad 4 bzw. 8.

Parallelitätsgrad Ausführungszeit (s) Gesamtzeit (s) Beschleunigung Effizienz (1 Programmlauf) (2 Programmläufe) 100.0 1 100.0 1,00 1,00 33,0 33.0 4 3,03 0,758 0,50 50.0 25,0 4,00

Tabelle 1.1: Kennzahlen des fiktiven Programmes A

Ein weiteres Argument, warum eine gute Auslastung des Gesamtsystems auch dem Benutzer von Interesse ist, sind die bei der Benutzung mehrerer Prozessoren entstehenden Kosten. Der Benutzer eines Mehrprozessorsystems muß dem Betreiber für den Zugriff auf das System bezahlen, wobei sich die Kosten üblicherweise auf die benutzten Zeiteinheiten pro Prozessor beziehen. Wenn nur so viele Prozessoren alloziert werden wie die Program-

me des Benutzers gut auslasten können, werden den Programmen evtl. weniger Prozessoren zugeordnet. Daraus folgt, daß die Kosten für die Benutzung des Mehprozessorsystems ggf. verringert werden können. Auf der anderen Seite gibt es Rechenzentren, die eine ineffiziente Benutzung der zur Verfügung gestellten Resourcen bestrafen. Beispielsweise belastet ein Rechenzentrum Benutzer, die die Vektoreinheiten eines Vektorrechners kaum benutzen, viermal soviel wie Benutzer, die von den Vektoreinheiten intensiv Gebrauch machen. Auch in dieser Situation ist es wichtig, daß der Benutzer auf die Effizienz achtet.

Zusammenfassend läßt sich sagen, daß die automatische Einstellung des Parallelitätsgrades sinnvoll erscheint. Neben der Verbesserung des Laufzeitverhalten eines Programmes ist bei der Anpassung des Parallelitätsgrades ein weiteres Ziel von Interesse, nämlich das Erreichen einer guten Auslastung des Mehrprozessorsystems.

## 1.2 Ziel der Dissertation

Diese Dissertation verfolgt zwei Thesen:

These 1: Es ist möglich, den Parallelitätsgrad eines Programmes dynamisch einzustellen und eine Verbesserung des Laufzeitverhaltens von parallelen Programmen zu erreichen, die für ein mit verteiltem Speicher realisiertes Mehrprozessorsystem entwickelt wurden. Je nach Ziel der Einstellung entspricht das Laufzeitverhalten der Ausführungszeit, der Effizienz oder dem Kosten-Nutzen-Verhältnis. Die Verbesserung des Laufzeitverhaltens wird gegenüber der Ausführung des Programmes ohne Einstellung des Parallelitätsgrades gemessen, d.h. der Ausgangspunkt ist die Ausführung mit der vom Benutzer oder Betriebssystem ausgewählten Anzahl von Prozessoren.

These 2: Die Auslastung des Gesamtrechners kann durch die Einstellung des Parallelitätsgrades von Programmen verbessert werden. Einem parallelen Programm wird durch die Einstellung des Parallelitätsgrades eine maximale Prozessoranzahl zugeteilt, bei der die Effizienz eine vorgegebene Schranke nicht unterschreitet, oder so daß die Kosten-Nutzen-Relation ihren minimalen Wert erreicht. Folge daraus ist, daß so viele Prozessoren wie möglich für die Ausführung weiterer, in das Mehrprozessorsystem kommender Programme freibleiben, was dem Benutzer letztendlich zugute kommt.

Unter Kosten-Nutzen-Relation versteht man das Verhältnis zwischen den Kosten, die bei der Benutzung von mehr als einem Prozessor für die Ausführung eines Programmes entstehen, und dem Nutzen, der wiederum dem Verhältnis zwischen der Ausführungszeit des Programmes mit einem Prozessor und mit p Prozessoren entspricht, wobei p>1 gilt.

Das Ziel der vorliegenden Dissertation ist es, die o.g. Thesen zu belegen. Dafür wird ein Modell zur Bestimmung des optimalen Parallelitätsgrades entwickelt und anhand eines Experimentiersystems sowie realer Anwendungen validiert.

### 1.3 Beiträge dieser Arbeit

Die vorliegende Arbeit ist die erste, die sich systematisch mit der automatischen Einstellung des Parallelitätsgrades auf Rechnern mit verteiltem Speicher beschäftigt hat. Die zwei präsentierten Thesen werden belegt, d.h. das Laufzeitverhalten paralleler Programme bzw.

die Auslastung des Gesamtrechners kann verbessert werden. Diese Aussage basiert auf der Untersuchung von drei realen Anwendungen, einem Sortieralgorithmus und drei der Livermore Loops.

Ein mathematisches Modell für die Berechnung des optimalen Parallelitätsgrades wurde entwickelt und anhand einer Benchmark-Sammlung mit sieben Programmen validiert. Das mathematische Modell ist fähig, den nach der Ausführungszeit, Effizienz sowie der Kosten-Nutzen-Relation optimalen Parallelitätsgrad zu approximieren. Bis auf einige Situationen, die in Abschnitt 7.2.3 beschrieben werden, bleibt die Auswirkung der Abweichung zwischen dem gemessenen und dem berechneten optimalen Parallelitätsgrad gering, nämlich im Durchschnitt ca. 13%.

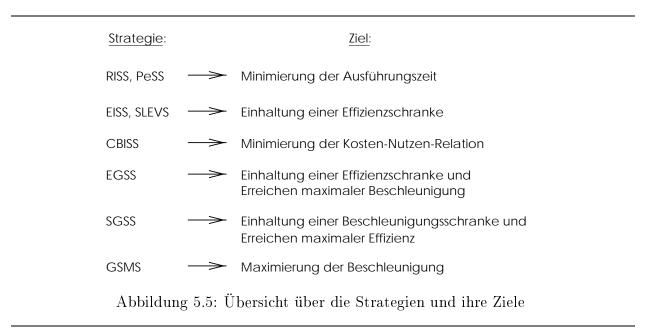

Effiziente Strategien für die Optimierung unterschiedlicher Kennzahlen, wie die Ausführungszeit bzw. die Beschleunigung paralleler Programmen, die Effizienz oder die Kosten-Nutzen-Relation, werden entwickelt, implementiert und getestet. Insgesamt handelt es sich um acht Strategien, wobei drei komplett neu entwickelt wurden und fünf auf [45] basierend angepaßt bzw. weiterentwickelt wurden.

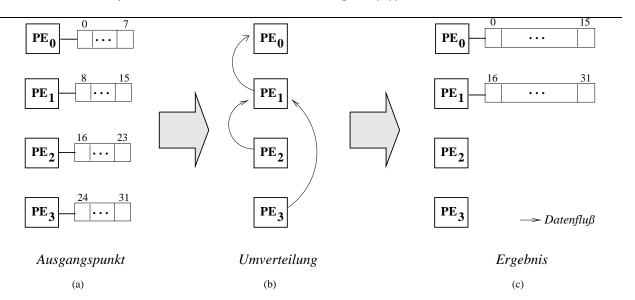

Ein Mechanismus für die Datenumverteilung verschiedener Datenstrukturen wurde entwickelt, implementiert und getestet. Die Datenumverteilung wurde so konzipiert, daß sie die Umverteilung unterschiedlicher Strukturen unterstüzt und auch einen Mechanismus vorsieht, wodurch der Benutzer leicht die Umverteilung neuer Datenstrukturen implementieren kann.

Es wurden zwei Arten der Einstellung des Parallelitätsgrade entwickelt, nämlich die Intra-Lauf- und die Inter-Lauf-Einstellung. Die beiden Möglichkeiten stehen dem Benutzer mittels der Bibliotheksroutinen zur Verfügung. Die erste Art der Einstellung findet innerhalb einer Ausführung des Programmes statt, während die zweite zwischen mehreren Läufen des Programmes geschieht. Vorteil der Inter-Lauf-Einstellung ist, daß dabei keine Datenumverteilung vorgenommen werden muß. So kann der Parallelitätsgrad auch von solchen Programmen eingestellt werden, deren Intra-Lauf-Einstellung wegen der Datenumverteilung mit sehr hohen Kosten verbunden wäre.

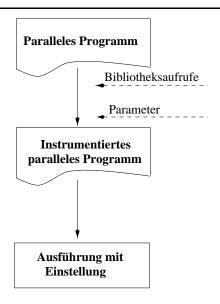

Im Rahmen dieser Arbeit wurde auch das System ParGrad entwickelt, das die automatische Einstellung des Parallelitätsgrades von in C++ geschriebenen Programmen auf einer Cray T3E, einem Parallelrechner mit verteiltem Speicher, realisiert. Das System steht dem Benutzer als eine Bibliothek zur Verfügung. Der Benutzer instrumentiert sein paralleles Programm durch das Einfügen von Aufrufen von Bibliotheksroutinen und die Spezifizierung einiger Parameter, wie die Einstellungsstrategie oder die umzuverteilenden Datenstrukturen. Nach der Instrumentierung läuft das Programm mit der Einstellung des Parallelitätsgrades. Drei Anwendungen, ein Sortieralgorithmus und drei Kerne wurden mit dem System ParGrad auf die Einstellung des Parallelitätsgrades hin untersucht. Die Anwendungen sind ein Operator aus der Geophysik, das TLM(Transmission Line Matrix)-Verfahren, ein Löser partieller Differentialgleichungen (PDE, Partial Differential Equation) und ein Sortieralgorithmus. Bei dem Sortieralgorithmus wurde eine Reduzierung der Ausführungszeit bis zum Faktor 3,5 erzielt. Die Effizienz wurde bei dem geophysikalischen Operator um bis zu 24% höher. Das Kosten-Nutzen-Verhältnis ist um Faktor 2 bei dem TLM-Verfahren gesunken. Bei der PDE-Anwendung konnte das Kosten-Nutzen-Verhältnis minimiert werden, wobei unter der Benutzung der Inter-Lauf-Einstellung der Parallelitätsgrad auf 16 Prozessoren eingestellt wurde.

### 1.4 Aufbau der Arbeit

Diese Arbeit besteht aus sieben weiteren Kapiteln. Kapitel 2 beschreibt die für die Arbeit relevanten Grundlagen von Parallelrechnern, Architekturmodellen, Programmier- und Leistungsmodellen für Parallelrechner und gibt eine Charakterisierung paralleler Programme. Im Kapitel 3 wird der Stand der Forschung vorgestellt, wobei Arbeiten aus drei Gebieten präsentiert und mit der vorliegenden Arbeit verglichen werden. Danach wird im Kapitel 4 über die theoretische Modellbildung zur Ermittlung des Parallelitätsgrades diskutiert. Im Kapitel 5 findet die Beschreibung des im Rahmen dieser Arbeit entwickelten Modells zur automatischen Bestimmung des optimalen Parallelitätsgrades eines Programmes statt. Basierend darauf befaßt sich Kapitel 6 mit der Realisierung der automatischen Einstellung des Parallelitätsgrades; das daraus entstandene System ParGrad wird vorgestellt. Die durch die Einstellung des Parallelitätsgrades von Programmen erzielten Ergebnisse und der Nachweis der von der vorliegenden Arbeit verfolgten Thesen werden im Kapitel 7 präsentiert. Kapitel 8 faßt nochmals die wichtigsten Ergebnisse zusammen und gibt einen Ausblick auf weitere Arbeiten.

# Kapitel 2

# Grundlagen

In diesem Kapitel werden die für die Arbeit relevanten Grundlagen beschrieben. Hier werden Parallelrechner bzw. die unterschiedlichen Architekturmodelle präsentiert, Programmierund Leistungsmodelle für Parallelrechner diskutiert, eine Charakterisierung paralleler Programme vorgestellt und den Entwurf paralleler Software besprochen.

### 2.1 Parallelrechner

Die Leistung der schnellsten Rechner ist seit dem Jahr 1945 bis heutzutage exponentiell gewachsen [21], durschnittlich um Faktor 10 alle fünf Jahre. Auf der anderen Seite steigt die Taktrate, die die Ausführungszeit des primitivsten Befehls letzendlich bestimmt, derzeit langsam, wobei eine Tendenz zur Annäherung an die physikalische Grenze beobachtet werden kann. Diese physikalische Grenze wird durch die Lichtgeschwindigkeit vorgegeben. Um über die gegenwärtig verfügbare Einzelprozessorleistung hinauszugehen, wird die Parallelverarbeitung eingesetzt. Dafür werden verschiedene Techniken bei dem Rechnerentwurf eingeführt: "Fließband-Bearbeitung" von Befehlen (pipelining), Einsatz mehrerer Ausführungseinheiten (z.B. Gleitkommaeinheit) oder der Einsatz mehrerer Prozessoren. Rechner, die aus einer Menge von Prozessoren bestehen, und zur Lösung eines Problems kooperieren, nennen sich Parallelrechner.

Parallelrechner unterscheiden sich nach Flynn [19] in SIMD- und MIMD-Architekturen. Rechner, die der SIMD (Single Instruction Multiple Data)-Kategorie gehören, sind fähig, denselben Programmbefehl gleichzeitig bezogen auf mehrere Datensätze auszuführen. MIMD (Multiple Instruction Multiple Data)-Rechner dagegen bearbeiten verschiedene Teile eines Programmes auf unterschiedlichen, voneinander unabhängigen Prozessoren. Die Programmierung von Parallelrechnern zweiter Art ist aufwendiger, weil die einzelnen Prozessoren miteinander kommunizieren müssen, um die parallel zu bearbeitenden Teilaufgaben miteinander abzustimmen und den Arbeitsfortschritt zu kontrollieren [52].

Im folgenden werden verschiedene Architektur- und Programmiermodelle für Parallelrechner präsentiert.

### 2.2 Architekturmodelle

Die Klassifikation nach Warschko [54] berücksichtigt die logische Struktur des Speichersubsystem (verteilter oder gemeinsamer Speicher), die Definition des Adreßraumes (global

oder lokal) sowie die Kommunikationsstrukturen zwischen dem Prozessor und dem Speichersubsystem (implizite oder explizite Kommunikation). Nach dieser Klassifikation sind drei Architekturmodelle für Parallelrechner mit p Prozessoren zu erkennen:

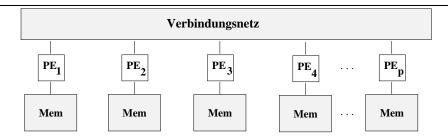

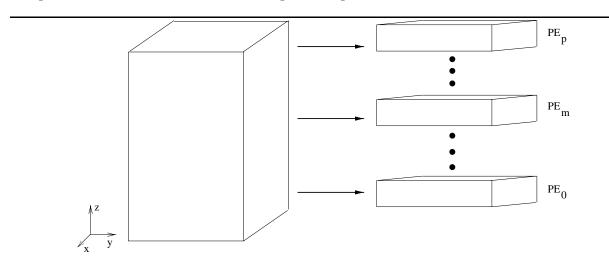

• Architekturen mit verteiltem Speicher (Nachrichtenkopplung, message passing systems, loosely coupled systems) — Sind durch einen physikalisch verteilten Speicher, p prozessor-lokale Adreßräume sowie explizite Kommunikationsoperationen, die nicht auf den Speicher anderer Prozessoren zugreifen können, gekennzeichnet (siehe Abbildung 2.1).

Abbildung 2.1: Architekturen mit verteiltem Speicher

• Architekturen mit gemeinsamem Adreßraum (shared address space) — Sind durch einen physikalisch verteilten Speicher, einen globalen Adreßraum sowie explizite Kommunikationsoperationen, die in Gegensatz zu den prozessoreigenen Speicherzugriffsoperationen auf den Speicher anderer Prozessoren zugreifen können, charakterisiert. Der direkte Zugriff auf den Speicher anderer Prozessoren geschieht mittels spezieller Kommunikationsoperationen, die den Schreib- bzw. Lesezugriff auf ein nichtlokales Speicherelement realisieren, wobei das Rendezvous-Prinzip, das bei Systemen mit verteiltem Speicher benötigt wird, entfällt (einseitige Kommunikation). Im Gegensatz zu Systemen mit gemeinsamem Speicher ist hier der Zugriff auf nicht-lokale Datenelemente über explizite Kommunikationsoperationen unter Angabe der Prozessornummer und der Speicherstelle innerhalb des Zielprozessors realisiert.

Für die Realisierung der vorliegenden Arbeit (siehe Kapitel 6) wurde ein Parallelrechner mit gemeinsamem Adreßraum als Zielarchitektur ausgewählt, nämlich die Cray T3E [41].

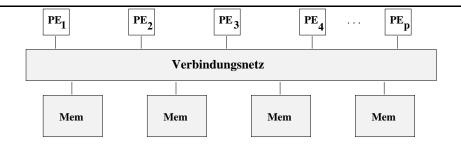

• Architekturen mit gemeinsamem Speicher (shared memory systems, tightly coupled systems) — Sind durch einen physikalisch gemeinsamen oder verteilten Speicher, einen globalen Adreßraum sowie implizite Kommunikationsoperationen charakterisiert, die über das Verbindungsnetzwerk (siehe Abbildung 2.2) transparent auf alle Speicherstellen zugreifen.

Das Besondere bei dieser Klassifikation im Vergleich zu der nach Hwang [29] ist die Einführung des Kriteriums Kommunikationsstrukturen, welches die eindeutige Unterscheidung zwischen Architekturen mit gemeinsamem Adreßraum und Architekturen mit gemeinsamem Speicher ermöglicht.

Abbildung 2.2: Architekturen mit gemeinsamem Speicher

## 2.3 Parallele Programmiermodelle

Die parallele Programmierung hat eine höhere Komplexität im Vergleich zur sequentiellen Programmierung: Die Zusammenarbeit einer großen Anzahl von Prozessoren muß geregelt und die Interaktion zwischen Prozessoren muß koordiniert werden. Verschiedene Modelle unterstützen die parallele Programmierung. Diese Modelle bzw. Abstraktionen unterscheiden sich in ihrer Flexibilität, dem Mechanismus zur Kommunikation zwischen Prozessen, der Unterstützung der Datenlokalität, Skalierbarkeit und Modularität [21]. Als nächstes werden einige dieser Modelle vorgestellt.

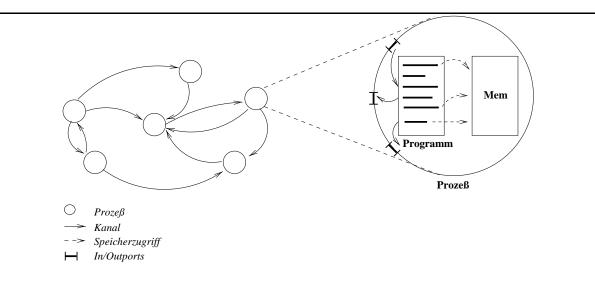

• Prozeß und Kanäle (task and channels) — Dieses Modell nimmt an, daß ein paralleles Programm aus mehreren simultan ausgeführten Prozessen besteht und daß die Anzahl der Prozesse in der Zeit variieren kann. Ein Prozeß besteht wiederum aus einem sequentiellen Programm und einem lokalen Speicher, wobei eine Menge von inports und outports die Schnittstelle zu der "Außenwelt" bildet. Neben dem Lesen vom lokalen Speicher bzw. dem Schreiben in den lokalen Speicher kann ein Prozeß noch vier weitere Grundoperationen durchführen: Nachrichten an seine outports senden, Nachrichten an seine inports empfangen, neue Prozesse erzeugen bzw. beenden. Outport-Inport-Paare können über die Kanäle verbunden werden. In Abbildung 2.3 sind Prozesse, Kanäle und Interaktionen zwischen Prozessen zu sehen.

Abbildung 2.3: Prozeß-Kanäle-Programmiermodell

Der wesentliche Unterschied von diesem Programmiermodell zur Nachrichtenkopplung ist, daß die Kommunikationsstruktur des parallelen Programmes hier viel genauer spezifiziert werden muß. Anstatt die Kommunikation zwischen Prozessen in verschiedenen Prozessoren zu spezifizieren, muß die Kommunikation zwischen Kanälen spezifiziert werden, wobei ein Prozeß in der Regel über mehrere Kanäle verfügt.

• Nachrichtenkopplung (message passing) — Dies ist wahrscheinlich das derzeit am meisten benutzte parallele Programmiermodell [21]. Bei einem nachrichtengekoppelten Programm, wie auch bei einem Prozeß-Kanäle-Programm, kapselt jeder erzeugte Prozeß seine lokalen Daten. Jeder Prozeß wird durch einen Namen identifiziert. Prozesse interagieren durch das Senden und Empfangen von Nachrichten, wobei die Prozeßnamen dabei benutzt werden. Im Vergleich zu dem Prozeß-Kanäle-Modell wird bei dem Nachrichtenkopplung eine Nachricht an einen Prozeß geschickt, anstatt eine Nachricht an einen Kanal. Dieses Programmiermodell stellt die geringsten Anforderungen an eine Parallelrechnerarchitektur [54], da die einzelnen Prozessoren vollkommen unabhängig voneinander arbeiten und über eine Kommunikationsschnittstelle verfügen, die es ihnen gestattet, mit anderen Prozessoren Nachrichten auszutauschen. Die Frage nach einer Speicherkonsistenz stellt sich hier nicht, da jeder Prozeß nur seinen eigenen Speicher kennt und verwalten muß.

Programmierumgebungen wie PVM (*Parallel Virtual Machine*) [15], MPI (*Message Passing Interface*) [8] oder P4 [6] sind typische Vertreter dieses parallelen Programmiermodells.

• Datenparallelität – Dieses parallele Programmiermodell nutzt die Parallelität aus, die auf der Ausführung der selben Operation synchron auf verschiedenen Elementen einer Datenstruktur basiert. Ein datenparalleles Programm besteht aus einer Menge solcher Operationen. Übersetzer für datenparallele Programme brauchen normalerweise vom Benutzer Information über die Datenverteilung auf die Prozessoren, d.h. der Benutzer muß festlegen, wie die Daten den Prozessoren zugeordnet werden.

Unterschiede zu der Nachrichtenkopplung sind die synchrone Semantik und der globale Adreßraum, wobei hier ebenfalls explizite Kommunikationsoperationen verwendet werden.

Typische Vertreter dieses Modells sind alle datenparallelen Programmiersprachen basierend auf Fortran oder C und deren Derivaten, wie z.B. HPF [32] und DPC(Data Parallel C) [26].

• Gemeinsame Variablen — Bei diesem Programmiermodell kommunizieren die verschiedenen Prozesse über einen gemeinsamen Adreßraum, woraus sie asynchron lesen bzw. in den sie asynchron schreiben. Die Speicherkonsistenz wird auf Architekturebene gewährleistet. Um den Zugriff auf den gemeinsamen Speicher zu verwalten, werden bestimmte Mechanismen benutzt, wie z.B. Schloßvariable (locks) und Semaphor. Dieses Modell vereinfacht die Entwicklung von Programmen, weil es keinen Bedarf an explizite Kommunikation zwischen Erzeuger und Verbraucher gibt.

Die Vertreter dieses Modells sind Programmierumgebungen (Betriebssystemerweiterungen und sog. *Thread*-Bibliotheken) für Multiprozessorsysteme verschiedenster Hersteller.

In der vorliegenden Arbeit werden sowohl das Nachrichtenkopplung- als auch das Datenparallelitäts-Programmiermodell eingesetzt. Bei dem System, das die Einstellung des Parallelitätsgrades realisiert, wird die Nachrichtenkopplung benutzt. Bei den Benchmarks werden Nachrichtenkopplung und Datenparallelität eingesetzt.

### 2.4 Charakterisierung paralleler Programme

In diesem Abschnitt werden Kennzahlen zur Charakterisierung paralleler Programme vorgestellt. Auf Basis dieser Kennzahlen können parallele Algorithmen bewertet und miteinander verglichen werden.

Die Definitionen der drei nachfolgend vorgestellten Kennzahlen stammen aus [21] und dienen als Grundlage für die Definition komplexerer Kennzahlen und Leistungsmodelle. Auf sie wird vielmals in dieser Arbeit zurückgegriffen.

Berechnungszeit ( $T_{comp}$ , computation time) — Die Berechnungszeit eines Algorithmus ist die Zeit, die für Rechenoperationen verwendet wird. Die Berechnungszeit ist von der Problemgröße abhängig. Falls es bei einem parallelen Algorithmus replizierte Aktivitäten gibt, ist die Berechnungszeit auch von der Anzahl der Prozesse oder Prozessoren abhängig, wobei  $T_{comp}$  in diese Situation der maximalen Zeit unter der beteiligten Prozessoren entspricht. Bei einem Parallelrechner, der aus Prozessoren unterschiedlicher Art besteht (sog. heterogener Parallelrechner), kann die Berechnungszeit auf den verschiedenen Prozessoren variieren.

Die Berechnungszeit hängt auch mit den Charakteristika und den Speichersysteme der Prozessoren zusammen. Änderungen an der Problemgröße bzw. an der Anzahl der Prozessoren können die Leistung des *Cache*-Speichers oder die Effektivität des Prozessorpipelining beeinträchtigen. Folge daraus ist, daß die totale Berechnungszeit eines Algorithmus, d.h. die über alle beteiligten Prozessoren kumulative Berechnungszeit, nicht unbedingt konstant bleibt, wenn sich die Anzahl der benutzten Prozessoren ändert.

Kommunikationszeit ( $T_{comm}$ , communication time) – Die Kommunikationszeit eines Algorithmus ist die Zeit, in der Nachrichten gesendet bzw. empfangen werden. Zwei Arten der Kommunikation können unterschieden werden: Die Intra-Prozessor- und die Inter-Prozessor-Kommunikation. Bei der ersten befinden sich die zwei Prozesse, die miteinander kommunizieren möchten, auf demselben Prozessor, wobei bei der zweiter Art der Kommunikation die Prozesse auf unterschiedlichen Prozessoren sind.<sup>1</sup>

Die Kosten, die bei einer Inter-Prozessor-Kommunikation zwischen zwei Prozessen zustande kommen, können durch zwei Parameter repräsentiert werden: Die Startzeit  $t_s$  (startup time) und die Übertragungszeit pro Wort  $t_w$  (transfer time per word). Die erste ist die Zeit, die für die Initialisierung der Kommunikation benötigt wird, während  $t_w$  die Bandbreite des Kommunikationsmediums ist, das die zu kommunizierenden Prozessoren verbindet. Die Übertragungszeit einer Nachricht, die aus L Worten besteht, beträgt:

$$T_{msg} = t_s + t_w \times L$$

Interessant ist, daß für einen sehr großen L nur  $t_w$  von Bedeutung ist, wobei für sehr kleine Nachrichten  $t_s$  dagegen eine dominierende Rolle spielt.

<sup>&</sup>lt;sup>1</sup>Wenn nur ein Prozeß pro Prozessor vorgesehen ist, handelt es sich immer um eine Inter-Prozessor-Kommunikation.

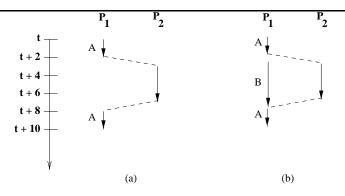

Bereitschaftszeit ( $T_{idle}$ ,  $idle\ time$ ) – Die Bereitschaftszeit ist die Zeit, während der ein Prozeß zwar bereit ist, aber nichts zu berechnen hat oder während die für die Berechnung benötigten Daten nicht verfügbar sind. Die erste Situation kann durch Techniken zur Lastbalancierung [47] vermieden werden. Bei der zweiten Situation befindet sich der Prozeß im Bereitschaftsmodus, weil die benötigten Daten für die Fortsetzung der Berechnung gerade geholt werden. Diese Bereitschaftszeit kann aber ausgenutzt werden, in dem die betroffenen Prozessoren andere Prozesse ausführen. Diese Technik wird Überlappung (overlapping) der Berechnung und Kommunikation gennant und ist in Abbildung 2.4 dargestellt. Die durchgehenden Linien repräsentieren Berechnungen, gestrichelte Linien Kommunikationsoperationen, sowie  $P_1$  und  $P_2$  Prozessoren. Sowohl in Abbildung 2.4(a) als auch in 2.4(b) erzeugt Prozessor  $P_1$  eine Anforderung an Prozessor  $P_2$  im Zeitpukt t+2 und empfängt eine Antwort im Zeitpukt t+8. In (a) hat  $P_1$  nichts mehr zu berechnen bis  $P_2$  ihm eine Nachricht schickt, in (b) dagegen wechselt  $P_1$  vom Prozeß A zu Prozeß B bis  $P_2$  ihm eine Nachricht geschickt hat. Diese Technik ist aber nur dann effektiv, wenn die Kosten, die mit dem Kontextwechsel zwischen Prozessen gebunden sind, nicht höher als die zu vermeidenden Bereitschaftszeit sind.

Abbildung 2.4: Überlappung von Berechnung und Kommunikationsoperation

**Ausführungszeit**  $(T, execution \ time)$  – Die Ausführungszeit eines parallelen Programmes mit p Prozessoren setzt sich aus den drei bereits vorgestellten Kennzahlen zusammen, wobei sie auf zwei verschiedene Arten definiert werden kann. Bei der ersten Art ist die Ausführungszeit T die Summe der Berechnungs-, der Kommunikations- und der Bereitschaftszeit an einem Prozessor j:

$$T = T_{comp}^j + T_{comm}^j + T_{idle}^j$$

Da die für einen Prozessor individuellen Zeitanteile oft nicht gemessen werden können, ist es sinnvoller, die Ausführungszeit in einer anderen Weise darzustellen. Hier wird die Ausführungszeit T als eine Summe verschiedener Zeitanteile über alle Prozessoren gebildet und diese durch die Anzahl der Prozessoren p dividiert:

$$T = \frac{1}{p} \left( \sum_{i=0}^{p-1} T_{comp}^i + \sum_{i=0}^{p-1} T_{comm}^i + \sum_{i=0}^{p-1} T_{idle}^i \right)$$

Parallelitätsgrad – Der Parallelitätsgrad eines Programmes gibt an, wieviel Parallelismus das Programm zu einem bestimmten Zeitpunkt anzubieten hat. In der vorliegenden Arbeit wird Parallelitätsgrad letztendlich als Synonym für die Anzahl von Prozessoren angewendet, die vom betrachteten Programm zu einem bestimmten Zeitpunkt in Anspruch genommen werden können.

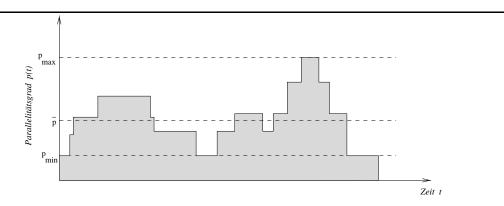

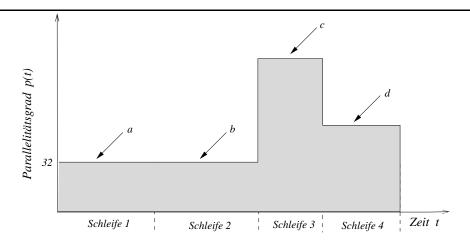

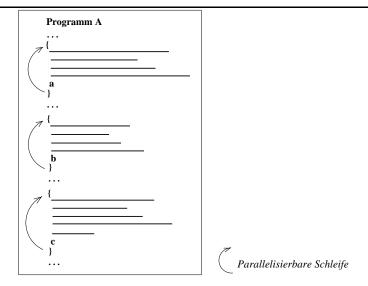

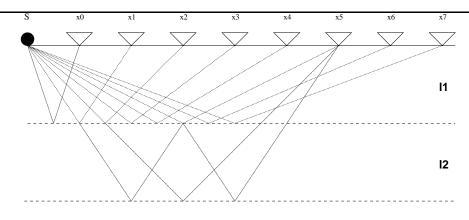

**Parallelitätsprofil** — Das Parallelitätsprofil eines Programmes ist der Verlauf des Parallelitätsgrades  $p_t$  über die Ausführungszeit t des Programmes. In Abbildung 2.5 ist zu sehen, daß der Parallelitätsgrad eines Programmes in der Zeit variiert, d.h. es gibt Phasen, in denen das Programm mehr Parallelismus anzubieten hat (z.B. bei  $p_{max}$ ), und andere Phasen, in denen weniger und/oder feinkörnigere parallele Aktivitäten vorhanden sind (z.B. bei  $p_{min}$ ). Das hat Kumar in [33] im Jahr 1988 gezeigt, wobei er ein Werkzeug mit dem Ziel entwickelt hat, den Parallelismus für FORTRAN-Programme zu messen. Der Parallelitätsprofil kann auch als die Anzahl der von einem Programm benutzten Prozessoren interpretiert werden [28], wenn beliebig viele Prozessoren zur Verfügung stehen.

Abbildung 2.5: Parallelitätsprofil eines Programmes

**Beschleunigung**  $(S_p, speed-up)$  – Die Beschleunigung stellt das Verhältnis zwischen der Ausführungszeit eines Programmes auf einem Prozessor und der auf p Prozessoren dar:

$$S_p = \frac{T_1}{T_p}$$

Die erzielte Beschleunigung sagt letztendlich, ob und wieviel sich die Ausführungszeit des Programmes reduziert bzw. vergrößert hat, wenn p Prozessoren statt einem Prozessor eingesetzt werden. Bei einer Beschleunigung von p auf p Prozessoren spricht man von einer linearen Beschleunigung, die wegen der Konkurrenz um gemeinsame Betriebsmittel, den zusätzlichen Kosten, die durch die Kommunikation zwischen Prozessoren entstehen, und der begrenzten Anzahl paralleler Aktivitäten, die das Programm anzubieten hat, nur schwer zu erreichen ist. Im Normalfall ist die Beschleunigung nicht linear und wächst auf Kosten der Effizienz.

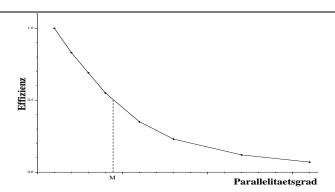

**Effizienz**  $(E_p, efficiency)$  – Die Effizienz stellt das Verhältnis zwischen der Beschleunigung, die mit dem Einsatz von p Prozessoren erreicht wurde, und der Prozessoranzahl dar:

$$E_p = \frac{S_p}{p}$$

Die erzielte Effizienz sagt, wie gut die p Prozessoren ausgelastet sind bzw. wie gut ein Algorithmus die Betriebsmittel eines Parallelrechners ausnutzen kann. Wenn nur ein Prozessor benutzt wird, beträgt die Effizienz 1. In dem Fall, daß die Effizienz bei 1 bleibt, wenn mehrere Prozessoren dazu kommen, ist die Beschleunigung linear.

Sowohl die Beschleunigung als auch die Effizienz können relativ oder absolut sein [21]. Sie sind relativ, wenn für ihre Erfassung die Ausführung des parallelen Algorithmus auf einem Prozessor berücksichtigt wird. Absolut sind sie, wenn der bestbekannte sequentielle Algorithmus eingesetzt wird.

Wie in [13] beschrieben, können die Beschleunigung und die Effizienz in der Praxis nicht gleichzeitig wachsen. Die Beschleunigung wird normalerweise auf Kosten der Effizienz gesteigert, da die gesamte Bereitschaftszeit mit der Anzahl der Prozessoren wächst. Das passiert wegen der Konkurrenz, der Kommunikation und der Programmstruktur, wie schon oben erläutert wurde.

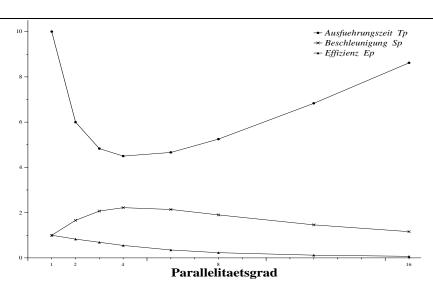

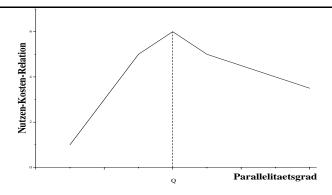

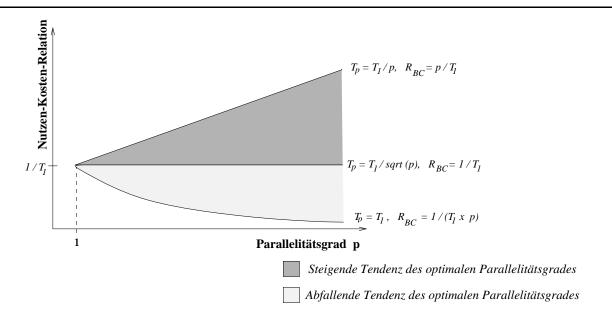

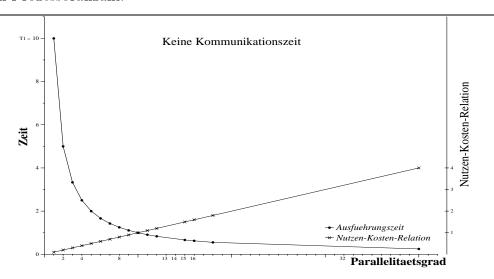

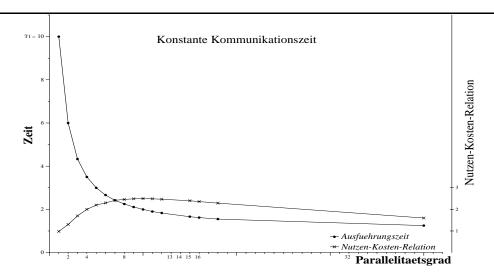

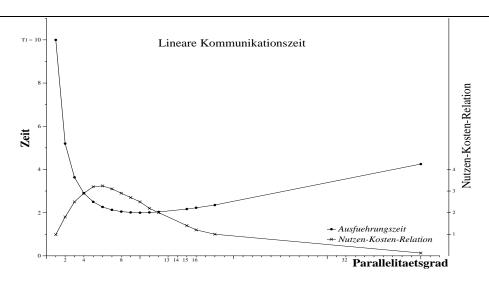

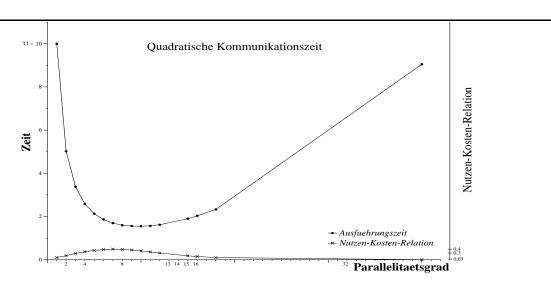

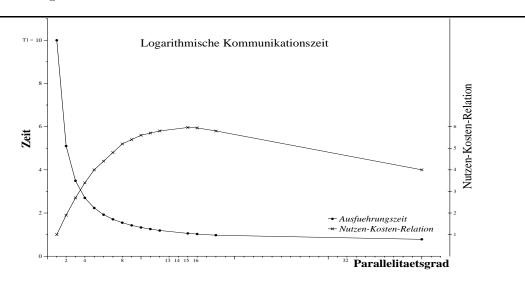

Kosten-Nutzen-Relation (cost-benefit relation) — Wenn man die Kurven  $T_p$  (Ausführungszeit) und  $E_p$  (Effizienz) in Abbildung 2.6 etwa im Bereich des Minimums der Ausführungszeitkurve betrachtet, stellt man fest, daß bei der Erhöhung des Parallelitätsgrades um 1 der Gewinn bezüglich der Ausführungszeit praktisch 0 ist, die Effizienz sich jedoch kontinuierlich verringert. Bei einem sehr geringen Parallelitätsgrad kann dagegen die Erhöhung um 1 eine erhebliche Reduktion der Ausführungszeit bewirken, während sich die Effizienz nicht in demselben Maß verschlechtert. Diese Beobachtung führt zu der Idee, die Kosten-Nutzen-Relation zu minimieren [28]. Diese Relation entsteht durch die Bildung des Quotienten aus den Kosten  $C_p$  und dem Nutzen  $S_p$ . Äquivalent dazu kann man auch die reziproke Nutzen-Kosten-Relation maximieren.

Abbildung 2.6: Zusammenhang zwischen  $S_p$ ,  $E_p$  und  $T_p$

$$C_p = T_p \times p$$

repräsentiert, wobei p die Anzahl der benutzten Prozessoren und  $T_p$  die Ausführungszeit des Programms auf p Prozessoren darstellt. Die Kosten resultieren aus dem Einsatz mehrerer Prozessoren, anstatt nur einem, für die Ausführung eines Programmes.

Der Nutzen  $S_p$  ist die Verbesserung oder Verschlechterung der Ausführungszeit durch die Benutzung mehrerer Prozessoren im Vergleich zu dem Einsatz von nur einem Prozessor, was letztendlich der Beschleunigung eines Programmes entspricht.

Die Kosten-Nutzen-Relation  $R_{CB}$  ist damit:

$$R_{CB} = \frac{T_p^2 \times p}{T_1}$$

Die Kennzahl Kosten-Nutzen-Relation beantwortet die Frage, inwiefern es sich lohnt, zusätzliche Prozessoren einem parallelen Programm zuzuordnen.

## 2.5 Modellierung der Leistung paralleler Programme

Hier werden drei Techniken präsentiert, die für die Charakterisierung der Leistung paralleler Programme benutzt werden.

#### 2.5.1 Das Amdahl'sche Gesetz

Nach dem Amdahl'schen Gesetz [1] besteht ein paralleler Algorithmus aus einem parallelen  $(\alpha)$  und einem sequentiellen  $(\beta)$  Teil. Die Beschleunigung (siehe Abschnitt 2.4), die durch den Algorithmus erzielt werden kann, ist wegen des sequentiellen Teils begrenzt. Die maximale Beschleunigung, die auf einem Parallelrechner erzielt werden kann, ist  $1/(1-\alpha)$ , wenn es keine Grenze für die Anzahl der Prozessoren gibt und  $T_1 = 1$ . Dise Erkenntnis wird im folgenden gezeigt.

Die Ausführungszeit  $T_p$  auf p Prozessoren setzt sich aus der Ausführungszeit des sequentiellen und des parallelen Teils zusammen:

$$T_p = (1 - \alpha) + \frac{\alpha}{p} \tag{2.1}$$

Wie im Abschnitt 2.4 erläutert, wird die Beschleunigung eines Programmes durch die folgende Formel repräsentiert:

$$S_p = \frac{T_1}{T_p} \tag{2.2}$$

Wenn die Prozessoranzahl unendlich wachsen kann, folgt aus (2.1) und (2.2):

$$S_p = \frac{1}{(1-\alpha) + \frac{\alpha}{p}} = \frac{1}{(1-\alpha)}$$

Wenn der sequentielle Teil eines Programmes z.B. 5% beträgt, beträgt die maximale Beschleunigung, die auf einem Parallelrechner erzielt werden kann, 20.

### 2.5.2 Asymptotische Analyse

Die Leistung eines parallelen Algorithmus kann auch durch eine asymptotische Analyse modelliert werden. Das Problem dabei ist, daß eine asymptotische Analyse Faktoren, die in vielen Fällen wichtig sein können, unberücksichtigt läßt. Die wirklichen Kosten eines Algorithmus für eine Problemgröße von N können z.B. 10N + NlogN betragen, wobei eine asymptotische Analyse die Kosten als NlogN modellieren würde. Dies wäre für mittelgroße bzw. große Problemgrößen realistisch, für kleine Problemgrößen aber nicht angebracht. Ein zweiter Nachteil ist, daß asymptotische Analyse auf idealisierten Maschinenmodellen basiert, die weit entfernt von realistischen Maschinen liegen können, wobei Aspekte wie Speicherhierarchie unberücksichtigt bleiben.

Eine asymptotische Analyse von parallelen Algorithmen basiert auf dem PRAM- und auf dem LogP-Modell, die im folgenden beschrieben werden.

Das PRAM-Modell — PRAM steht für Parallel Random Access Machine [20] und modelliert einen idealisierten speichergekoppelten Parallelrechner, der aus p identischen Prozessoren besteht. Die Prozessoren arbeiten synchron, greifen auf einem gemeinsamen Speicher zu und kommunizieren miteinander, ohne daß Kosten dabei entstehen. Außerdem enthalten alle Programmspeicher das gleiche Programm, führen dieselbe oder aber auch verschiedene Rechenoperationen gleichzeitig aus.

Das LogP-Modell — Hier wird ein nachrichtgekoppelter Parallelrechner, bei dem die Prozessoren unabhängig voneinander, vollkommen asynchron arbeiten, modelliert. Die Prozessoren kommunizieren über ein Netzwerk miteinander. Um die Kommunikation zu berücksichtigen, definiert das LogP-Modell [10] vier Kennzahlen, woraus der Name des Modells auch entsteht. Die Kennzahlen sind:

- Latenzzeit (*L*, *latency*) obere Schranke der Verzögerungszeit einer Kommunikationsoperation beim Austausch einer kleinen Nachricht (d.h. wenige Worte) zwischen zwei Knoten.

- Aufwand (o, overhead) Zeitbedarf für den Sende- bzw. Empfangsvorgang. Während dieser Zeit kann der sendende Prozessor keine weiteren Operationen ausführen.

- **Abstand** (g, gap) untere Schranke für die Zeit, die zwischen aufeinanderfolgenden Sende- bzw. Empfangsoperationen eingehalten werden muß.

- **Prozessoranzahl** (*P*, *processors*) Anzahl der Prozessoren, wobei jeder Prozessor über einen lokalen Speicher verfügen kann.

Das Modell hat einige Einschränkungen: Zu einem bestimmten Zeitpunkt sind maximal  $\lceil L/g \rceil P$  Nachrichten im Netz. Außerdem werden keine Konflikte im Verbindungsnetz berücksichtigt. Eine dritte Einschränkung ist die Tatsache, daß größere Nachrichten, bei denen die Latenzzeit von der Nachrichtenlänge abhängt, nicht beachtet werden.

Die asymptotische Analyse ist sicherlich relevant für die Entwicklung paralleler Programme. Die Ergebnisse einer asymptotischen Analyse müssen aber sorgfältig untersucht werden, indem die Rechnerarchitektur, für die die Ergebnisse erzielt wurden, die Koeffiziente, die angewendet werden müssen, die Problemgröße und die Prozessoranzahl klargestellt werden.

### 2.5.3 Planbare Algorithmen

W. Zimmermann [58] und W. Löwe [36] haben sich mit der Transformation paralleler Programme beschäftigt, die nach dem PRAM-Modell entwickelt wurden. Diese parallelen Programme sollen in Programme transformiert werden, die das oben beschriebenen LogP-Modell einsetzen. Das Ziel dabei ist, von einem theoretischen, abstrakten Programmiermodell zu einem Modell von praktischer Relevanz überzugehen, wobei die Ausführungszeiten der übersetzten Algorithmen auf der LogP-Maschine optimiert werden sollen. Die Transformationen beruhen auf einer Subklasse von PRAM-Programmen<sup>2</sup>, die durch einen planbaren Algorithmus gegeben werden können. Planbare Algorithmen sind Algorithmen, die sich durch ein eingabeunabhängiges Kommunikationsverhalten charakterisieren lassen, wobei das Verhalten nur vom Umfang der Eingabe abhängt, nicht jedoch von deren Inhalt<sup>3</sup>.

Diese Methode ermöglicht es, die maximale Ausführungszeit eines PRAM-Programmes auf verfügbaren Rechnern statisch zu berechnen. Das LogP-Modell ist ein geeigneter Kompromiß zwischen der bei der parallelen Programmierung erzielten Einfachheit und der Realitätsnähe bzw. praktischen Relevanz. Die o.g. Einschränkungen des LogP-Modells bleiben aber erhalten.

#### 2.5.4 Methode nach Foster

Ian Foster definiert in [21] eine neue Methode zur Modellierung der Leistung paralleler Algorithmen, die in der vorliegenden Arbeit bei der Validierung des mathematischen Modells, das den optimalen Parallelitätsgrades eines Programmes berechnet, benutzt wird. Foster behauptet, daß eine gute Leistungsmodellierung zwei Kriterien erfüllen muß: Erstens muß sie fähig sein, Beobachtungen bzw. Phänomene zu erklären, und zweitens muß sie künftig auftretende Situationen vorhersagen können, wobei von unwichtigen Details abstrahiert werden soll. Da sowohl das Amdahl'sche Gesetz als auch asymptotische Analyse das erste Kriterium nicht erfüllen, ist man auf der Suche nach einer vollständigeren Methode zur Modellierung der Leistung paralleler Algorithmen, die aber unbrauchbare Details nicht berücksichtigt.

Nach Foster wird die Ausführungszeit T eines Programmes in Abhängigkeit von der Problemgröße N, der Anzahl von Prozessoren p, der Anzahl von Prozessen U und anderer Charakteristika des Algorithmus sowie der Hardware definiert:

$$T = f(N, p, U, ...)$$

Das Ziel dabei ist, Formeln zu entwickeln, die die Ausführungszeit von N, p, usw. abhängend spezifizieren. Bei der Ermittlung der Ausführungszeit T werden die Berechnungs-, die Kommunikations- sowie die Bereitschaftszeit wie bei der im Abschnitt 2.4 definierten Charakterisierung paralleler Programme betrachtet. Nachteil dieser Methode ist, daß sie Aspekte wie Speicherhierarchie bei der Modellierung der Leistung paralleler Algorithmen unberücksichtigt läßt.

<sup>&</sup>lt;sup>2</sup>Aus praktischer Sicht besteht diese Subklasse aus einer großen Menge von PRAM-Programmen, z.B. FFT, Finite-Elemente-Methode, PDE-Löser, Matrix Multiplikation, usw.

<sup>&</sup>lt;sup>3</sup>Um PRAM-Programme in LogP-Programme zu transformieren, sind nach Zimmermann und Löwe drei Schritte erforderlich: Erstens muß die Anzahl der eingesetzten Prozessoren auf die Anzahl der zur Verfügung stehenden Prozessoren reduziert werden, zweitens muß das synchrone auf ein äquivalentes asynchrones Programm umgeschrieben werden. Drittens soll von einem verteilten statt einem gemeinsamen Speicher ausgegangen werden.

## 2.6 Entwurf paralleler Software

Für den Entwurf paralleler Software kann nicht ein einfaches Rezept vorgegeben werden, weil dabei viel an Kreativität gefordert ist. Dieser Prozeß kann aber durch eine spezifische Vorgehensweise unterstützt werden, indem der Weg von der Problemspezifikation bis hin zum parallelen Algorithmus beschrieben wird.

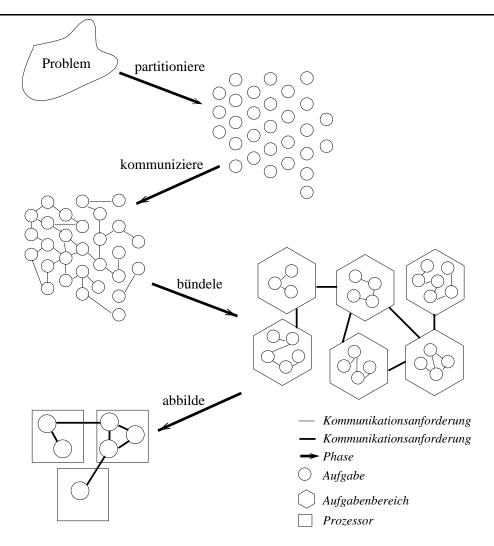

Foster [21] und Ungerer [52] strukturieren den Entwurfsprozeß paralleler Software in vier Phasen:

- Partitionierung (partitioning) Die Berechnungsschritte und die Daten, auf denen die Berechnungen ausgeführt werden, werden in kleine Aufgaben aufgeteilt. Praktische Erwägungen wie die Maschinenkonfiguration, die Anzahl der Prozessoren und die Struktur des Verbindungsnetzwerkes werden in dieser Phase ignoriert. Das Hauptziel ist, möglichst viel Parallelität zu entfalten.

- Kommunikation (communication) In dieser Phase werden Kommunikationsanforderungen festgelegt, und geeignete Kommunikationsstrukturen und Algorithmen definiert.

- **Bündelung** (agglomeration) Die Aufgaben und Kommunikationsstrukturen, die in den ersten zwei Phasen festgelegt wurden, werden bzgl. der Leistungsanforderungen und bzgl. Implementierungskosten evaluiert. Falls es notwendig ist, werden Aufgaben zu umfassenderen Aufgabenbereichen gebündelt, um die Leistung zu erhöhen oder die Entwicklungskosten zu sparen.

- **Abbildung** (mapping) Die Aufgaben werden den Prozessoren so zugeordnet, daß die konkurrierenden Ziele der maximalen Prozessorauslastung und der minimalen Kommunikationskosten miteinander in Einklang gebracht werden. Die Prozesorzuteilung kann statisch vom Übersetzer festgelegt oder dynamisch erst zur Laufzeit durch Anwendung von Lastbalancierungsalgorithmen vorgenommen werden.

Die verschiedenen Phasen sind in Abbildung 2.7 gezeigt, wobei das Ergebnis jeder Phase graphisch dargestellt ist. Die ersten zwei Phasen konzentrieren sich auf die Entfaltung von Parallelität sowie auf eine gute Skalierbarkeit und suchen einen Algorithmus mit diesen Eigenschaften. Die dritte und vierte Phasen behandeln die Lokalität und weitere leistungsorientierte Eigenschaften.

Die beschriebene Vorgehensweise bleibt für alle Zielprogrammstrukturen gleich. Beispielsweise wird bei einer SPMD(Single Programm Multiple Data)-Programmstruktur jedem Prozessor dieselbe Aufgabe zugeordnet.

Um die vorliegende Arbeit in den Entwurfsprozeß paralleler Software einzuordnen, wird von Fosters Phasenaufteilung Gebrauch gemacht. Die automatische Einstellung des Parallelitätsgrades ist Teil der Abbildungsphase, wobei hier eine dynamische und *iterative Abbildung* angewendet wird. Die Abbildung wird deswegen iterativ genannt, weil sie zur Laufzeit wiederholt durchgeführt wird, und zwar jedesmal, wenn sich der Parallelitätsgrad ändert.

Abbildung 2.7: Phasen des Entwurfsprozesses paralleler Programme

# Kapitel 3

# Stand der Forschung

Im folgenden wird der Stand der Forschung vorgestellt. Es werden Arbeiten aus drei Gebieten präsentiert und mit der vorliegenden Arbeit verglichen. Zuerst werden Beiträge zur Verbesserung der Auslastung von Parallelrechnern erläutert, danach Arbeiten, die durch die Bestimmung des Parallelitätsgrades zur Verbesserung der Leistung paralleler Programme beitragen. Als letztes werden diejenigen Beiträge vorgestellt, die eine Kombination von den zwei erstgenannten Gebieten berücksichtigen. Die vorliegende Arbeit ist dem letzten Gebiet zuzuordnen.

## 3.1 Verbesserung der Auslastung von Parallelrechnern

In diese Kategorie fallen alle Arbeiten, die sich mit Prozessorzuteilung beschäftigen und als Ziel eine Verbesserung der Auslastung des Gesamtsystems haben. Die Verwandschaft zu der voliegenden Arbeit besteht darin, daß auch die vorliegende Arbeit eine Verbesserung der Auslastung von Parallelrechnern als eines der Ziele hat. Trotz dieser Verwandschaft unterscheiden sich die Arbeiten im Lösungsansatz. Die vorliegende Arbeit befaßt sich nicht mit der Prozessorzuteilung in Parallelrechnern. Sie geht davon aus, daß die Prozessorzuteilung schon gelöst ist, aber daß der Bedarf an Prozessoren für verschiedene parallele Programme und ihre unterschiedliche Phasen (siehe Abbildung 2.5) nicht genau berücksichtigt, bzw. nicht überprüft wird. Außerdem betrachtet die vorliegende Arbeit die Einstellung des Parallelitätsgrades auf Programmebene anstatt auf Systemebene.

H.-U. Heiss an der Universität Karlsruhe klassifiziert in [28] die Prozessoraufteilung in statische, semi-dynamische und dynamische Aufteilung. Bei der statischen Aufteilung ist eine Menge paralleler Programme und die Funktionen vorgegeben, die die Beschleunigung der Programme wiedergeben. Auf Basis dieser Funktionen werden die Parallelitätsgrade der Programme berechnet und die Prozessoren für die gesamte Abarbeitungszeit fest aufgeteilt. Bei der semi-dynamischen Aufteilung ist eine dynamische Menge von Programmen gegeben, die jeweils einen konstanten Bedarf an Prozessoren haben (sog. statische Programme). Auch hier wird davon ausgegangen, daß der optimale Parallelitätsgrad eines jeden Programmes bekannt ist. Die dynamische Aufteilung erlaubt dagegen, daß Programme während ihrer Abarbeitung weitere Prozessoren allozieren bzw. freigeben. Das Verfahren setzt aber voraus, daß die Beschleunigungsfunktionen der Programme zur Verfügung stehen. Die Idee ist, demjenigen Programm inkrementell einen weiteren Prozessor zuzuteilen, dessen Beschleunigung dadurch am größten wird [43]. Damit wird schrittweise sichergestellt, daß im Hinblick auf den Durchsatz vom Betriebsmittel Prozessor bestmöglicher Gebrauch gemacht wird. Keine Implementierung der Technik in der letzten Kategorie ist bekannt.

Im Vergleich zur dynamischen Aufteilung wird der Parallelitätsgrad bei der vorliegenden Arbeit seitens des Programms, statt seitens des Betriebssystems, eingestellt. Außerdem wird der Parallelitätsgrad nicht nur nach der Beschleunigung eingestellt, sondern auch alternativ nach der Kosten-Nutzen-Relation und Effizienz.

M.S. Squillante, F. Wang und M. Papaefthymiou an dem Forschungszentrum T.J.Watson bzw. an der Yale Universität präsentieren in [50, 53, 49] die Technik gang scheduling (zuerst von Ousterhout [42] präsentiert), die die Betriebsmittel auf verteilten Systemen verwaltet. Gang scheduling kombiniert zwei Techniken: Erstens die Zeitanteil-Technik oder auch time sharing genannt, wodurch alle Prozessoren einem einzigen Programm für eine vorgegebene Zeit zugeordnet werden. Die zweite Technik ist die sog. Platzanteil-Technik oder auch space sharing genannt, bei der Programme mit der gleichen Anforderung an Prozessoren zu derselben Gruppe (gang) gehören. Jeder Gruppe wird eine Prozessorunterteilung (partition) für eine gegebene Zeitdauer zugeordnet. Wenn diese Zeit vorbei ist, geschieht ein Kontextwechsel für die Ausführung der nächsten Programmgruppe. Hier wird die Anzahl der den Programmen zugeteilten Prozessoren heuristisch festgelegt.

A. Gupta, A. Tucker und S. Urushibara beschreiben in [23] eine Studie, bei der die Leistung verschiedener Prozessozuteilungsstrategien durch Simulation untersucht wurde. Gang scheduling und process-control-Techniken (d.h. Techniken, die erlauben, daß Programme eine in der Zeit variierende Anzahl von Prozessen abhängig von der Anzahl der freien Prozessoren haben) zeigten die beste Leistung, wobei die Systemauslastung bei 71% lag. Kommerzielle Systeme wie CM-5 [34] und Intel Paragon [9] benutzen eine einfache gang-scheduling-Technik, die eine vorgegebene Prozessorunterteilung anwendet. Es gibt auch Variationen der gang-scheduling-Technik, die z.B. flexible Prozessorunterteilungen bzw. flexible Zeitanteile erlauben.

Bei der vorliegenden Arbeit wird der Parallelitätsgrad auf Basis von Messungen eingestellt, die zur Laufzeit stattfinden, anstatt ihn basierend auf Heuristiken statisch festzulegen. Außerdem ist bei der Arbeit von M. Squilante et al. eine Datenumverteilung trotz der Zielarchitektur, die über verteilten Speicher verfügt, nicht notwendig, weil sich der Parallelitätsgrad der Gruppe bis zum Ende der Ausführung der Programme nicht mehr ändert. Wie in Abschnitt 2.4 erwähnt, variiert der Parallelitätsgrad eines Programmes in der Zeit, was beim Einsatz dieser Methode zu einer Verschlechterung der Leistung von parallelen Programmen führen kann.

Die drei nächsten Arbeiten beschäftigen sich mit der dynamischen Zuordnung von Prozessoren zu Prozessen in Architekturen mit gemeinsamem Speicher und haben eine gute Auslastung des gesamten Systems als Ziel. Diese Arbeiten, die sich auf Architekturen der o.g. Art beschränken, berücksichtigen keine Datenumverteilung. Daraus folgt, daß diese Ansätze auf eine Architektur, die über verteilten Speicher verfügt, nicht anwendbar sind.

Der Prototyp Minos von C. McCann, R. Vaswani und J. Zahorjan an der Universität Washington [39] schlägt eine Strategie für die Prozessorzuordnung in Mehrprozessorsystemen mit gemeinsamem Speicher vor. Die Strategie ist dynamisch, weil sie die Zuordnung von Prozessoren zu Prozessen je nachdem ändert, wieviel Parallelismus jeder Prozeß während der Ausführungszeit anzubieten hat. Ein Prozeß enthält eine variierende Menge von Threads und signalisiert dem Scheduler-Thread, wieviele dieser Threads laufbereit sind. Anhand dieser Information wird die Anzahl der zu den Prozessen zugeordneten Prozessoren geändert, nämlich sie wird größer oder kleiner je nachdem, ob der Prozeß gerade zu viele oder zu wenig Prozessoren belegt. Der Prototyp ist in C++ geschrieben und läuft auf einer Sequent-Symmetry-Maschine mit 20 Prozessoren unter dem Betriebssystem DYNIX. Die Leistung der dynamischen Prozessorzuordnung wurde mit anderen Strategien

(Round-Robin Job [35], Equipartition [51]) verglichen und hat die besten Ergebnisse geliefert. *Minos* beschäftigt sich aber nicht mit der Frage, wie die Anzahl der Threads pro Prozeß bestimmt wird. Es wird einfach angenommen, daß jeder Prozeß dem Scheduler-Thread die richtige Anzahl von Threads mitteilt, ohne daß diese Information bei der Ausführungszeit überprüft wird.

Wesentliche Unterschiede zu der vorliegenden Arbeit sind die abweichende Zielarchitektur und die Art der Bestimmung des optimalen Parallelitätsgrades, die bei der vorliegenden Arbeit dynamisch und basierend auf realen Messungen stattfindet.

Die Technik LLPC (Loop-Level Process Control) von K. Yue und D. Lilja an der Universität Minnesota [56] unterstützt die Anpassung der Anzahl von Prozessoren, die eine Anwendung für die Ausführung der einzelnen parallelen Abschnitte benutzen darf. Diese Anpassung basiert auf der aktuellen Systemlast. Die Realisierung dieser Technik wurde durch die Einstellung der Anzahl der Threads erzielt, die jeder parallelen Schleife dynamisch zugeordnet wird. Die Kriterien für die Anpassung hängen aber nur von zwei Größen ab, nämlich der Systemlast und der Granularität der Schleife, die nur statisch abgeschätzt wird. Wenn die Systemlast hoch ist, reduziert LLPC die Kontextwechselrate, indem den Anwendungen nur eine geringe Anzahl von Prozessoren zugeordnet werden, statt ihnen die statisch bestimmte maximale Anzahl der Prozessoren zu erlauben. Die Messungen wurden auf einem Silicon-Graphics-Challenge-System unter dem Betriebssystem IRIX durchgeführt, wobei alle Beispielprogramme durch den PFA (Power Fortran Accelerator) parallelisiert wurden. Die Ergebnisse zeigen eine Verbesserung im Vergleich zu der Technik, die für die Prozessorzuordnung durch Silicon Graphics zur Verfügung steht (qang scheduling [50, 16]), und zu der Technik space sharing. Bei der Benchmark-Sammlung "Perfect Club" [4] konnte LLPC z.B. von 71% bis 85% der maximalen Beschleunigung in einer standalone-Ausführung der Programme erreichen.<sup>1</sup> Die Technik space sharing konnte dagegen nur gerade 56% der maximalen Beschleunigung erzielen. In einem anderen Testfall konnte LLPC von 47% bis 93% der maximalen Beschleunigung erreichen, während dieser Wert beim gang scheduling nur im Bereich von 28% bis 68% lag.

Neben der Zielarchitektur ist ein anderer Unterschied zu der vorliegenden Arbeit zu beobachten, nämlich daß die Einstellung des Parallelitätsgrades hier nur von der Systemlast und von einer statischen Abschätzung der Arbeit in der parallelen Schleife abhängt. Bei der vorliegenden Arbeit werden diese Parameter dynamisch kontrolliert, was die Methode auch auf irregulären Parallelismus anwendbar macht.

Die Arbeit von A. Tucker und A. Gupta an der Universität Stanford [51] schlägt einen Lösungsansatz für ein sehr spezifisches Problem vor, nämlich die Verschlechterung der Leistung von Programmen auf Multiprozessoren mit gemeinsamem Speicher, wenn die Anzahl der laufenden Prozesse viel größer ist als die Anzahl der zur Verfügung stehenden Prozesseren. Es handelt sich hier um eine Technik, die die Anzahl der laufenden Prozesse dynamisch kontrolliert, wobei die optimale Anzahl der Prozesse pro Programm durch eine zentrale Diensteinheit gegeben wird. Anhand dieser Information initialisieren bzw. beenden die Programme dynamisch Prozesse, um diese optimale Anzahl zu treffen. Diese Technik nimmt an, daß die Leistung paralleler Programme am besten ist, wenn die Gesamtanzahl der benutzten Prozesse gleich der Anzahl der zur Verfügung stehenden Prozessoren ist, wobei mehrere Programme gleichzeitig ausgeführt werden können. Im System können sowohl kontrollierte als auch nicht-kontrollierte Programme aktiv sein. Kontrollierte Programme

$<sup>^1</sup>$ Die standalone-Ausführung eines Programmes bezieht sich auf die Ausführung auf einem Rechner, auf dem kein weiteres Programm gleichzeitig läuft.

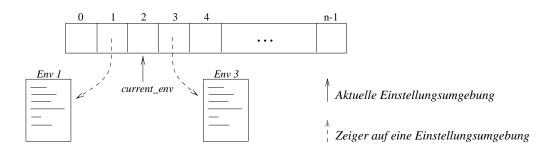

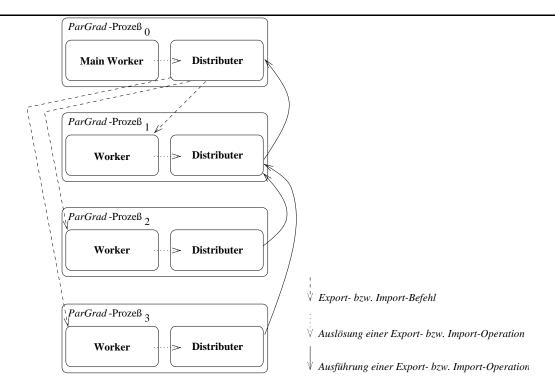

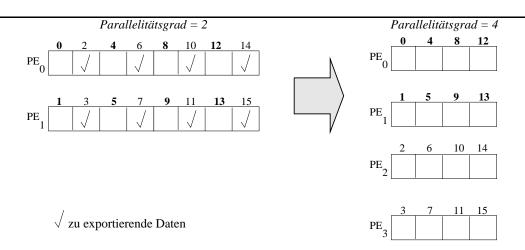

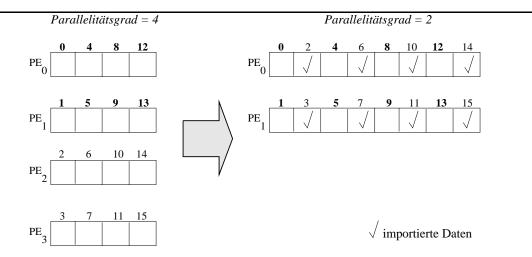

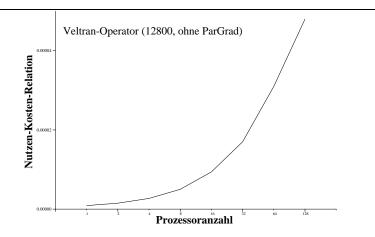

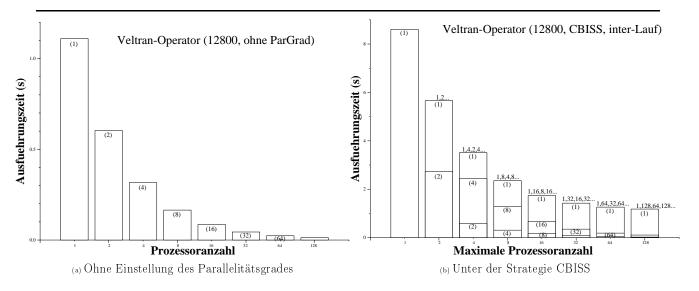

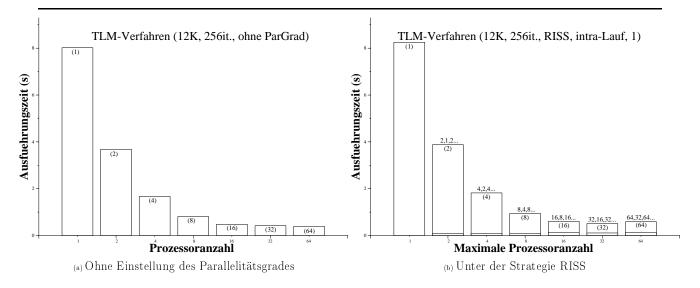

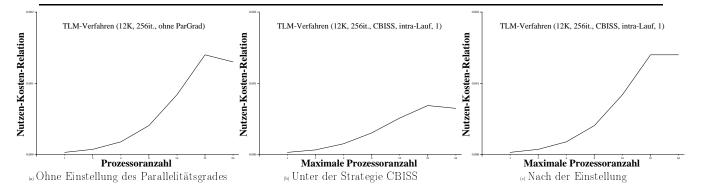

sind diejenigen, die unter der beschriebenen Technik laufen. Die Methode wurde auf einer Encore Multimax mit 16 Prozessoren implementiert. Die zentrale Diensteinheit kontrolliert regelmäßig die Gesamtanzahl der Prozesse im System, überprüft die Anzahl der Prozesse, die zu nicht kontrollierten Programmen gehören, subtrahiert diese von der gesamten Prozessoranzahl, um die Anzahl der Prozessoren festzulegen, die den kontrollierten Programmen zugeordnet werden können. Diese Prozessoren werden den Programmen unterteilt, darauf basierend wird die Anzahl der Prozesse pro Programm neu festgelegt. Bei der neu entstandenen Konfiguration ist die Gesamtanzahl der Prozesse gleich der Anzahl der Prozessoren im System. Für die vier analysierten Programme wächst die Beschleunigung bis zu 16 Prozessen für die im System kontrollierten und nicht-kontrollierten Programme, ohne daß der Mehraufwand der eingesetzten Technik signifikant wird. Dieses Verhalten war schon zu erwarten, da 16 Prozessoren zur Verfügung stehen. Ab 16 Prozessen ist die Beschleunigung für die kontrollierten Programme besser als für die nicht-kontrollierten, wobei dieser Unterschied größer wird, wenn die Gesamtanzahl der Prozesse wächst.